CONTROL DATA CORPORATION

MSL151 MAINTENANCE SOFTWARE

REFERENCE MANUAL

PART I TEST PROCEDURES & PART II TEST DESCRIPTIONS

IOU DETECTION/ISOLATION

CPU ISOLATION (FIS1)

MEMORY DETECTION ISOLATION (CMT1)

CDC COMPUTER SYSTEMS:

CYBER 170 MODELS 815 and 825

CYBER 180 MODELS 810 and 830

CONTROL DATA

CORPORATION

MSL151 MAINTENANCE SOFTWARE

REFERENCE MANUAL

PART I TEST PROCEDURES & PART II TEST DESCRIPTIONS

IOU DETECTION/ISOLATION

CPU ISOLATION (FIS1)

MEMORY DETECTION ISOLATION (CMT1)

CDCO COMPUTER SYSTEMS:

CYBER 170 MODELS 815 and 825

CYBER 180 MODELS 810 and 830

#### REVISION RECORD

REVISION

#### DESCRIPTION

- A Manual released. This manual reflects release level 137.

- 5-82

- B Manual revised; includes ECO PD 02900. This manual reflects

- 11-82 release level 143. FISI is supported at level 3.1. Model 815 has been added. Due to extensive changes, revision bars are not used. This edition obsoletes previous one.

- C Manual revised; includes ECO PD 02979. This manual reflects release 5-83 level 149. FIS1 is supported at level 4.0. The following pages are affected: vii/viii, ix, I-1-1, I-1-2, I-1-6 through I-1-9, I-1-14.

affected: vii/viii, ix, I-1-1, I-1-2, I-1-6 through I-1-9, I-1-14, I-1-23, I-1-25, I-2-4, I-2-10 through I-2-12, I-3-4, II-1-25 through II-1-33, II-2-8, II-2-9, II-2-15 through II-2-34, A-1 through A-3.

- D Manual revised; includes ECO PD 03063. This manual reflects release 11-83 level 156. FIS1 is supported at level 4.1. The following pages are

- affected: cover, title, ii, iii, iv, v, vii, viii, xi; in Part I:

Part I divider, 1-1, 1-2, 1-3, 1-5, 1-7, 1-13 through 1-17, 1-24, I-2

divider, 2-2, 2-3, 2-7, 2-10, 3-1, 3-2, 3-4 through 3-8, 3-10, 3-13,

3-15, 3-16, 3-22, 3-38, 3-50, 3-51, 3-52, and 3-54; in Part II: Part

II divider, 1-20, 1-22 through 1-35, II-2 divider, 2-5, 2-18, 2-19,

2-34, 3-11, 3-12, 3-14, appendix B divider, appendix C divider, and comment sheet.

- E Manual revised to include ECO PD 03109. FIS1 is supported at level

- 5-84 5.0. See List of Effective Pages for changed pages. This edition obsoletes all previous editions.

Publication no. 60469400

Revision Letters I, O, Q, S, X, and Z are not used

Address comments concerning this manual to:

Control Data Canada Toronto Publications 1855 Minnesota Court MISSISSAUGA, Ont., Canada L5N 1K7

or use Comment Sheet in the back of this manual

© 1982, 1983, 1984 by Control Data Corporation All Rights Reserved Printed in the United States of America

## LIST OF EFFECTIVE PAGES

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE     | REV      | PAGE         | REV | PAGE   | REV          | PAGE      | REV |

|----------|----------|--------------|-----|--------|--------------|-----------|-----|

| Cover    | B        | I-1-24       | B   | I-3-5  | R            | I-3-44    | A   |

| Title    | E        | I-1-25       | E   | I-3-6  | D            | I-3-45    | A   |

| 2        | B ·      | I-1-26       | E   | I-3-7  | D            | I-3-46    | A   |

| 3        | E        | I-1-27       | B   | I-3-8  | D            | I-3-47    | A   |

| 4        | E        | Divider      | B   | I-3-9  | A            | I-3-48    | A   |

| 5        | E        | I-2-1        | K   | I-3-10 | D            | I-3-49    | A   |

| 6        | E        | <b>I-2-2</b> | E   | I-3-11 | A            | I-3-50    | D   |

| 7        | E        | I-2-3        | E   | I-3-12 | A            | I-3-51    | D   |

| 8        | E        | I-2-4        | B   | I-3-13 | D            | I-3-52    | D   |

| 9/10     | E        | I-2-5        | E   | I-3-14 | E            | I-3-53    | A   |

| Divider  | E        | I-2-6        | E   | I-3-15 | D            | I-3-54    | D   |

| 1        | E        | I-2-7        | E   | I-3-16 | D            | I-3-55    | A   |

| 2        | R        | I-2-8        | E   | I-3-17 | A            | I-3-56    | A   |

| 3        | E        | I-2-9        | B   | I-3-18 | A            | I-3-57    | A   |

| Pt I Div | D        | I-2-10       | E   | I-3-19 | A.           | I-3-58    | A   |

| Divider  | A        | I-2-11       | E   | I-3-20 | A            | I-3-59    | A   |

| I-1-1    | E        | I-2-12       | E   | I-3-21 | В            | I-3-60    | A   |

| I-1-2    | E        | I-2-13       | E   | I-3-22 | D            | I-3-61    | A   |

| I-1-3    | E        | I-2-14       | E   | I-3-23 | A            | I-3-62    | · A |

| I-1-4    | В        | I-2-15       | B   | I-3-24 | B            | I-3-63    | A   |

| I-1-5    | E        | I-2-16       | E   | I-3-25 | B            | I-3-64    | A   |

| I-1-6    | E        | I-2-17       | B   | I-3-26 | A            | I-3-65    | A   |

| I-1-7    | B        | I-2-18       | B   | I-3-27 | A            | I-3-66    | A   |

| I-1-8    | C        | I-2-19       | E   | I-3-28 | A            | I-3-67    | A   |

| I-1-9    | С        | I-2-20       | E   | I-3-29 | . A          | I-3-68    | A   |

| I-1-10   | E        | I-2-21       | E   | I-3-30 | A            | I-3-69    | A   |

| I-1-11   | <b>B</b> | I-2-22       | E   | I-3-31 | A            | I-3-70    | A   |

| I-1-12   | A        | I-2-23       | E   | I-3-32 | , <b>A</b> , | I-3-71    | A   |

| I-1-13   | D        | I-2-24       | B   | I-3-33 | A            | I-3-72    | A   |

| I-1-14   | E        | I-2-25       | E   | I-3-34 | A            | I-3-73    | A   |

| I-1-15   | E        | I-2-26       | E   | I-3-35 | A            | I-3-74    | A   |

| I-1-16   | B        | I-2-27       | E   | I-3-36 | A            | I-3-75    | A   |

| I-1-17   | E        | I-2-28       | B   | I-3-37 | A            | I-3-76    | A   |

| I-1-18   | E        | I-2-29       | E   | I-3-38 | E            | I-3-77    | A   |

| I-1-19   | B        | Divider      | A   | I-3-39 | A            | I-3-78    | A   |

| I-1-20   | E        | I-3-1        | E   | I-3-40 | A            | I-3-79    | A   |

| I-1-21   | E        | I-3-2        | B   | I-3-41 | A            | I-3-80    | A   |

| I-1-22   | E        | I-3-3        | E   | I-3-42 | A            | I-3-81    | A   |

| I-1-23   | B        | I-3-4        | D   | I-3-43 | A            | Pt II Div | D   |

60469400 E

| PAGE          | REV        | PAGE    | REV     | PAGE    | REV        | PAGE | R <b>EV</b> |

|---------------|------------|---------|---------|---------|------------|------|-------------|

| Divider       | A          | II-2-8  | B       | II-3-19 | A          | -    |             |

| II-1-1        | A          | II-2-9  | E       | II-3-20 | A          |      |             |

| II-1-2        | A          | II-2-10 | E       | II-3-21 | A          |      |             |

| [I-1-3        | . <b>A</b> | II-2-11 | E       | II-3-22 | A          | •    |             |

| II-1-4        | A          | II-2-12 | B       | Divider | C          |      |             |

| II-1-5        | A          | II-2-13 | E       | A-1     | C          |      |             |

| I-1-6         | A          | II-2-14 | E       | A-2     | E          |      |             |

| I-1-7         | A          | II-2-15 | E       | A-3     | E          |      |             |

| I-1-8         | A          | II-2-16 | E       | A-4     | A          |      |             |

| I-1-9         | A          | II-2-17 | B       | A-5     | A          |      |             |

| I-1-11        | A          | II-2-18 | E       | Divider | E          |      |             |

| I-1-12        | A          | II-2-19 | E       | B-1     | A          |      |             |

| I-1-13        | . <b>A</b> | II-2-20 | E       | B-2     | A          |      |             |

| I-1-14        | À          | II-2-21 | · · · B | B-3     | A          |      |             |

| I-1-15        | . A        | II-2-22 | E       | B-4     | A          |      |             |

| I-1-16        | A          | II-2-23 | E       | B-5     | - <b>A</b> |      |             |

| I-1-17        | A          | II-2-24 | E       | B-6     | A          |      |             |

| I-1-18        | A          | II-2-25 | E       | B-7     | A          |      |             |

| I-1-19        | A          | II-2-26 | B       | B-8     | A          |      |             |

| I-1-20        | D          | II-2-27 | E       | B-9     | В          | •    |             |

| I-1-21        | A          | II-2-28 | E       | B-10    | В          |      |             |

| I-1-22        | D          | II-2-29 | E       | B-11    | A          |      |             |

| I-1-23        | D          | II-2-30 | E       | B-12    | В          |      |             |

| I-1-24        | Ø          | II-2-31 | E       | B-13    | В          |      |             |

| [-1-25        | D          | II-2-32 | E       | B-14    | A          |      |             |

| <b>I-1-26</b> | D          | II-2-33 | B       | B-15    | A          |      |             |

| T-1-27        | E          | II-2-34 | E       | B-16    | A          |      |             |

| <b>I-1-28</b> | E          | II-2-35 | R       | Divider | E          |      |             |

| I-1-29        | E          | II-2-36 | R       | C-1     | A          |      |             |

| I-1-30        | B          | II-2-37 | B       | C-2     | A          |      |             |

| I-1-31        | E          | •       |         | C-3     | A          |      |             |

| [-1-32        | E          | Divider | A       | C-4     | <b>A</b> . |      |             |

| I-1-33        | E          | II-3-1  | A       | C-5     | A          |      | •           |

| I-1-34        | E          | II-3-2  | A       | C-6     | A          |      |             |

| I-1-35        | E          | II-3-3  | A       | C-7     | A          |      |             |

| I-1-36        | B          | II-3-4  | A       | C-8     | A          |      |             |

| I-1-37        | E          | II-3-5  | A       | C-9     | A          |      |             |

| I-1-38        | K          | II-3-6  | A       | C-10    | A          |      |             |

| I-1-39        | E          | II-3-7  | A       | C-11    | A          |      |             |

| I-1-40        | B          | II-3-8  | · A     | C-12    | A          |      |             |

| [-1-41        | E          | II-3-9  | A       | Comment |            |      |             |

| [-1-42        | E          | II-3-10 | A       | Sheet   | E          |      |             |

| ivider        | E          | II-3-11 | D       |         |            |      |             |

| I-2-1         | E          | II-3-12 | D       |         |            |      |             |

| I-2-2         | E          | II-3-13 | A       |         |            |      |             |

| I-2-3         | A          | II-3-14 | D       |         |            |      |             |

| I-2-4         | A          | II-3-15 | A       |         |            |      |             |

| I-2-5         | D          | II-3-16 | A       |         |            |      |             |

| <b>[-2-6</b>  | E          | II-3-17 | A       |         |            |      |             |

| [-2-7         | E          | II-3-18 | A       |         |            |      |             |

### **PREFACE**

This manual describes the tests provided on the Maintenance Software Library (MSL 151) for use only on the CDC® CYBER 170 Model 815 and 825 and CDC® CYBER 180 Model 810 and 830 Computer Systems.

The manual is organized into two parts. Part I defines test procedures and part II describes program organization and content of each test. Within each part, the text of the manual is divided into the following sections:

- 1. IOU Detection/Isolation

- 2. CPU Isolation Tests (FIS1)

- 3. Memory (CMT1, CMI1)

### DISCLAIMER

This product is intended for use only as described in this document. Control Data cannot be responsible for the proper functioning of undescribed features or undefined parameters.

### RELATED PUBLICATIONS

| Control Data Publication                                                      | Publication Number |

|-------------------------------------------------------------------------------|--------------------|

| Maintenance Software Library (MSL15X) Reference<br>Manual                     | 60456530           |

| MSL 15% Model Independent Maintenance Software Reference Manual               | 60469390           |

| CYBER 170 Model 815 Logic Diagrams Hardware Maintenance Manual                | 60469640           |

| CYBER 170 Model 815 Multi-Level Block Diagrams<br>Hardware Maintenance Manual | 60469630           |

| CYBER 170 Model 815 and 825 Maintenance and Parts Hardware Maintenance Manual | 60469180           |

| CYBER 170 Model 825 Multi-Level Block Diagrams Hardware Maintenance Manual    | 60469210           |

| CYBER 170 Model 825 Logic Diagrams Hardware Maintenance Manual                | 60469220           |

| CYBER 170 Model 815 and 825 Hardware Reference Manual                         | 60469350           |

| CYBER 180 Model 810 and 830 Maintenance and Parts<br>Hardware Maintenance Manual | 60469500 |

|----------------------------------------------------------------------------------|----------|

| CYBER 180 Model 830 Multi-Level Block Diagrams<br>Hardware Maintenance Manual    | 60469480 |

| CYBER 180 Model 830 Logic Diagrams Hardware<br>Maintenance Manual                | 60469490 |

| CYBER 180 Model 810 Multi-Level Block Diagrams<br>Hardware Maintenance Manual    | 60469670 |

| CYBER 180 Model 810 Logic Diagrams Hardware Maintenance Manual                   | 60469660 |

## CONTENTS

|      | mand Buffers for Models 810, 815, 825<br>ck Margins | , and 830 | 1<br>1 |

|------|-----------------------------------------------------|-----------|--------|

|      | 1 CP Systems                                        |           | ī      |

|      |                                                     |           |        |

| PAR: | T 1 - TEST PROCEDURES                               |           |        |

|      | SECTION 1 - IOU DETECTION/ISOLATION                 | I TESTS   |        |

| 1    | Introduction                                        |           | I-1-1  |

| 2    | Requirements                                        |           | I-1-3  |

| 2.1  | Hardware                                            |           | I-1-3  |

| 2.2  | Software                                            |           | I-1-3  |

| 2.3  | Accessories                                         |           | I-1-4  |

| 2.4  | Characteristics                                     |           | I-1-4  |

| 3    | Operational Procedure                               |           | I-1-6  |

| 3.1  | Restrictions and User Cautions                      |           | I-1-6  |

| 3.2  | Loading Procedure                                   |           | I-1-6  |

| 3.3  | Parameters and Control Words                        |           | I-1-9  |

| 3.4  | Section Index                                       |           | I-1-1  |

| 4    | Operator Communication                              |           | I-1-1  |

| 4.1  | Displays                                            |           | I-1-1  |

| 4.2  | Operator Entries                                    |           | I-1-1  |

| 4.3  | Normal Messages                                     |           | I-1-1  |

| 4.4  | Error Messages                                      |           | I-1-1  |

| 4.5  | Stand Alone Mode                                    |           | I-1-2  |

|      | SECTION 2 - CPU FAULT ISOLATION TES                 | T (FIS1)  |        |

| 1    | Introduction                                        |           | I-2-1  |

| 1.1  | FIS1 on Systems with Dual CPUs                      |           | I-2-1  |

| 2    | Requirements                                        |           | I-2-3  |

| 2.1  | Hardware                                            |           | I-2-3  |

| 2.2  | Software                                            |           | I-2-4  |

| 2.3  | Accessories                                         |           | I-2-4  |

| 2.4  | Characteristics                                     |           | I-2-4  |

| 3    | Operational Procedure                               |           | I-2-4  |

| 3.1  | Restrictions and User Cautions                      |           | I-2-4  |

| 3.2  | Loading Procedure                                   |           | I-2-5  |

| 3.3  | Parameters and Control Words                        |           | I-2-5  |

| 3 A  | Section Index                                       | ,         | T 2 0  |

60469400 E

|            |                                                                                   | ~ 0 1/             |

|------------|-----------------------------------------------------------------------------------|--------------------|

| 4          | Operator Communication                                                            | I-2-14             |

| 4.1<br>4.2 | Displays                                                                          | I-2-14             |

| 4.2        | Operator Entries                                                                  | I-2-17<br>I-2-25   |

| 4.4        | Normal Messages<br>Brror Messages                                                 | I-2-25             |

| 4.4        | arror messages                                                                    | 1-2-23             |

|            | SECTION 3 - MEMORY FAULT DETECTION/ISOLATION TEST (CMT1/CMI1)                     |                    |

| 1          | Introduction                                                                      | 1-3-1              |

| 2          | Requirements                                                                      | I-3-1              |

| 2.1        | Hardware                                                                          | I-3-1              |

| 2.2        | Software                                                                          | I-3-2              |

| 2.3        | Accessories                                                                       | I-3-2              |

| 2.4        | Characteristics                                                                   | I-3-2              |

| 3          | Operational Procedure                                                             | I-3-3              |

| 3.1        | Restrictions and User Cautions                                                    | I-3-3              |

| 3.2        | Loading Procedure                                                                 | I-3-4              |

| 3.3        | Parameters and Control Words                                                      | I-3-4              |

| 3.4        | Section Index                                                                     | I-3-8              |

| 4          | Operator Communication                                                            | I-3-9              |

| 4.1        | Displays                                                                          | I-3-9              |

| 4.2        | Operator Entries                                                                  | I-3-11             |

| 4.3        | Normal Messages                                                                   | I-3-11             |

| 4.4        | Error Messages                                                                    | I-3-12             |

| PART       | II - TEST DESCRIPTIONS                                                            |                    |

|            | SECTION 1 - IOU DETECTION/ISOLATION TESTS                                         |                    |

| LDS        | - Long Deadstart Sequence - General                                               | 11-1-1             |

|            | - Extended Deadstart Sequence - General                                           | II-1-5             |

|            | - Quick Look Test - General                                                       | II-1-6             |

|            | - PP Memory Test 1 - General                                                      | II-1-7             |

|            | - Execution Unit Test - General                                                   | II-1-10            |

|            | - PP Memory Test 2 - General                                                      | II-1-12            |

|            | - Channel Test - General                                                          | II-1-15            |

|            | - Central Memory Access Test - General                                            | II-1-17            |

|            | - Maintenance Register Access Test - General                                      | II-1-19            |

|            | - Maintenance Register Test - General                                             | II-1-20            |

|            | - Maintenance Register Test - General                                             | II-1-22            |

|            | - Display Alignment Test - General                                                | II-1-25            |

|            | - Two Port Multiplexer Test - General<br>- Clock and Remote Access Test - General | II-1-27            |

| CIVIT      | Procedures for Remote Sections of CRA1                                            | II-1-30            |

| rxim       | - Two Port Multiplexer Test                                                       | II-1-31<br>II-1-34 |

|            | - IOU Isolation - General                                                         | II-1-34<br>II-1-37 |

|            |                                                                                   | **-1-3/            |

|         | SECTION 2 - CPO PROLIT ISOLATION | 1651 (F151)                  |             |

|---------|----------------------------------|------------------------------|-------------|

| Genera  | al                               |                              | 11-2-1      |

| Section | on Descriptions                  |                              | II-2-3      |

| Contro  | ol Store SECDED                  |                              | 11-2-35     |

|         | SECTION 3 - MEMORY FAULT DETECT  | ION/ISOLATION TEST (CMT1/CMI | <b>:1)</b>  |

| Genera  | <b>a1</b>                        |                              | II-3-1      |

| Section | on Descriptions                  |                              | II-3-3      |

|         |                                  | PPENDIXES                    |             |

| A .     | Glossary                         |                              | A-1         |

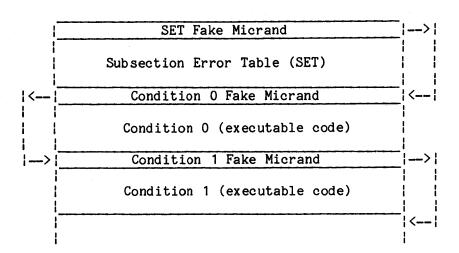

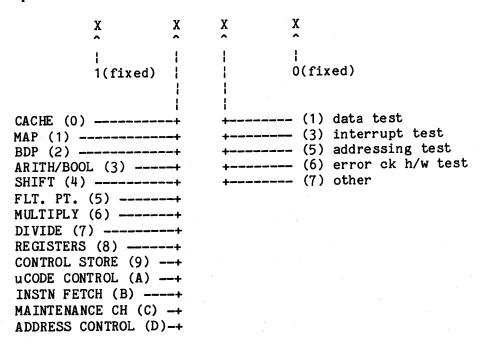

| B       | Fake Micrands                    |                              | B-1         |

| C       | FIS1 Subsection Error Table (    | SRT)                         | C-1         |

|         | The paper of the fact of         | <b></b>                      | <b>5</b> -1 |

|         |                                  | TABLES                       |             |

| I-1-1   | IOU Test Characteristics         |                              | I-1-5       |

| I-1-2   | Error Message Directory          |                              | I-1-25      |

|         |                                  | FIGURES                      |             |

| II-1-1  | Auto Answer Test Connections     |                              | II-1-31     |

|         | Auto Dial Test Connections       |                              | II-1-33     |

| II-1-3  | Monitor PP Map                   |                              | II-1-38     |

|         | Parity Error Buffer              |                              | II-1-39     |

|         | Invert Parity Error Buffer       |                              | II-1-39     |

| II-1-6  | Control and Data Error           |                              | II-1-40     |

| C-1     | Example of SET Source Code       |                              | C-2         |

| C-2     | Example of an Assembled SET T    | able                         | C-12        |

|  | * J |

|--|-----|

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

COMMAND BUFFERS

Clock Margins

Dual CP Systems

## COMMAND BUFFERS

#### **CLOCK MARGINS**

There are no more command buffers with a suffix of N or W for running narrow and wide clock margins. Most test command buffers contain an RJ command which executes one of three small command buffers called IOMARG, CMMARG, and CPMARG. These buffers set the wide/narrow margin bit for the respective subsystem using the CMSE CM command. The operator is required to select and run one of three other small command buffers called WIDE, NARROW, and NORMAL. Each of these initiates a PP program which modifies all three previously mentioned command buffers changing the W, N, or blank flag characters of the CM command.

After executing one (only) of the WIDE, NARROW, or NORMAL buffers with the CM command the operator may run one or more test command buffers. The RJ command in the test command buffers sets the subsystem margin bit (one only) appropriate to the test.

After testing with wide or narrow margins the operator must execute the NORMAL command buffer to reset the system and the IOMARG, CMMARG, and CPMARG buffers for normal (no margins) condition.

### DUAL CP SYSTEMS

Some tests for models 810, 815, 825, and 830 have more than one version and thus more than one command buffer. The majority of these command buffers are for instruction level tests as opposed to PP and microcode level tests. There are four classes of command buffers for the instruction level tests. They are identified by a suffix added to the end of the buffer name. The meaning of the suffixes is listed below:

No Suffix: For the only CP, single CP system

Suffix A: For CPO, dual CP system

Suffix B: For CP1, dual CP system

Suffix C: Concurrently for CPO and CP1, dual CP system

Suffix S: Sequentially for CPO and CP1, dual CP system

Buffers for single CP systems should not be run on dual CP systems and vice versa. Additional details are provided in the following paragraphs:

1) Command buffers without a suffix are functionally the same as those on previos releases although in many cases the nomenclature for individual commands has been changed to reflect the changes introduced in CMSE for dual CP operation.

- 2) Suffixes A and B distingush between two sets of command buffers for instruction level tests on dual CP systems. Command buffers with the suffix A are used to run the named test on CPO only and command buffers with the suffix B are used to run the named test on CPI only when you want only one CP to be active. The CMSE commands HK and CF in the buffers are directed to both CPs. This ensures that the selected CP will not be interfered with when the other CP is left active by the execution of the previous command buffer.

- 3) Suffix C indicates that the test runs concurrently on both CPs of a dual CP system.

- 4) Suffix S indicates that the test runs sequentially on dual CP systems. These buffers are for tests that operate under the control of the instruction test controller (ITC). The ITC runs each section of the test first in CPO and then in CP1. At any given time only one CP is active. Commands, listed on the test's parameter stop display, are provided to select or deselect either of the CPs if you want to test only one.

Current command buffer names are listed below.

# Command Buffer Names

| <b>\$\$</b> QLT10   |     | \$\$FT3G11B         |

|---------------------|-----|---------------------|

| \$\$PMT10           |     | \$\$FT3G21B         |

| <b>\$\$</b> EXT10   |     | <b>\$\$</b> FT3G31B |

| <b>\$\$PMU10</b>    |     | \$\$FT3FP1B         |

| <b>\$\$</b> CHD10   |     | \$\$FT3BD1B         |

| <b>\$\$CMA10</b>    |     | <b>\$\$</b> FT3S11B |

| <b>\$\$MRA10</b>    |     | <b>\$\$</b> FT3S21B |

| <b>\$\$M</b> RT10   |     | <b>\$\$</b> FCT51   |

| <b>\$\$</b> DST10   |     | <b>\$\$</b> FCT51S  |

| \$\$TPM10           |     | <b>\$\$</b> FCT91   |

| <b>\$\$CRA10</b>    |     | \$\$FCT91S          |

| <b>\$\$MUX10</b>    |     | \$\$EXCH1           |

| <b>\$\$</b> FII10   |     | \$\$EXCH1S          |

| <b>\$\$CMT10</b>    | •   | \$\$TRAP1           |

| <b>\$\$CMI10</b>    |     | \$\$TRAP1S          |

| <b>\$\$</b> FDS10   |     | \$\$EXC1            |

| <b>\$\$</b> FIS10   |     | \$\$EXClA           |

| \$\$CMEM1           |     | \$\$EXC1C           |

| \$\$CMEM1A          | • • | <b>\$\$RCT11</b>    |

| \$\$CMEM1B          |     | \$\$RCT11A          |

| \$\$FCT11           |     | \$\$RCT11B          |

| <b>\$\$</b> FCT118  |     | \$\$RCT21           |

| <b>\$\$FCT21</b>    |     | \$\$RCT21A          |

| \$\$FCT21A          |     | \$\$RCT21B          |

| \$\$FCT21B          |     | <b>\$\$</b> RCT111C |

| <b>\$\$</b> FCT31   |     | <b>\$\$</b> RCT221C |

| <b>\$\$</b> FT3G01  |     | <b>\$\$</b> RCT211C |

| <b>\$\$</b> FT3G11  |     | <b>\$\$</b> RCT121C |

| <b>\$\$</b> FT3G21  |     | \$\$C170CP          |

| \$\$FT3G31          |     | \$\$IOMARG          |

| <b>\$\$</b> FT3FP1  |     | \$\$CMMARG          |

| \$\$FT3BD1          |     | \$\$CPMARG          |

| \$\$FT3S11          |     | \$\$NORMAL          |

| \$\$FT3S21          |     | \$\$NARROW          |

| \$\$FCT31A          |     | \$\$WIDE            |

| \$\$FT3G01A         |     | \$\$BUILD           |

| \$\$FT3G11A         |     | \$\$CLEAR1          |

| <b>\$\$</b> FT3G21A |     | \$\$ABU             |

| \$\$FT3G31A         |     | \$\$DEMOTC1         |

| \$\$FT3FP1A         |     | \$\$DPALL           |

| \$\$FT3BD1A         |     | \$\$SNAP            |

| \$\$FT3S11A         |     | \$\$SNAPA           |

| \$\$FT3S21A         |     | \$\$SNAPB           |

| \$\$FCT31B          |     | \$\$0FA10           |

| <b>\$\$</b> FT3G01B |     | \$\$EME             |

|                     |     |                     |

## PART I

## TEST PROCEDURES

IOU DETECTION/ISOLATION TESTS

CPU FAULT ISOLATION TEST (FIS1)

MEMORY DETECTION/ISOLATION TEST (CMT1/CMI1)

SECTION I-1

IOU DETECTION/ISOLATION TESTS

|  |  |  | • | Z N                                   |

|--|--|--|---|---------------------------------------|

|  |  |  |   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   | y 'S                                  |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   | y 13                                  |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

|  |  |  |   |                                       |

### 1 INTRODUCTION

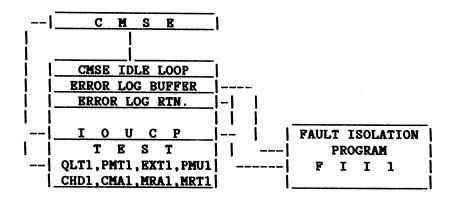

Maintenance software for the Models 810, 815, 825, and 830 IOUs consists of three major parts:

- Deadstart diagnostics

- Detection tests

- Isolation diagnostic

The deadstart diagnostics are Long Deadstart Sequence (LDS) and Extended Deadstart Sequence (EDS1). They assure that the IOU is stable enough to run the common maintenance software executive (CMSE). They are used only at deadstart time and test one barrel, some of the channels, and other hardware used by CMSE.

The detection tests are a series of programs which test each PP and channel in the IOU for correct functional operation. These tests also record errors such as differences between expected and actual (received) results, and generate internal codes which identify the area of the IOU under test when the error was detected.

#### The tests include:

QLT1 - quick look test

PMT1 - PP memory test 1

EXT1 - execution unit test

PMU1 - PP memory test 2

CHD1 - channel test

CMA1 - central memory access test

MRA1 - maintenance register access test

MRT1/- maintenance register test

MRTC

DST1 - display alignment test

TPM1 - two-port multiplexer test

CRA1 - clock and remote access test

MUX1 - two-port multiplexer test\*

The isolation diagnostic (FII1/FIIC) analyzes errors reported by the detection tests, and attempts to identify a group of logic paks which are likely to be causing the problem.

Bight of the detection tests listed above are used to verify functional operation and provide test results for the isolation diagnostic. These eight tests are listed below with brief descriptions of the hardware or functions checked by each test.

<sup>\*</sup> For use only with Models 815 and 825 that do not have FCO PD03122 installed; TPM1 and CRA1 cannot be run.

#### NOTE

Systems with element identification (EID) numbers 13 and 14 have all detection tests in common except for the maintenance register test (MRTC) and the isolation analyzer (FIIC).

## Test Name

### Purpose

Quick Look Test (QLT1)

Tests capability of each channel to handle one word of input and output data.

Execution Unit Test (EXT1)

Checks instruction execution in all PPs except those used by CMSE and the control program.

PP Memory Test 1 (PMT1)

Tests memory opertion in all barrels not being used by the input/output control program.

PP Memory Test 2 (PMU1)

Performs a more rigorous test on PP memories checked by PMT1.

Channel Test (CHD1)

Tests inter PP data transfer. Used two PPs to test each channel.

Central Memory Access Test (CMA1)

Tests data paths from PP memory to central memory, and from central memory to PP memory.

Maintenance Register Test (MRA1)

Checks access to the maintenance registers from all PPs. Also tests maintenance channel hardware interlock and interrupt priority circuits.

Maintenance Register Test (MRT1/MRTC)

Tests all IOU parity networks using the invert parity feature.

Each of the detection tests listed above may be loaded and executed separately using either CMSE keyboard commands or a command buffer. To perform isolation, run all eight tests in the sequence listed above. After the tests have finished executing, the isolation program may be executed to analyze the test results.

The four tests not used for isolation, DST1, TPM1, CRA1 and MUX1 provide basic checks of the CC545 display, the two port multiplexer, and calendar clock. These tests are run as needed, and are not part of the isolation sequence.

## 2 REQUIREMENTS

#### 2.1 HARDWARE

Equipment for which test is intended: Models 810, 815, 825, and 830 Computer Systems

## Target Configuration

10 PPs with 12 channels.

## Minimum Configuration

Five PPs with eight channels.

### Maximum Configuration

20 PPs with 24 channels.

Hardware Required to Run Tests:

LDS

Five PPs with associated channels LDS ROMs. Channel 17.

#### EDS1

five PPs with associated channels Channel 15 Channel 17 Maintenance software load (MSL) device

All other IOU tests

Five PPs with associated channels; CHD1 requires six PPs when run with CMSE. Channel 15

Channel 17

Maintenance software load (MSL) device

CC545 Display station

CMA1 uses 1 Megabyte of CM for its accessing tests

CC555 Display station for TPM1, CRA1, and MUX1 tests

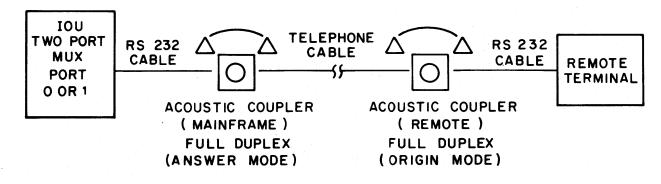

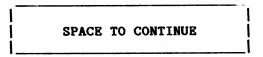

Acoustic coupler modem or equivalent for CRA1 test

### 2.2 SOFTWARE

LDS resides in ROM.

EDS1 requires the initial program load routine (IPL) which is a part of the common test initialization program (CTI). All other tests run under control of the common maintenance software executive (CMSE 15%). All interfaces to CMSE are handled by Input/Output Control Program (IOCP). For QLT1, PMT1,

MRA1, and MRT1, interfaces to IOCP are handled by the main PP test driver (MPDD). For EXT1, PMU1, and CMA1, interfaces are handled by the single PP driver (SPPD); and for CHD1, interfaces are handled by the double PP driver (DPPD).

## 2.3 ACCESSORIES

Use of DDLTs in the CYBER 170 Model 815 and 825 Maintenance and Parts Manual is recommended for LDS and EDS1.

## 2.4 CHARACTERISTICS

The following tables summarize characteristics of the various IOU tests. N/A equals not applicable.

## Long Deadstart Sequence (LDS)

| 1.  | Test name                            | LDS               |

|-----|--------------------------------------|-------------------|

| 2.  | Size (source)                        | 1K PP Words       |

| 3.  | Size (memory required for execution) | ROM               |

| 4.  | Code type                            | PP                |

| 5.  | Run time (default)                   | 14 Sec            |

| 6.  | Run time (quick look)                | N/A               |

| 7.  | Run time (all sections)              | N/A               |

| 8.  | Level of isolation                   | Detection         |

| 9.  | Off-line test                        | Yes               |

| 10. | Off-line system                      | N/A               |

| 11. | Where resident during execution      | ROM/Logical PP00  |

| 12. | Assembly language                    | 16 Bit PP Compass |

| 13. | Source code maintenance              | Update            |

| 14. | Uses maintenance channel             | Yes               |

## Extended Deadstart Sequence (EDS1)

| 1.  | Test name                            | EDS1              |

|-----|--------------------------------------|-------------------|

| 2.  | Size (source)                        | 2K PP Words       |

| 3.  | Size (memory required for execution) | 2K PP Words       |

| 4.  | Code type                            | PP                |

| 5.  | Run time (default)                   | 12 Sec            |

| 6.  | Run time (quick look)                | N/A               |

| 7.  | Run time (all sections)              | N/A               |

| 8.  | Level of isolation                   | Detection         |

| 9.  | Off-line test                        | Yes               |

| 10. | Off-line system                      | MSL 151           |

| 11. | Where resident during execution      | PP00              |

| 12. | Assembly language                    | 16 Bit PP Compass |

| 13. | Source code maintenance              | Update            |

| 14. | Uses maintenance channel             | Yes               |

# All Other IOU Tests

| 1.  | Test name                            | See table 1-1     |

|-----|--------------------------------------|-------------------|

| 2.  | Size (source)                        | See table 1-1     |

| 3.  | Size (memory required for execution) | See table 1-1     |

| 4.  | Code type                            | PP                |

| 5.  | Run time (default)                   | See table 1-1     |

| 6.  | Run time (quick look)                | See table 1-1     |

| 7.  | Run time (all sections)              | N/A               |

| 8.  | Level of isolation                   | Detection         |

| 9.  | Off-Line test                        | Yes               |

| 10. | Off-Line system                      | MSL 151           |

| 11. | Where resident during execution      | PP Resident       |

| 12. | Assembly language                    | 16 Bit PP Compass |

| 13. | Source code maintenance              | Update            |

| 14. | Uses maintenance channel             | Yes               |

TABLE I-1-1. IOU TEST CHARACTERISTICS

| Test Name | Size (Source) | Size (Execution)   | Run Time in Seconds |

|-----------|---------------|--------------------|---------------------|

| 1         |               |                    |                     |

| QLT1      | 5000 lines    | 4096 PP words      | 1 second/channel    |

| PMT1      | 5000 lines    | 4096 PP words      | 2 seconds/PP        |

| EXT1      | 5000 lines    | 4096 PP words      | 1 second            |

| PMU1      | 5000 lines    | 4096 PP words      | 7 seconds           |

| CHD1      | 5000 lines    | 4096 PP words      | 4 seconds/channel   |

| CMA1      | 5000 lines    | 4096 PP words      | 15 seconds          |

| MRA1      | 5000 lines    | 4096 PP words      | 1 second/PP         |

| MRT1      | 5000 lines    | 4096 PP words      | 2 seconds/PP        |

| MRTC      | 5000 lines    | 4096 PP words      | 2 seconds/PP        |

| DST1      | 5000 lines    | 4096 PP words      | 2 seconds*          |

| TPM1      | 5000 lines    | 4096 PP words      | 20 seconds*         |

| CRA1      | 5000 lines    | 4096 PP words      | 1 min, 20 seconds*  |

| MUX1      | 5000 lines    | 4096 PP words      | 1 min, 20 seconds*  |

| *Operato  | r interaction | requires an additi | onal 20 seconds     |

| or more.  |               |                    |                     |

# Fault Isolation (FII1)

| 1.  | Test name                            | FII1              |

|-----|--------------------------------------|-------------------|

| 2.  | Size (source)                        | 2K                |

| 3.  | Size (memory required for execution) | 4K                |

| 4.  | Code type                            | PP                |

| 5.  | Run time (default)                   | 1 second          |

| 6.  | Run time (quick look)                | N/A               |

| 7.  | Run time (all sections)              | N/A               |

| 8.  | Level of isolation                   | Isolation         |

| 9.  | Off-Line test                        | Yes               |

| 10. | Off-Line system                      | MSL 151           |

| 11. | Where resident during execution      | PP Memory         |

| 12. | Assembly language                    | 16 Bit PP Compass |

| 13. | Source code maintenance              | Update            |

| 14. | Uses maintenance channel             | Yes               |

## 3 OPERATIONAL PROCEDURES

#### 3.1 RESTRICTIONS AND USER CAUTIONS

The external channels, MSL device, and microprocessor deadstart program are assumed to be working. The long deadstart sequence (LDS) and extended deadstart sequence (EDS1) must run on the barrel from which the deadstart is performed.

#### NOTE

When running MRT1, all other activity must be stopped since MRT1 induces errors in the system.

The CRA1 test requires manual connection of telephones and modems if sections 4,5, and 6 are selected. See paragraph titled Procedures for Remote Sections of CRA1 in section II-1 of this manual.

## 3.2 LOADING PROCEDURE

### LDS

LDS is permanently resident in ROM and is activated by typing L as the microprocessor deadstart program input at the console.

### EDS1

If LDS completes execution, the common test and initialization package (CTI) automatically loads EDS1 from the selected MSL device if bit  $2^{0}$  of word 12 in the Deadstart program is set.

### IOU Detection Tests

To run tests in detection-only mode, do the following. To isolate faults see IOU Fault Isolation (FII1) below.

The IOU detection tests reside on the Maintenance Software Library. The operator uses CMSE commands for loading IOU tests under CMSE. Refer to the Maintenance Software Library (MSL 15%) Reference Manual for initial deadstart procedures.

A command buffer exists on the MSL 151 tape to facilitate loading and execution of each test. (Refer to the following table for the names of command buffers provided.) Before using a command buffer you may have to modify it for your system. Display the command buffer using the CMSE command buffer display commands or print the contents of the command buffer using procedures provided in the Command Buffer Maintenance section of the MSL 15X Reference Manual. Then modify the command buffer as directed by comments embedded in the command buffer. When you are satisfied that the command buffer is set up properly, enter a GO,xxxx command (where xxxx is the command buffer name) to execute it.

60469400 E

Modified command buffers can be saved on a back-up tape for future use. Refer to the Utilities section of the MSL 15% Reference Manual for procedures.

| <u>Test Name</u>                 | Command Buffer Nam |

|----------------------------------|--------------------|

| Quick look test                  | QLT10              |

| PP memory test 1                 | PMT10              |

| Execution unit test              | EXT10              |

| PP memory test 2                 | PMU10              |

| Channel test                     | CHD10              |

| Central memory access test       | CMA10              |

| Maintenance register access test | MRA10              |

| Maintenance register test        | MRT10              |

| Display alignment test           | DST10              |

| Two-port multiplexer test 1      | TPM10              |

| Clock and remote access test     | CRA10              |

| *Two port multiplexer test       | MUX10              |

#### NOTE

When the MRT10 test is selected, it reads the EID register. If the EID is 13 or 14, the test executes MRTC, if not, it executes MRT1.

## IOU Fault Isolation (FIII)

The IOU fault isolation program (FIII) resides on the Maintenance Software Library (MSL 151). Refer to the Maintenance Software Library (MSL 15X) Reference Manual for a description of how to set up and use command buffers.

Command buffer FII10 exists on the MSL 151 tape to facilitate loading and execution of each test. Before using this command buffer you may have to modify it for your system. Display the command buffer using the CMSE command buffer display commands or print the contents of the command buffer using procedures provided in the Command Buffer Maintenance section of the MSL 15X Reference Manual. Then modify the command buffer as directed by comments embedded in the command buffer. When you are satisfied that the command buffer is set up properly, enter a GO,FII10 command to execute all the IOU tests and conclude with fault isolation.

Modified command buffers can be saved on a back-up tape for future use. Refer to the Utilities section of the MSL 15X Reference Manual for procedures.

The automatic sequence runs the tests in order and then loads the fault isolation program FII1. You may start the sequence at any test manually, but the order of the sequence is retained.

#### NOTE

Run LDS and EDS1 before running fault isolation.

60469400 E I-1-7

<sup>\*</sup> For use only on Models 815 and 825 that do not have FCO PD03122 installed.

NOTE: Page I-1-8 is blank to compensate for deleted material.

## 3.3 PARAMETERS AND CONTROL WORDS

### 3.3.1 Parameters

The following parameter words are common to IOU tests except for LDS and EDS1. The bits in parameter words may be set and cleared using CMSE commands.

## NOTE

Multi-PP tests such as EXT1, PMU1, CHD1, and CMA1 are executed on a functional basis, i.e., all PPs receive the same copy of the test and execute it independently from all other PPs. Therefore parameters, control words, and messages are for the PP currently reporting at a given time.

| Word   | Address | Bit   | Default | <u>Definition</u>                                                                                       |

|--------|---------|-------|---------|---------------------------------------------------------------------------------------------------------|

| PARAMO | 122     | 48-63 | 134120  | Test control word, as defined<br>for CMSE. Refer to the MSL<br>15% Reference Manual.                    |

| PARAM1 | 123     | 61-63 | 000000  | Test control word as defined for CMSE. Refer to the MSL 15% Reference Manual.                           |

|        |         | 60    |         | Auto load mode. If this bit is set at the end of the test                                               |

|        |         |       |         | and neither the repeat or<br>stop at end of test is set,<br>CMSE will automatically call<br>a new test. |

|        |         | 59    |         | Repetitive restart mode. The test will be restarted automatically on the first detected error.          |

| PARAM2 | 124     | 48-63 | 000001  | Repeat test count as defined for CMSE.                                                                  |

| PARAM3 | 125     | 48-63 | 000000  | Not used.                                                                                               |

| PARAM4 | 126     | 48-63 | 000000  | Not used.                                                                                               |

| PARAM6              | 130        |                | 177777            | bit, if set, represents a selected section. Bit 63 in PARAM5 represents section number 0; bit 63 in PARAM6 represents section 16, etc.                                                    |

|---------------------|------------|----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAM7              | 131        | 48-63          | 177777,           | Subsection select bits.                                                                                                                                                                   |

| PARAM8<br>PARAM9    | 132<br>133 |                | 177777,<br>077777 | Each bit, if set, represents a selected subsection. Bit 63 in PARAM7 represents subsection 00; bit 63 in PARAM8 represents subsection 16; bit 63 in PARAM9 represents subsection 32, etc. |

| PARAM10,<br>PARAM11 | 134<br>135 | 48-63<br>48-54 | 000000,           | PP00 through PP31 (octal) flags. Each bit, if set, represents a selected PP number. Bit 63 in PARAM10 represents PP00; bit 63 in PARAM11 represents PP 208, etc.                          |

| PARAM12<br>PARAM13  | 136<br>137 | 48–63<br>52–63 | 000000,           | Channel 00 through 33 (octal) flags. Each bit, if set represents a selected channel. Bit 63 in PARAM12 represents channel 00; bit 63 in PARAM13 represents channel 208, etc.              |

|                     |            |                |                   | Bit 63 in PARAM12 represent<br>number of stop bits for TPM1<br>and CRA1 tests. When set it<br>selects 2 stop bits.                                                                        |

|                     |            |                |                   | Bits 62 and Bit 63 in PARAM13 represent parity select for TPM1 and CRA1 tests.                                                                                                            |

| PARAM14             | 140        | 48-63          | 000000            | Central memory size. Each bit represents a multiple of 131k, e.g., 0 equals 131k, 1 equals 262k, etc.                                                                                     |

The values of parameters 10 through 13 are automatically preset at the beginning of the test by reading the options installed register and setting the appropriate flags.

# 3.3.2 Control Words

The following control words are common to IOU tests except for LDS and EDS1.

| Word  | Address | <u>Definition</u>         |

|-------|---------|---------------------------|

| CWO   | 102     | Program name              |

| CW1   | 103     | Program name              |

| CW2   | 104     | Program type              |

| CW3   | 105     | Monitor ID word           |

| CW 4  | 106     | Error code number 1       |

| CW5   | 107     | Error code number 2       |

| CW6   | 110     | Pass counter              |

| CW7   | 111     | Current section number    |

| CW8   | 112     | Current subsection number |

| CW9   | 113     | Current condition number  |

| CW 10 | 114     | Current error count       |

| CW 11 | 115     | Controlling PP number     |

| CW 12 | 116     | Tested channel number     |

| CW13  | 117     | Tested PP number          |

| CW 14 | 120     | Random seed               |

| CW15  | 121     | Message builder address   |

## 3.4 SECTION INDEX

# LDS - Long Deadstart Sequence

LDS does not have selectable test sections.

## EDS1 - Extended Deadstart Sequence

EDS1 does not have selectable test sections.

## QLT1 - Quick Look Test

The test section number (converted to octal), represents the channel under test.

| Section |          | Ī    | Description  |      |         |      |

|---------|----------|------|--------------|------|---------|------|

| 00      | Test one | word | input/output | over | channel | 00.  |

| 01      | Test one | word | input/output | over | channel | 01.  |

| 02      | Test one | word | input/output | over | channel | 02.  |

| 03      | Test one | word | input/output | over | channel | 03.  |

| 04      |          |      | input/output |      |         |      |

| 05      |          |      | input/output |      |         |      |

| 06      |          |      | input/output |      |         |      |

| 07      |          |      | input/output |      |         |      |

| 08      |          |      | input/output |      |         |      |

| •       | •        |      |              |      |         |      |

| :       | •        |      | :            |      |         |      |

| 27      | Test one | word | input/output | over | channel | 338. |

|         |          |      |              |      |         |      |

# PMT1 - PP Memory Test 1

The test section number represents the PP under test.

| Section | Description       |  |  |

|---------|-------------------|--|--|

| 00      | Test PP00 memory. |  |  |

| 01      | Test PP01 memory. |  |  |

| 02      | Test PP02 memory. |  |  |

| 03      | Test PP03 memory. |  |  |

| 04      | Test PP04 memory. |  |  |

| 05      | Test PP05 memory. |  |  |

| 06      | Test PP06 memory. |  |  |

| 07      | Test PP07 memory. |  |  |

| 08      | Test PP10 memory. |  |  |

| 09      | Test PP11 memory. |  |  |

| 16      | Test PP20 memory. |  |  |

| :       | :                 |  |  |

| :       | :                 |  |  |

| 25      | Test PP31 memory. |  |  |

# EXT1 - Execution Unit Test

Sections are not selectable.

| Section | Tag      | <u>Description</u>                                                                       |

|---------|----------|------------------------------------------------------------------------------------------|

| 00      | UJNTST   | Test arithmetic unit and execution of 12-bit                                             |

| ,,01    | TEST 13X | operand instructions 00 through 57 (octal). Test arithmetic unit and execution of 16-bit |

| 02      | STSTEST  | operand instructions 1030 through 1057 (octal). Test execution of channel instructions.  |

# PMU1 - PP Memory Test 2

| Section | Description                                       |

|---------|---------------------------------------------------|

| 00      | Executes in lower half of memory and tests all    |

|         | memory except test core and direct cells used by  |

| + 1     | lower-half copy.                                  |

| 01      | Executes in upper half of memory and tests direct |

|         | cells and core used by lower-half copy.           |

# CHD1 - Channel Test

The number of sections selected (0-31) specifies the number of channels to be tested for one PP pair.

# CMA1 - Central Memory Access Test

| Section | Tag    | Description                                     |

|---------|--------|-------------------------------------------------|

| 00      | SEC00  | Tests relocation (R) register.                  |

| 01      | SEC 01 | Tests (R + A) - central memory address.         |

| 02      | CWDTST | Tests read/write CM with 60-bit single CM word. |

| 03 | ADRTST | Tests read/write addresses in CM with 60-bit single CM word. |

|----|--------|--------------------------------------------------------------|

| 04 | CWMTST | Tests read/write CM with 64-bit single CM word.              |

| 05 | CLDTST | Tests read/write block in CM with 60-bit CM word.            |

| 06 | CLMTST | Tests read/write block in CM with 64-bit CM word.            |

| 07 | RSLTST | Tests read and set lock.                                     |

| 80 | RCLTST | Tests read and clear lock.                                   |

| 09 | MIXTST | Tests read/write in mixed mode (60- and 64-bit CM            |

|    |        | word, single CM word and block).                             |

## MRA1 - Maintenance Register Access Test

Bach section (1-25) represents the PP number from which the MCH is accessed.

| <u>Section</u> | Tag   | <u>Description</u>                                                   |

|----------------|-------|----------------------------------------------------------------------|

| 00<br>01       | SEC00 | Tests the MCH interlock and PP priority. Tests MCH access from PPO1. |

| •              |       | •                                                                    |

| •              |       | •                                                                    |

| 25             |       | . PP31.                                                              |

## MRT1/MRTC - Maintenance Register Test

The test section number represents the PP number testing the MR.

| <u>Section</u> | <u>Description</u>     |

|----------------|------------------------|

| 00             | Test parity from PPO.  |

| 01             | Test parity from PP1.  |

| 02             | Test parity from PP2.  |

| 03             | Test parity from PP3.  |

| 04             | Test parity from PP4.  |

| 05             | Test parity from PP5.  |

| 06             | Test parity from PP6.  |

| 07             | Test parity from PP7.  |

| 08             | Test parity from PP10. |

| 09             | Test parity from PP11. |

| 16             | Test parity from PP20. |

| 17             | Test parity from PP21. |

| 18             | Test parity from PP22. |

| 19             | Test parity from PP23. |

| 20             | Test parity from PP24. |

| 21             | Test parity from PP25. |

| 22             | Test parity from PP26. |

| 23             | Test parity from PP27. |

| 24             | Test parity from PP30. |

| 25             | Test parity from PP31. |

# DST1 - Display Alignment Test

| <u>Section</u> | Tag   | <u>Description</u>                                   |

|----------------|-------|------------------------------------------------------|

| 00             | SEC00 | Tests dot function, CDC display code.                |

| 01             | SEC01 | Tests one character - full screen, CDC display code. |

| 02             | SEC02 | Tests full alphabet, CDC display code.               |

| 03             | SEC03 | Tests intensity, CDC display code.                   |

| 04             | SEC04 | Tests dot function, ASCII code.                      |

| 05             | SEC05 | Tests one character, full screen, ASCII code.        |

| 06             | SEC06 | Tests full alphabet, ASCII code.                     |

| 07             | SEC07 | Tests intensity, ASCII code.                         |

# <u>TPM1 - Two-Port Multiplexer Test</u>

| <u>Section</u> | Tag   | <u>Description</u>                                      |

|----------------|-------|---------------------------------------------------------|

| 00             | SEC00 | Tests the function response and FIFO.                   |

| 01             | SEC01 | Tests the connect function and DTR function.            |

| 02             | SEC02 | Tests the loop back feature.                            |

| 03             | SEC03 | Tests the master clear and disconnect function.         |

| 04             | SEC04 | Tests the X-Y positioning and parity detection feature. |

| 05             | SEC05 | Displays full alphanumeric characters.                  |

| 06             | SEC06 | Displays crossed diagonal lines.                        |

| 07             | SEC07 | Tests the input buffer and data in overrun bit.         |

| 08             | SEC08 | Tests the deadstart function.                           |

## CRA1 - Clock and Remote Access Test

| <u>Section</u> | Tag   | Description                                        |

|----------------|-------|----------------------------------------------------|

| 00             | SEC00 | Reads wall clock and displays date and time.       |

| 01             | SEC01 | Writes pattern to clock.                           |

| 02             | SEC02 | Tests the propagation of carry-through all stages. |

| 03             | SEC03 | Enters time and date to wall clock.                |

| *04            | SEC04 | Tests auto answer on port 0.                       |

| <b>*</b> 05    | SEC05 | Tests auto answer on port 1.                       |

| *06            | SEC06 | Tests auto dial out on port 1.                     |

<sup>\*</sup> These sections are only selected for Model 13 and 14.

# MUX1 - Two-Port Multiplexer Test\*

| <u>Section</u> | Tag   | <u>Description</u>                                                                             |

|----------------|-------|------------------------------------------------------------------------------------------------|

| 00             | SEC00 | Tests the response on function and FIFO.                                                       |

| 01             | SEC01 | Displays full screen dots and crossed diagnonal lines.                                         |

| 02             | SEC02 | Displays full screen of one character.                                                         |

| 03             | SEC03 | Displays all alphanumeric characters.                                                          |

| 04             | SEC04 | Displays blinking and reduce intensity messages.                                               |

| 05             | SEC05 | Subsection 0 reads clock and displays date and time. Subsection 1 writes pattern to the clock. |

| 06             | SEC06 | Subsection O checks propagation of carry through all stages. Subsection 1 writes to clock.     |

## FII1/FIIC - IOU Isolation Program

FII1/FIIC does not have selectable test sections.

60469400 E I-1-15

<sup>\*</sup> For use only on Models 815 and 825 that do not have FCO PD03122 installed.

#### 4 OPERATOR COMMUNICATION

LDS and EDS1 communicate errors via the deadstart microprocessor displays. All other IOU tests use standard CMSE commands and displays.

#### 4.1 DISPLAYS

All IOU tests, except LDS and EDS1 use the standard CMSE displays as described in the Maintenance Software Library (MSL 15%) Reference Manual.

Normal and error messages that appear in the test display area of the B display are described in sections 4.3 and 4.4 of this manual.

Refer to the section descriptions of DST1 and TPM1 for descriptions of special displays used by these tests.

#### 4.2 OPERATOR ENTRIES

All IOU tests except LDS and EDS1 use the standard CMSE keyboard commands (S, R, D, and space) as described in the Maintenance Software Library (MSL 15X) Reference Manual.

#### 4.3 NORMAL MESSAGES

## 4.3.1 <u>Detection Tests</u>

Normal messages displayed by the IOU detection tests (except for LDS and EDS1) in the test display area of the B display are of three types:

IMO - Standard informative message

IM1 - PP activity message

IM2 - Set parameter message

Refer to the test descriptions of DST1 and TPM1 for special messages displayed by these tests.

Except where noted, values are in octal.

#### NOTE

Multi-PP tests such as EXT1, PMU1, CHD1, and CMA1 are executed on a functional basis, i.e., all PPs receive the same copy of the test and execute it independently from all other PPs. Therefore parameters, control words, and messages are for the PP currently reporting at a given time.

# IMO - Standard Informative Message

The standard informative message displayed by IOU tests is shown below. The second informative message is used for TPM tests only.

| name | op | PCxxxx | Sxxxx | SBxxxx | Cxxxx | MPPxx | CHxx | TPPxx  | ١ |

|------|----|--------|-------|--------|-------|-------|------|--------|---|

| name | ор | PCxxxx | Sxxxx | SBxxxx | Cxxxx | MPPxx | CHxx | PORTXX | 1 |

#### where:

name Name of test (up to four-character mnemonic)

op Type of operation performed. Same as defined for CMSE. Refer to

Running Display, paragraph 4.1.1, section I-2 of this manual.

PCxxxx Pass count in decimal

SXXXX Current section number in decimal

SBXXXX Current subsection number in decimal

Cxxxx Current condition number in decimal

MPPxx IOU monitor PP number

CHxx Channel number

TPPxx Tested PP number

PORTxx Tested Port number

### IM1 - PP Activity Message

The format of the PP activity message displayed by all IOU tests except TPM and CRA in the test area of the B display is shown below.

| PP 00-xx 01-xx 02-xx 03-xx 04-xx 05-xx 06-xx 07-xx 10-xx 11-xx | 20-xx 21-xx 22-xx 23-xx 24-xx 25-xx 26-xx 27-xx 30-xx 31-xx |

Where xx is defined for each IOU test as follows:

QLT1, PMT1, MRA1 and MRT1 xx equals PP status:

L load mode

D dump mode

I idle mode

R PP running

H PP hung

EXT1, PMU1 and CMA1

xx equals lower two digits of pass count counter

CHD1

xx equals tested channel number

#### IM2 - Set Parameters Message

The following set parameters message is displayed only once at the beginning of each test. All parameter entries are in octal.

|   | *************************************** |     |        |        |       |     |

|---|-----------------------------------------|-----|--------|--------|-------|-----|

| ļ | <u>name</u> S                           | SET | PARAMS | PAxxxx | yy.mm | .dd |

where:

name

Name of test (up to four-character mnemonic)

SET PARAMS

Set parameters operation

PAxxxx

First word address for parameters

yy mm Year the test was assembled Month the test was assembled

dd Day the test was assembled

#### 4.3.2 Fault Isolation

In addition to the normal messages displayed by the IOU tests, FIII presents the following message upon completion of isolation.

# FISMO - Fault Isolation Message O

This message indicates that no errors were recorded or that no errors were detected:

#### 4.4 ERROR MESSAGES

# 4.4.1 LDS and EDS1 Error Stop Directory

When LDS stops, the contents of the P, Q, K, and A registers in the PP register displays identify the failure. Refer to the appropriate Maintenance and Parts Manual for LDS and EDS1 error stop directories.

# 4.4.2 DST1 Error Stops

If a CC555 is not available for running the DST1 test and DST1 detects an error, the test stops on a 0300 instruction. The contents of the monitor PP A register identify the failure as shown below. FFFF is the function code used.

| A Register Contents | Failure                         |

|---------------------|---------------------------------|

| OFFFF               | Initial channel 10 status error |

| 1FFFF               | Response on FAN error           |

| 2FFFF               | Response on FNC error           |

| 3 <b>FFF</b> F      | Dot timing error                |

| 4FFFF               | Coordinate timing error         |

| 5FFFF               | Character timing error          |

#### 4.4.3 TPM1 Error Stops

If a CC545 is not available for running the TPM1 test and TPM1 detects an error, the test stops on a 0300 instruction. The contents of the monitor PP A register identify the failure as shown below. FFFF is the function code used.

| A REGISTER CONTENTS | FAILURE                          |

|---------------------|----------------------------------|

| OFFFF               | Initial channel 15 status error. |

| 1FFFF               | Response on FAN error.           |

| 2FFFF               | Response on FNC error.           |

| 3FFFF               | Response on status request.      |

| 4FFFF               | FIFO status.                     |

| 5FFFF L             | Keyboard status error.           |

# 4.4.4 IOU Tests Error Messages

#### EMO - Error Message O

When an IOU test, other than LDS and EDS1, detects an error, it displays the following message immediately below the standard informative message:

Additional messages, described in the following paragraphs, are displayed beginning with the fifth display line.

# EM1 - Error Message 1

This message provides expected results. The data field displays from six to 30 digits or up to six characters.\*

# EM2 - Error Message 2

This message provides received results. The data field displays from six to 30 digits or up to six characters.\*

RCV=xxxxx xxxxxx xxxxx xxxxx

# EM3 - Error Message 3

This message provides the address at which the error was detected. The data field varies from six to 12 digits.

ADR=xxxxx xxxxxx

<sup>\*</sup>When this format is used to display a 64-bit CM word, the two most significant bits of each of the 18-bit groups are not used.

## EM4 - Error Message 4

This message shows that a parity error bit was detected in a fault register and identifies the byte and bit.

PE BIT Oxyz

where:

Identifies the fault register

x = 0 for fault register 1

x = 1 for fault register 2

y Byte n

Byte number in that register

Z.

Bit number in that byte

#### EM5 - Error Message 5

This message indicates a data or status error has been detected on channel xx. Error messages EM1 and EM2 are used in conjunction with EM5 to describe expected and received channel data or status.

CH XX ERR

Information displayed in expected and received messages (EM1 and EM2) regarding channel status includes:

| Message | Meaning                         |  |  |  |  |

|---------|---------------------------------|--|--|--|--|

| ACTIVE  | Channel active status           |  |  |  |  |

| INACT.  | Channel inactive status         |  |  |  |  |

| FULL    | Channel full status             |  |  |  |  |

| EMPTY   | Channel empty status            |  |  |  |  |

| FL.SET  | Channel flag set status         |  |  |  |  |

| FL.CLR  | Channel flag clear status       |  |  |  |  |

| EF.SET  | Channel error flag set status   |  |  |  |  |

| BF.CLR  | Channel error flag clear status |  |  |  |  |

#### EM6 - Error Message 6

This message indicates that a memory error has been detected in PPxx.

PPxx MEMORY ERROR

#### EM7 - Error Message 7

This message indicates that control over PPxx is lost. The current contents of the P, Q, K, and A registers are provided.

| PI | exx Hung |       |

|----|----------|-------|

| P  | XXXXXX   | XXXXX |

| Q  | XXXXXX   | XXXXX |

| K  | XXXXXX   | XXXXX |

| A  | XXXXXX   | XXXXX |

# EM8 - Error Message 8

This message indicates that an error was detected while reading the PPxx register identified by y. Register y can be P, Q, K, A, or R.

PPxx REG y ERR

## EM9 - Error Message 9

This message indicates that an error was detected during a Central Memory read/write operation.

CM ACCESS ERROR

Error message 10 is used in conjunction with EM9 to provide the contents of the R register.

## EM10 - Error Message 10

Error message 10 is used in conjunction with EM9 to provide the contents of the R register for a central memory access error.

R=xxxxx xxxxx

### EM11 - Error Message 11

This message indicates that an error in the parity network was detected for the test mode register.

PAR NTWRK ERR EC7=xxx TM=yyy yyy

MSK=bbb bbb bbb bbb bbb bbb bbb

OSB=aaa aaa aaa aaa aaa aaa aaa

where:

EC7=xxx

Value of byte 7 in the environment control register

тм=ууу ууу

Contents of test mode register

MSK=bbb ...

Contents of mask register

OSB=aaa ...

Contents of OS bounds register

# EM12 - Error Message 12

This message indicates that an error in the priority circuitry for MCH has been detected.

PP PRIORITY ERROR

## EM13 - Error Message 13

This message indicates that more than one PP has access to the MCH.

# MULTY PP ACCESS ERROR

## EM14 - Error Message 14

This message indicates that the response was bad on the issued function.

# MR FUNCTION RESPONSE ERROR F=xxxx

where: F=xxxx identifies the function error.

## EM15 - Error Message 15

This message indicates that a data error was detected using an echo function.

MR ECHO ERROR

## EM16 - Error Message 16

This message indicates that an error was detected in writing the maintenance register.

# MR WRITE ERROR RGTR=xxx

where: RGTR=xxx identifies the register as follows:

SSM status summary register

BID element ID register

OPT option installed register

MSK mask register

OSB OS bounds register

BCR environment control register

FS1 fault status 1 register

FS2 fault status 2 register

TMD test mode register

#### EM17 - Error Message 17

This message indicates that an error was detected while performing a read operation. xxx is as defined for EM16.

| l | MR | READ | ERROR | RGTR=xxx |  |

|---|----|------|-------|----------|--|

#### EM18 - Error Message 18

This message indicates that an error was detected while using the status summary function.

# MR STATUS SUMMARY ERROR

#### EM19 - Error Message 19

This message indicates that an error was detected on the initial channel identified by xx.

#### INITIAL CH XX STATUS ERROR

## EM20 - Error Message 20

This message indicates that the response on function xxxx issued by a FAN instruction is bad.

FUNCTION RESPONSE ERROR FAN=xxxx EXP=INACT RCV=ACTIVE

## EM21 - Error Message 21

This message indicates that the response on function xxxx issued by an FNC instruction is bad.

# FUNCTION RESPONSE ERROR FNC=xxxx

The expected and received messages for this error message are the same as shown in Error Message 5.

### EM22 - Error Message 22

This message indicates that a timing error was detected when the dot mode function was used. The expected response time is 6 microseconds.

DOT MODE TIMING ERROR T=6US

# EM23 - Error Message 23