# Burroughs B5500

Information

Processing Systems

REFERENCE MANUAL

# Burroughs B 5500 INFORMATION PROCESSING SYSTEMS REFERENCE MANUAL

Business Machines Group

Sales Technical Services

Systems Documentation

Contains material from 200-21014 and B 5000.55B, both COPYRIGHT® 1964 BURROUGHS CORPORATION

Burroughs B 5500 Information Processing System

#### TABLE OF CONTENTS

| ECTION | TITLE                                             | PAGE       |

|--------|---------------------------------------------------|------------|

|        | INTRODUCTION                                      | XXI        |

| 1      | SYSTEMS DESCRIPTION                               | 1-1        |

| -      | General                                           | 1-1        |

|        | Master Control Program                            | 1-1        |

|        | Description and Function of Major Units           | 1-1        |

|        | Central Control Unit                              | 1-4        |

|        | Memory Exchange                                   | 1-4        |

|        | I/O Exchange                                      | 1-4        |

|        | System Control                                    | 1-4        |

|        | Processors, A and B                               | 1-4        |

|        | Word Mode                                         | 1-4        |

|        | Character Mode                                    | 1-5        |

|        | Normal State                                      | 1-5        |

|        | Control State                                     | 1-5        |

|        |                                                   | 1-5        |

|        | Operators (instructions)                          | 1-5        |

|        | Clock                                             | 1-5        |

|        | Core Memory Module                                | 1-5<br>1-5 |

|        | Input/Output Control Unit                         | _          |

|        | I/O Channel                                       | 1-5        |

|        | Display and Distribution Unit                     | 1-5        |

|        | Information Flow Between Units                    | 1-6        |

|        | Memory Access                                     | 1-7        |

|        | Input/Output Access                               | 1-7        |

|        | Information Transfer                              | 1-7        |

|        | Communication Between Memory and Processor        | 1-7        |

|        | Memory Exchange                                   | 1-7        |

|        | Memory Addressing                                 | 1-7        |

|        | Communication Between Memory and I/O Control Unit |            |

|        | and I/O Device                                    | 1-8        |

|        | I/O Exchange                                      | 1-8        |

|        | Input                                             | 1-8        |

|        | Output                                            | 1-8        |

|        | Interrupt System                                  | 1-8        |

|        | Processor Independent Interrupts                  | 1-9        |

|        | Processor Dependent Interrupts                    | 1-9        |

|        | Interrupt Handling                                | 1-10       |

| 2      | DATA REPRESENTATION                               | 2-1        |

| •      | General                                           | 2-1        |

|        | Binary Notation                                   | 2-1        |

|        | Octal Notation                                    | 2-2        |

|        | Number Conversion                                 | 2-3        |

|        | Binary to Decimal Conversion                      | 2-3        |

|        |                                                   | 2-3<br>2-3 |

|        | Integral                                          | 2-3<br>2-3 |

|        | Fractional                                        |            |

|        | Decimal to Binary Conversion                      | 2-4<br>2-4 |

|        | Integral                                          |            |

|        | Fractional                                        | 2-4        |

| ECHON | TITLE                                         | PAGE |

|-------|-----------------------------------------------|------|

| 2     | Decimal to Octal Conversion                   | 2-5  |

|       | Integral                                      | 2-5  |

|       | Fractional                                    | 2-5  |

|       | Octal to Decimal Conversion                   | 2-5  |

|       | Octade                                        | 2-5  |

|       | Integral                                      | 2-6  |

|       | Fractional                                    | 2-6  |

|       | Binary Code Decimal (BCD)                     | 2-7  |

|       | Data Types and Physical Layout                | 2-7  |

|       | Characters                                    | 2-7  |

|       | Operands                                      | 2-7  |

|       | Numeric Operands (Numbers)                    | 2-7  |

|       | Logical Operands                              | 2-8  |

| 3     | POLISH NOTATION AND STACK                     | 3-1  |

|       | General                                       | 3-1  |

|       | Polish Notation                               | 3-1  |

|       | Polish String                                 | 3-1  |

|       | General Rules for Generation of Polish String | 3-1  |

|       | Rule for Evaluating Polish String             | 3-2  |

|       | Compilation Using Polish Notation             | 3-3  |

|       | Stack Concept Description                     | 3-3  |

|       | Program Reference Table (PRT)                 | 3-3  |

|       | Relative Addressing                           | 3-3  |

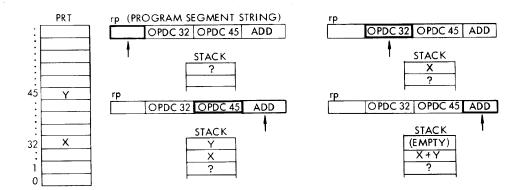

|       | Simple Stack Operation                        | 3-4  |

|       | Program Segment String Syllables              | 3-4  |

|       | Operand Call Syllable                         | 3-4  |

|       | Descriptor Call Syllable                      | 3-5  |

|       | Literal Syllable                              | 3-5  |

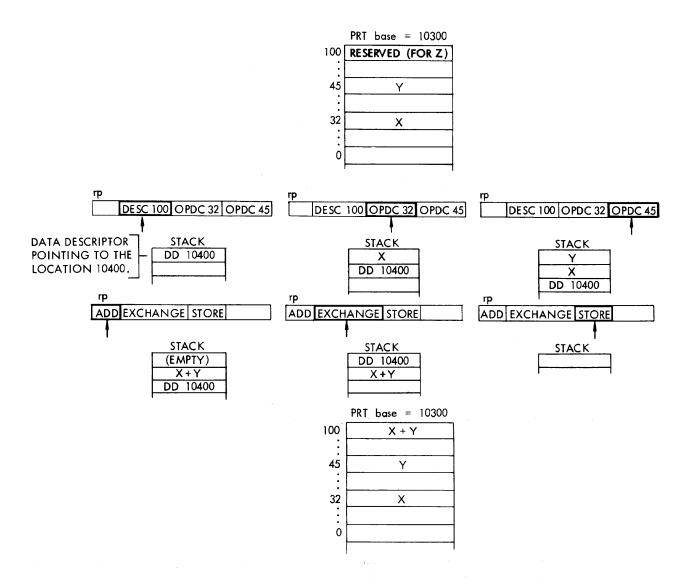

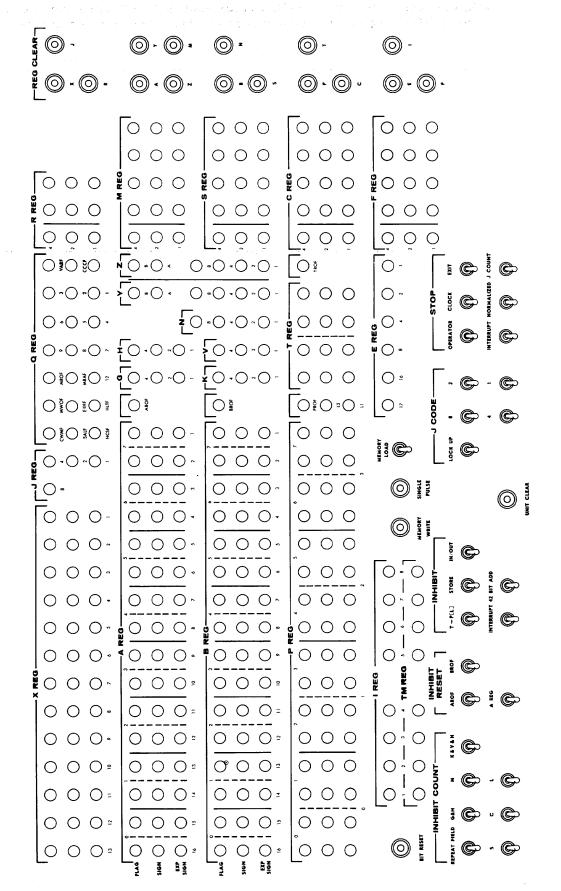

|       | Stack Area Description                        | 3-5  |

|       | Stack Location                                | 3-5  |

|       | Stack Register (A, B, S)                      | 3-5  |

|       | Top of Stack                                  | 3-6  |

|       | Stack Adjustment                              | 3-6  |

|       | Relative Addressing in Stack (F Register)     | 3-7  |

|       | Stack in Operation                            | 3-7  |

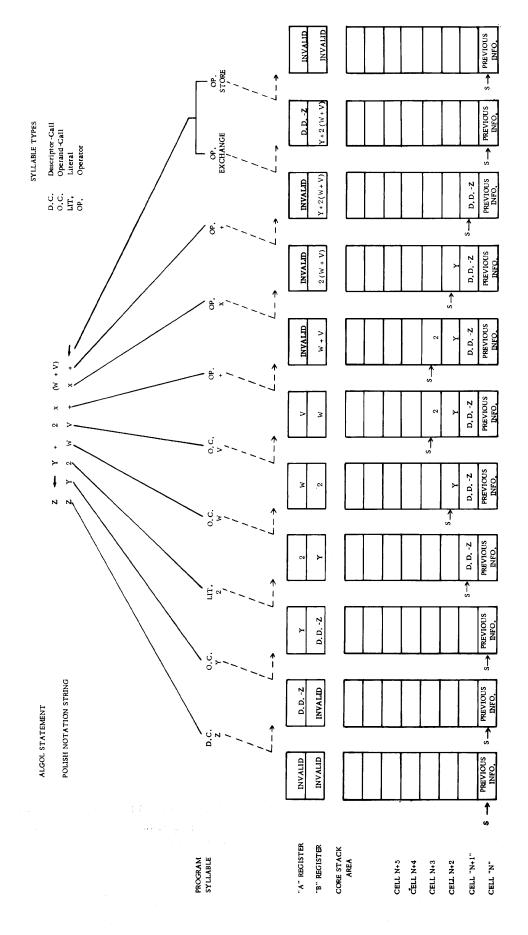

| 4     | MAJOR REGISTERS AND CONTROL FLIP FLOPS        | 4-1  |

|       | General                                       | 4-1  |

|       | Processor                                     | 4-1  |

|       | Registers and Flip Flops                      | 4-1  |

|       | A Register                                    | 4-1  |

|       | B Register                                    | 4-1  |

|       | AROF                                          | 4-1  |

|       | BROF                                          | 4-1  |

|       | Y Register                                    | 4-1  |

|       | Z Register                                    | 4-1  |

|       | G Register                                    | 4-1  |

|       | K Register                                    | 4-1  |

|       | H Register                                    | 4-2  |

|       | V Register                                    | 4-2  |

|       | N Register                                    | 4-2  |

| SECTION | TITLE                                     | PAGE       |

|---------|-------------------------------------------|------------|

| 4       | X Register                                | 4-2        |

|         | M Register                                | 4-2        |

|         | S Register                                | 4-2        |

|         | R Register                                | 4-2        |

|         | F Register                                | 4-2        |

|         | E Register                                | 4-2        |

|         | P Register                                | 4-2        |

|         | T Register                                | 4-2        |

|         | C Register                                | 4-2        |

|         | L Register                                | 4-2        |

|         | TROF                                      | 4-3        |

|         | PROF                                      | 4-3        |

|         | NCSF                                      | 4-3        |

|         | SALF                                      | 4-3        |

|         | CWMF                                      | 4-3        |

|         | HLTF                                      | 4-3        |

| -       | MSFF                                      | 4-3        |

|         | Q Register                                | 4-3        |

|         | I Register                                | 4-3        |

|         |                                           | 4-3        |

|         | J Register                                | 4-3<br>4-3 |

|         |                                           | 4-3<br>4-3 |

|         | Register Display                          | 4-3<br>4-3 |

|         | Program Syllable Access                   | 4-3<br>4-4 |

|         | Information Access                        | 4-4        |

|         | E Register                                | 4-4<br>4-4 |

|         | Processor Interrupt                       |            |

|         | I Register                                | 4-4        |

|         | Description of Interrupt Control          | 4-7        |

|         | Detecting and Processing                  | 4-7        |

|         | Categories                                | 4-7        |

|         | Priorities                                | 4-7        |

|         | External Interrupt Flip Flops             | 4-7        |

|         | Interrupt Address Register                | 4-9        |

|         | Real Time Clock                           | 4-9        |

|         | Halt Processor 2 Flip Flop                | 4-9        |

|         | Commence Timing and Load Flip Flops       | 4-11       |

|         | Core Memory Module Register               | 4-11       |

|         | I/O Control Unit Registers and Flip Flops | 4-11       |

|         | Registers and Flip Flops                  | 4-11       |

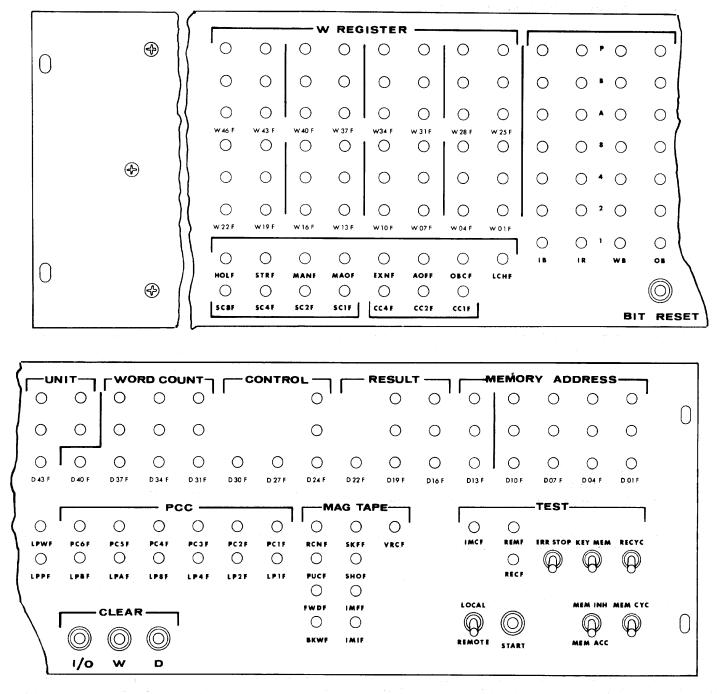

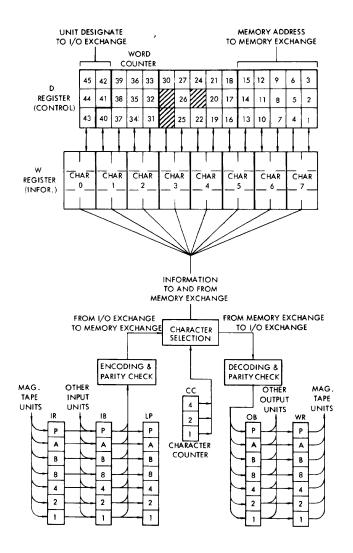

|         | W Register                                | 4-11       |

|         | D Register                                | 4-11       |

|         | Character Counter                         | 4-13       |

|         | Input Buffer Register                     | 4-13       |

|         | Tape Information Read Buffer Register     | 4-13       |

|         | Output Buffer Register                    | 4-13       |

|         | Tape Information Write Buffer Register    | 4-13       |

|         | Longitudinal Parity Register              | 4-13       |

|         | Sequence Counter                          | 4-13       |

|         | Pulse Counter                             | 4-13       |

|         | Logical Control Flip Flops                | 4-14       |

|         |                                           |            |

| SECTION | TITLE                                                | PAGE          |

|---------|------------------------------------------------------|---------------|

| 4       | Information Flow                                     |               |

|         | Input Information Flow                               | 4-14          |

|         | Output Information Flow                              | 4-14<br>4-14  |

|         | Card Reader Input                                    |               |

| 5       |                                                      | 4-14          |

| 5       | WORD MODE OPERATION                                  | 5-1           |

|         |                                                      | 5-1           |

|         | Syllable Addressing and Syllable Identification      | 5-1           |

|         | Syllable Addressing and Format                       | 5-1           |

|         | P and T Registers                                    | 5-1           |

|         | L and C Registers                                    | 5-1           |

|         | Word Mode Syllable Identification                    | 5-2           |

|         | Syllable Type                                        | 5-2           |

|         | Bits 0-9                                             | 5-2           |

|         | Coding a Syllable Using Octal Multiplication by Four | 5-3           |

|         | Decoding a Syllable Using Octal Division by Four     | 5-3           |

|         | Relative Addressing                                  | 5-4           |

|         | T0 OFF - (A38 OFF)                                   | 5-5           |

|         | TO ON, T1 ON T2 OFF - (A38 ON, A39 OFF)              | 5-5           |

|         | TO ON, T1 ON, T2 OFF - (A38 ON, A39 ON, A40 OFF)     | 5-5           |

|         | TO ON, T1 ON, T2 ON - (A38 ON, A39 ON, A40 ON)       | 5-5           |

|         | Normal Word Mode Addressing                          | 5-5           |

|         | Operand Call Syllable                                | 5-6           |

|         | Descriptor Call Syllable                             | 5-6<br>5-6    |

|         | Data Descriptors                                     | 5-6<br>5-7    |

|         | Application of Data Descriptors                      | 5-7<br>5-8    |

|         | Subroutines                                          | 5-8           |

|         | SALF                                                 | 5-8           |

|         | Subroutine Entry and Exit                            | 5-10          |

|         | Special Subroutine Entry and Exit                    | 5-10<br>5-10  |

|         | Mark Stack Control Word (MSCW) Description           | 5-10<br>5-10  |

|         | Mark Stack Control Word Format                       | 5-10<br>5-10  |

|         | Program Descriptor Description                       | 5-10<br>5-11  |

|         | Program Descriptor Format                            | 5-11<br>5-12  |

|         | Return Control Word (RCW) Description                | 5-12          |

|         | Return Control Word Format                           | 5-12          |

|         | State and Mode                                       | 5 <b>-</b> 13 |

|         | State                                                | 5-13          |

|         | Control State                                        | 5-13          |

|         | Normal State                                         | 5-13          |

|         | Mode                                                 | 5-13          |

|         | Word Mode                                            | 5-14          |

|         | Character Mode                                       | 5-14          |

|         | Processor Initiation                                 | 5-14          |

|         | Interrupt Occurring While in Normal State (NCSF=1)   | 5-14          |

|         | Word Mode                                            | 5-15          |

|         | Character Mode                                       | 5-15          |

|         | Processor 1                                          | 5-15          |

|         | Processor 2                                          | 5-15          |

|         | Interrupt Control Word Format                        | 5-18          |

| SECTION | TITLE                                             | PAGE |

|---------|---------------------------------------------------|------|

| 5       | Interrupt Return Control Word Format              | 5-18 |

|         | Initiate Control Word (INCW) Description          | 5-19 |

|         | Initiate Control Word Format                      | 5-20 |

|         | Initiating an Input/Output Operation              | 5-20 |

|         | General                                           | 5-20 |

|         | Detail                                            | 5-20 |

|         | Load Operation                                    | 5-21 |

| 6       | WORD MODE SYLLABLES AND OPERATORS                 | 6-1  |

|         | General                                           | 6-1  |

|         | LITC Literal Call Syllable (LTSL) XXX0 or XXX4    | 6-1  |

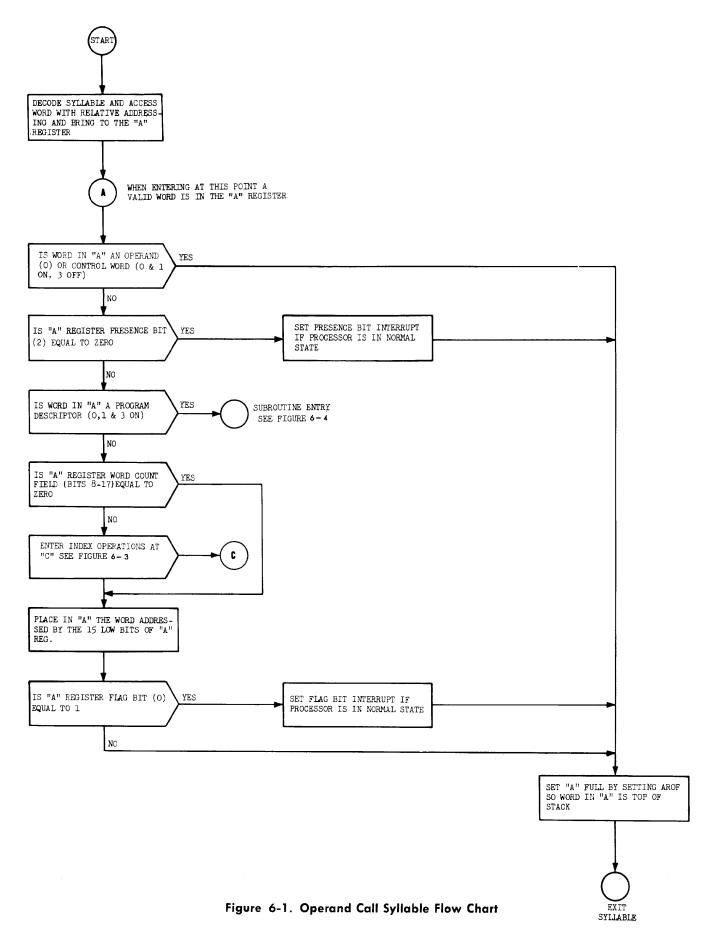

|         | OPDC Operand Call Syllable (OCSL) XXX2 or XXX6    | 6-1  |

|         | Operand or Control Word                           | 6-1  |

|         | Data Descriptor                                   | 6-2  |

|         | Presence Bit Off                                  | 6-2  |

|         | Presence Bit On                                   | 6-7  |

|         | Program Descriptor                                | 6-7  |

|         | Presence Bit Off                                  | 6-7  |

|         | Presence Bit On                                   | 6-7  |

|         | Argument Bit Off                                  | 6-7  |

|         | Argument Bit On                                   | 6-7  |

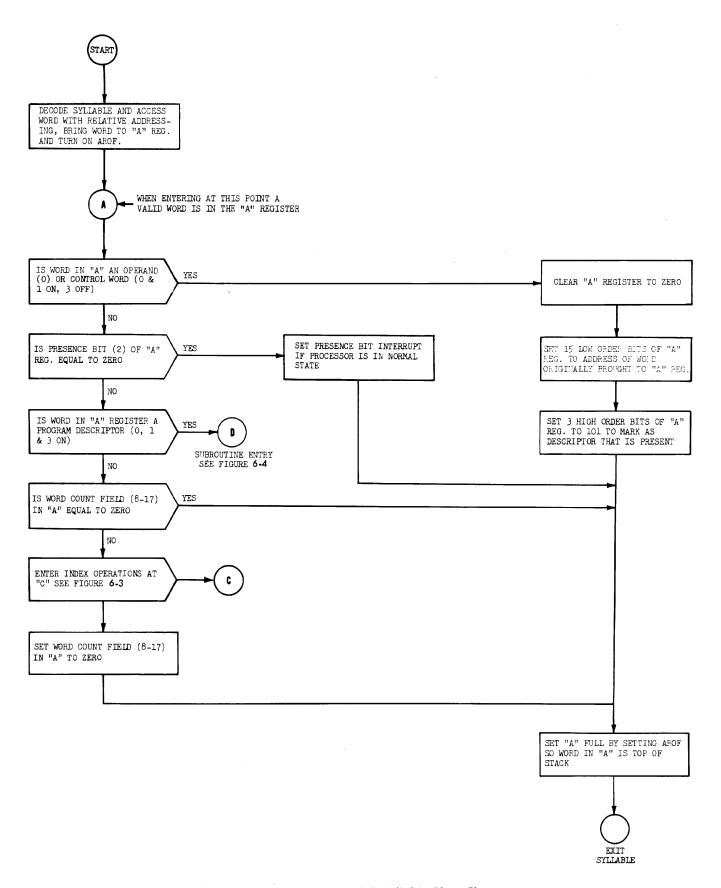

|         | DESC Descriptor Call Syllable (DCSL) XXX3 or XXX7 | 6-8  |

|         | Operand or Control Word                           | 6-8  |

|         | Data Descriptor                                   | 6-8  |

|         | Presence Bit Off                                  | 6-8  |

|         | Presence Bit On                                   | 6-8  |

|         | Program Descriptor                                | 6-8  |

|         | Operator Syllables                                | 6-9  |

|         | Arithmetic Operators - Single Precision           | 6-9  |

|         | ADD Single Precision Add (AD1L) 0101              | 6-9  |

|         | SUB Single Precision Subtract (SU1L) 0301         | 6-10 |

|         | MUL Single Precision Multiply (MU1L) 0401         | 6-10 |

|         | DIV Single Precision Divide (DV1L) 1001           | 6-10 |

|         | IDV Integer Divide (DV3L) 3001                    | 6-10 |

|         | RDV Remainder Divide (DV4L) 7001                  | 6-11 |

|         |                                                   |      |

|         | Arithmetic Operators - Double Precision           | 6-11 |

|         | DLA Double Precision Add (AD2L) 0105              | 6-11 |

|         | DLS Double Precision Subtract (SU2L) 0305         | 6-12 |

| ,       | DLM Double Precision Multiply (MU2L) 0405         | 6-12 |

|         | DLD Double Precision Divide (DV2L) 1005           | 6-12 |

|         | Logical Operators                                 | 6-13 |

|         | LND Logical and (LOAL) 0415                       | 6-13 |

|         | LOR Logical or (LOOL) 0215                        | 6-13 |

|         | LQV Logical Equivalence (LOEL) 1015               | 6-13 |

|         | LNG Logical Negate (LONL) 0115                    | 6-13 |

|         | Relational Operators                              | 6-13 |

|         | GTR B Greater Than A (BGAL) 0225                  | 6-13 |

|         | GEQ B Greater Than or Equal to A (BGEL) 0125      | 6-13 |

|         | EQL B Equal to A (BEQL) 4425                      | 6-14 |

|         | LEQ B Less Than or Equal to A (BLEL) 4125         | 6-14 |

|         | LSS B Less Than A (BLAL) 4225                     | 6-14 |

| SECTION | TITLE                                                                | PAGI         |

|---------|----------------------------------------------------------------------|--------------|

| 6       | NEQ B Not Equal to A (BNEL) 0425                                     | 6-14         |

|         | Branch Operators                                                     | 6-14         |

|         | BFW Branch Forward Unconditional (BFUL) 4231                         | 6-14         |

|         | BBW Branch Backward Unconditional (BBUL) 4131                        | 6-14         |

|         | BFC Branch Forward Conditional (BFCL) 0231                           | 6-14         |

|         | BBC Branch Backward Conditional (BBCL) 0131                          | 6-15         |

|         | BRT Branch Return (RJPL) 0135                                        | 6-15         |

|         | LFU Word Branch Forward Unconditional (JFUL) 6231                    | 6-15         |

|         | LBU Word Branch Backward Unconditional (JBUL) 6131                   | 6-15         |

|         | LFC Word Branch Forward Conditional (JFCL) 2231                      | 6-16         |

|         | LBC Word Branch Backward Conditional (JBCL) 2131                     | 6-16         |

|         | CBD Non-Zero Field Branch Backward,                                  | 0 10         |

|         | Destructive (ZBDL) XX51                                              | 6-16         |

|         | CBN Non-Zero Field Branch Backward,                                  | 0 10         |

|         | Non-Destructive (ZBNL) XX51                                          | 6-16         |

|         | CFD Non-Zero Field Branch Forward,                                   | 0 10         |

|         | Destructive (ZFDL) XX51                                              | 6-16         |

|         | CFN Non-Zero Field Branch Forward,                                   | 0 10         |

|         | Non-Destructive (ZFNL) XX51                                          | 6-17         |

|         | Store Operators                                                      | 6-17         |

|         | STD "B" Store Destructive (BSDL) 0421                                | 6-17         |

|         | SND "B" Store Non-Destructive (BSNL) 1021                            | 6-17         |

|         | ISD Integer Store Destructive (ISDL) 4121                            | 6-18         |

|         | ISN Integer Store Non-Destructive (ISNL) 4221                        |              |

|         | CID Conditional Integer Store Destructive (CSDL) 0121                | 6-18<br>6-18 |

|         | CND Conditional Integer Store Non-Destructive (CSNL) 0221.           |              |

|         | NOP Word Mode No-Op (NOPL) 0055                                      | 6-18         |

|         | Bit Operators                                                        | 6-18         |

|         | DIA Dial A (DIAL) XX55                                               | 6-18         |

|         | DIB Dial B (DIBL) XX61                                               | 6-18         |

|         | TRB Transfer Bits (TRFL) XX65                                        | 6-18         |

|         | FCE Compare Field Equal (CFEL) XX75                                  | 6-19         |

|         | FCI Compare Field Low (CFLL) XX71                                    | 6-19         |

|         | FCL Compare Field Low (CFLL) XX71                                    | 6-19         |

|         | MOP Reset Flag Bit (RFBL) 2015                                       | 6-19         |

|         | TOP Test Flag Bit (TFBL) 2031                                        | 6-19         |

|         | SSP Reset Sign Bit (MSPL) 4431                                       | 6-19         |

|         | SSN Set Sign Bit (MSNL) 0431                                         | 6-19         |

|         | CHS Change Sign Bit (CSSL) 1031                                      | 6-19         |

|         | ISO Variable Field Isolate (VFIL) XX45                               | 6-20         |

|         | CTC Transfer "Core" Field to "Core" Field (CCXL) 5425                | 6-20         |

|         | CTF Transfer "Core" Field to "F" Field (CFXL) 7425                   | 6-20         |

|         | FTF Transfer "F" Field to "F" Field (CFXL) 7425                      | 6-20         |

|         | FTF Transfer "F" Field to "F" Field (FFXL) 3425 Subroutine Operators | 6-20         |

|         | MKS Mark Stack (MSOL) 0441 · · · · · · · · · · · · · · · · · ·       | 6-20         |

|         | XIT Exit (REWL) 0435                                                 | 6-20         |

|         |                                                                      | 6-20         |

|         | RTN Return Normal (RNML) 0235                                        | 6-21         |

|         | CMN Enter Character Mode In Line (ECML) 4441                         | 6-21         |

|         | Omita Direct Originationed Middle III Dille (EUML) 4441              | 6-22         |

| SECTION | TITLE                                            | PAG        |

|---------|--------------------------------------------------|------------|

| 6       | Stack Operators                                  | 6-22       |

|         | XCH Exchange (EXCL) 1025                         | 6-22       |

|         | DUP Duplicate (DUPL) 2025                        | 6-22       |

|         | DEL Delete Top of Stack (DELL) 0065              | 6-23       |

|         | Miscellaneous Operators                          | 6-23       |

|         | LOD Load Operator (LODL) 2021                    | 6-23       |

|         | INX Index (INDL) 0141                            | 6-23       |

|         | COC Construct Operand Call (MDVL) 0241           | 6-23       |

|         | CDC Construct Descriptor Call (MDAL) 1241        | 6-23       |

|         | COM Communication Operator (COML) 1011           | 6-23       |

|         | PRL Program Release (PREL) 0111                  | 6-23       |

|         | SFI Store for Interrupt Operator (SFIL) 3011     | 6-24       |

|         | General                                          | 6-24       |

|         | Forced Store for Interrupt                       |            |

|         | Programmatic Use of Store for Interrupt Syllable | 6-26       |

|         | Sequence of the Store for Interrupt Syllable     | 6-26       |

|         | Word Mode                                        | 6-27       |

|         | Word Mode                                        | 6-27       |

|         | Character Mode                                   | 6-27       |

|         | ZPI Conditional Halt (CHPL) 2411                 | 6-27       |

|         | XRT Set Variant (VARL) 0061                      | 6-27       |

|         | SFT Store for Test (STFL) 3411                   | 6-28       |

|         | SSF Set or Store S or F Registers (FXSL) 2141    | 6-28       |

|         | FBS Flag Bit Search (SSFL) 7031                  | 6-28       |

|         | LLL Link List Lookup (LLLL) 2541                 | 6-29       |

|         | TUS Interrogate Peripheral Status (IPSL) 2431    | 6-29       |

|         | TIO Interrogate I/O Channels (TIOL) 6431         | 6-30       |

|         | Control State Operators                          | 6-30       |

|         | ITI Interrogate Interrupt (IINL) 0211            | 6-30       |

|         | IOR I/O Release (IORL) 2111                      | 6-30       |

|         | IIO Initiate I/O (IOOL) 4411                     | 6-30       |

|         | IPI Initiate P1 (INIL) 4111                      | 6-30       |

|         | IP2 Initiate P2 (PTOL) 4211                      | 6-30       |

|         | HP2 Halt P2 (HP2L) 2211                          | 6-31       |

|         | RTR Read Timer (RDTL) 0411                       | 6-31       |

|         | IFT Test Initiate (IFTL) 5111                    | 6-31       |

|         | II I Tobb Middle (II II) bill,,,,,               | 0-01       |

| 7       | CHARACTER MODE OPERATION                         | 7-1        |

| •       | General                                          | 7-1        |

|         | Function                                         | 7-1<br>7-1 |

|         | Character Mode Data Representation               | _          |

|         | Alphanymenia                                     | 7-1        |

|         | Alphanumeric                                     | 7-1        |

|         | Numeric                                          | 7-2        |

|         | Character Mode Addressing                        | 7-2        |

|         | Source String Addressing                         | 7-3        |

|         | Destination String Addressing                    | 7-3        |

|         | Entrance to Character Mode                       | 7-4        |

|         | Character Mode Syllable Decoding                 | 7-5        |

|         | Character Mode Loops                             | 7-5        |

|         | Loop Control Word (LCW) Description              | 7-6        |

| SECTION | TITLE                                              | PAGE         |

|---------|----------------------------------------------------|--------------|

| 7       | Loop Control Word Format                           | 7-6          |

|         | Interrupt Loop Control Word (ILCW) Description     | 7-7          |

|         | Interrupt Loop Control Word Format                 | 7-7          |

|         | Exit from Character Mode                           | 7-7          |

| 8       | CHARACTER MODE OPERATORS                           | 8-1          |

|         | General                                            | 8-1          |

|         | Character Mode Addressing                          | 8-1          |

|         | Source String                                      | 8-1          |

|         | Destination String                                 | 8-1          |

|         | Character Movement                                 | 8-1          |

|         | Address Adjustment                                 | 8-1          |

|         | Operator Syllables                                 | 8-1          |

|         | Operations Involving Memory Accesses to Source and |              |

|         | Destination Areas                                  | 8-2          |

|         | Transfer Operators                                 | 8-2          |

|         | TRS Transfer Source Characters (TSDL) XX77         | 8-2          |

|         | TRP Transfer Program Characters (TPDL) XX74        | 8-2          |

|         | TRZ Transfer Zones (TZDL) XX76                     | 8-2          |

|         | TRN Transfer Numeric (TNDL) XX75                   | 8-2          |

|         | TRW Transfer Words (TWDL) XX05                     | 8-2          |

|         | TBN Transfer Blanks for Non-Numerics (TBZL) XX12   | 8-3          |

|         | Test Operators                                     | 8-3          |

|         | TGR Test for Greater (TGTL) XX27                   | 8-3          |

|         | TEG Test for Greater or Equal (TGEL) XX26          | 8-3          |

|         | TEQ Test for Equal (TEQL) XX24                     | 8-3          |

|         | TEL Test for Equal or Less (TLEL) XX34             | 8-3          |

|         | TLS Test for Less (TLTL) XX35                      | 8-3          |

|         | The Test for Not Equal (TNEL) XX25                 | 8-3          |

|         | TAN Test for Alphanumeric (TANL) XX36              | 8-4          |

|         | BIT Test Bit (TEBL) XX37                           | 8-4          |

|         | Comparison Operators                               | 8-4          |

|         | CGR Compare for Greater (SGTL) XX63                | 8-4          |

|         | CEG Compare for Greater or Equal (SGFI) XX69       | 8-4          |

|         | CEQ Compare for Equal (SEQL) XX60                  | 8-4          |

|         | CEL Compare for Equal or Less (SLEL) XX70          | 8-4          |

|         | CLS Compare for Less (SLTL) XX71                   | 8-4          |

|         | CNE Compare for Not Equal (SNEL) XX61              | 8-5          |

|         | Jump Operators                                     | 8-5          |

|         | JFW Jump Forward Unconditional (FWJL) XX47         | 8-5          |

|         | JRV Jump Reverse Unconditional (REJL) XX57         | 8-5          |

|         | JFC Jump Forward Conditional (CFJL) XX45           | 8-5          |

|         | JRC Jump Reverse Conditional (CRJL) XX55           | 8-5          |

|         | BNS Begin Loop (BELL) XX52                         | 8-5          |

|         | ENS End Loop (ENLL) XX51                           | 8-5          |

|         | JNC Jump Out-of-Loop Conditional (CJOL) XX44       | 8-5          |

|         | Skip Operators                                     | 8-6          |

|         | SFS Skip Forward Source (FSSL) XX31                | 8 <b>-</b> 6 |

|         | SRS Skip Reverse Source (RSSL) XX30                | 8-6          |

|         | ALLO COMP INCIDED DOUTED (INDEL) AND               | 8-6          |

| SECTION | TITLE                                        | PAGE |

|---------|----------------------------------------------|------|

| 8       | SFD Skip Forward Destination (FSDL) XX16     | 8-6  |

|         | SRD Skip Reverse Destination (RSDL) XX17     | 8-6  |

|         | BSD Skip Bit Destination (SBDL) XX02         | 8-6  |

|         | BSS Skip Bit Source (SBSL) XX03              | 8-6  |

|         | Address Operators                            | 8-6  |

|         | SSA Store Source Address (STSL) XX15         | 8-6  |

|         | SDA Store Destination Address (STDL) XX14    | 8-6  |

|         | SCA Store Control Address (STPL) XX54        | 8-6  |

|         | RSA Recall Source Address (RSAL) XX53        | 8-6  |

|         | RDA Recall Destination Address (RDAL) XX04   | 8-6  |

|         | RCA Recall Control Address (RPAL) XX50       | 8-7  |

|         | SES Set Source Address (SSPL) XX22           | 8-7  |

|         | SED Set Destination Address (SDPL) XX06      | 8-7  |

|         | TSA Transfer Source Address (SSAL) XX56      | 8-7  |

|         | TDA Transfer Destination Address (SDAL) XX07 | 8-7  |

|         | Arithmetic Operators                         | 8-7  |

|         | FAD Field Add (FADL) XX73                    | 8-7  |

|         | FSU Field Subtract (FSUL) XX72               | 8-7  |

|         | Conversion Operators                         | 8-8  |

|         | ICV Input Convert (ICOL) XX67                | 8-8  |

|         | OCV Output Convert (OCOL) XX66               | 8-8  |

|         | Missellaneous Operators                      | 8-8  |

|         | Miscellaneous Operators                      | 8-8  |

|         | ING Increase Telly (INT) VV40                | 8-8  |

|         | INC Increase Tally (INTL) XX40               | 8-8  |

|         | STC Store Tally (STAL) XX41                  | 8-8  |

|         | BIR Reset Bit (REBL) XX65                    |      |

|         | BIS Set Bit (SEBL) XX64                      | 8-8  |

|         | CRF Call Repeat Field (CLRL) XX43            | 8-9  |

|         | EXC Exit Character Mode (RECL) XX00          | 8-9  |

|         | CMX Exit Character Mode in Line (ILEL) 0100  | 8-9  |

| 9       | PERIPHERAL UNITS                             | 9-1  |

|         | General                                      | 9-1  |

|         | B 122 Card Reader                            | 9-1  |

|         | Functional Characteristics                   | 9-1  |

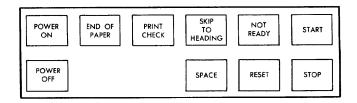

|         | Control Panel                                | 9-1  |

|         | B 123 Card Reader                            | 9-3  |

|         | B 124 Card Reader                            | 9-3  |

|         | Functional Characteristics                   | 9-3  |

|         | Control Panel                                | 9-3  |

|         | B 129 Card Reader                            | 9-4  |

|         | B 303 Card Punch                             | 9-4  |

|         | Functional Characteristics                   | 9-5  |

|         | Control Panel                                | 9-5  |

|         | B 304 Card Punch                             | 9-7  |

|         | Functional Characteristics                   | 9-7  |

|         | Control Panel                                | 9-7  |

|         | B 141 Paper Tape Reader                      | 9-9  |

|         | Functional Characteristics                   | 9-9  |

|         | Channel Select Diughoard                     | 9-10 |

| ECTION | TITLE                                                   | PAGE          |

|--------|---------------------------------------------------------|---------------|

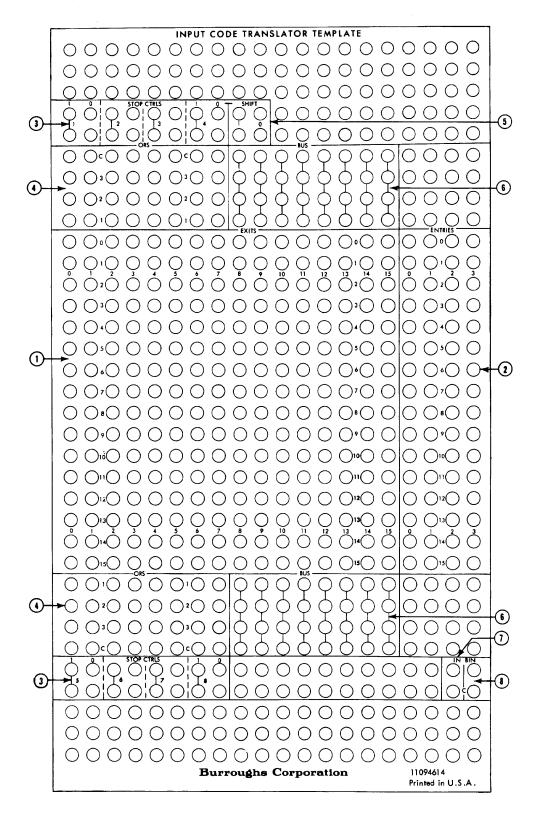

| 9      | Code Translator                                         | 9-10          |

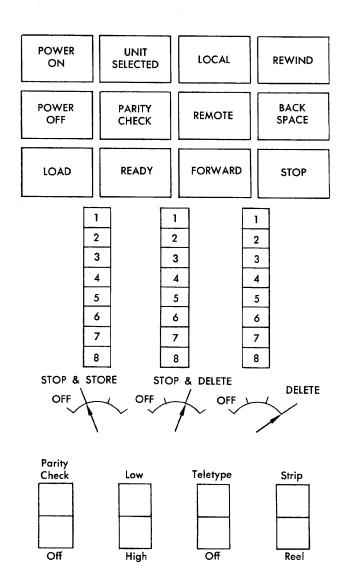

|        | Control Panel                                           | 9-12          |

|        | B 341 Paper Tape Punch                                  | 9-12          |

|        | Functional Characteristics                              | 9-14          |

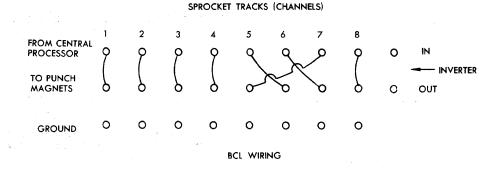

|        | Channel Select Plugboard                                | 9-15          |

|        | Code Translator                                         | 9-16          |

|        | Control Panel                                           | 9 <b>-1</b> 8 |

|        | B 320 Line Printer                                      | 9-19          |

|        | B 321 Line Printer                                      | 9-19          |

|        | Functional Characteristics                              | 9-20          |

|        | Tape Controlled Carriage                                | 9-20          |

|        | Control Tape                                            | 9-20          |

|        | Control Panel                                           | 9-21          |

|        | B 325 Line Printer                                      | 9-21<br>9-22  |

|        | B 328 Line Printer                                      | 9-22<br>9-22  |

|        | Functional Characteristics                              |               |

|        | B 329 Line Printer                                      | 9-22          |

|        | B 329 Line Printer Control Panel - B 328/B 329          | 9-22<br>9-22  |

|        | B 423 Magnetic Tape Unit                                | 9-22<br>9-23  |

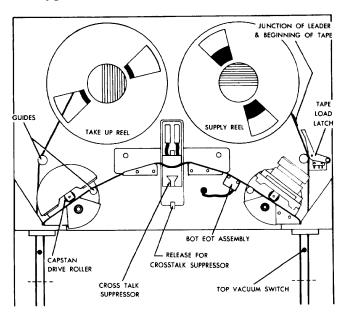

|        | B 422/B423 Magnetic Tape Unit Transport                 |               |

|        | Functional Characteristics                              | 9-23          |

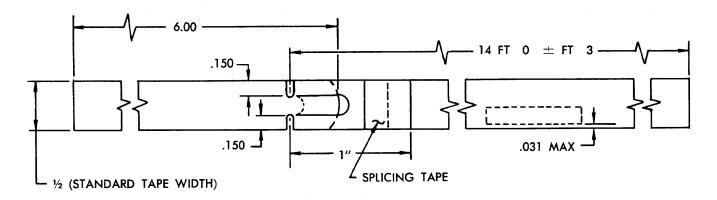

|        | Magnetic Tape                                           | 9-23          |

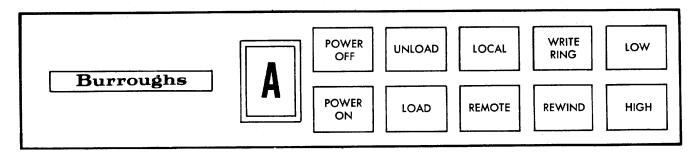

|        | Control Panel                                           | 9-24          |

|        | B 424 Magnetic Tape Unit Transport                      | 9-24<br>9-25  |

|        | B 450 Disk File/Data Communications Basic Control Unit. | 9-25<br>9-25  |

|        | B 5470 Disk File Control Unit                           | 9-25<br>9-26  |

|        | B 471 Disk File Electronics Unit                        | 9-26<br>9-26  |

|        | Control Panel                                           | 9-26<br>9-26  |

|        | B 475 Disk File Storage Module                          | 9-28          |

|        | Disks                                                   | 9-28          |

|        | Control Panel                                           | 9-28          |

|        | B 451 Disk File Expanded Control Unit                   | 9-28          |

|        | B 5480 Data Communication Control Unit                  | 9-28          |

|        | Functional Characteristics                              | 9-28          |

|        | Busy State                                              | 9-29          |

|        | Input Ready State                                       | 9-29          |

|        | Output Ready State                                      | 9-29          |

|        | B 481 Teletype Terminal Unit                            | 9-29          |

|        | Functional Characteristics                              | 9-29          |

|        | B 483 Typewriter Terminal Unit                          | 9-29          |

|        | Functional Characteristics                              | 9-30          |

|        | B 493 Typewriter Inquiry Station                        | 9-30          |

|        | Functional Characteristics                              | 9-30          |

|        | Data Transmission System                                | 9-30          |

|        | Functional Description                                  | 9-30<br>9-30  |

|        | B 249 Data Transmission Control Unit                    | 9-30<br>9-31  |

|        | B 487 Data Transmission Terminal Unit (DTTU)            | 9-31          |

|        | Buffer Conditions                                       | 9-31<br>9-32  |

|        | Line Adaptors                                           | 9-32<br>9-32  |

|        | Typewriter                                              | 9-32<br>9-32  |

| SECTION | TITLE                                              | PAGE                     |

|---------|----------------------------------------------------|--------------------------|

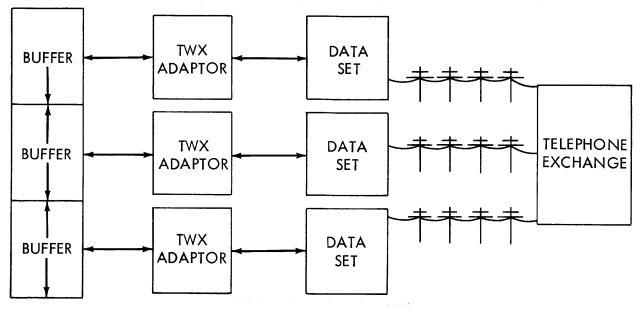

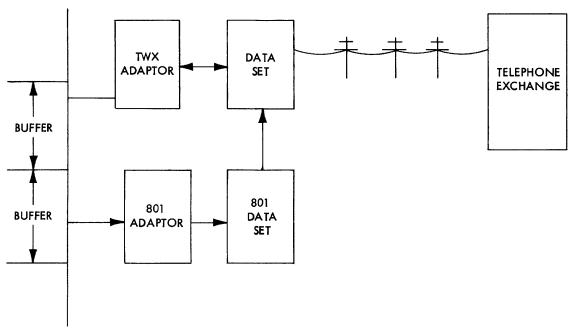

| 9       | TWX Networks                                       | 9-33                     |

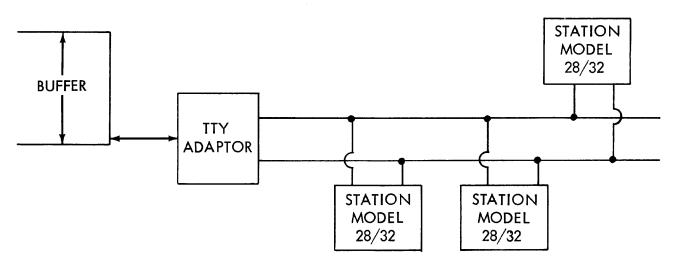

|         | Teletype Networks                                  | 9-33<br>9-34             |

|         | 801 Automatic Calling Unit (ACU)                   | 9-3 <del>4</del><br>9-34 |

|         | Dataspeed II · · · · · · · · · · · · · · · · · ·   |                          |

|         | IBM 1050                                           | 9-34                     |

|         | B 300, UNIVAC 1004                                 | 9-34                     |

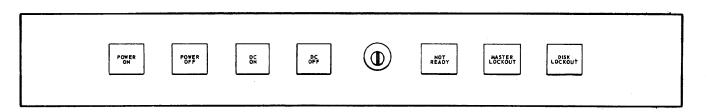

|         | Consolo                                            | 9-35                     |

|         | Console                                            | 9-35                     |

|         | Supervisory Printer                                | 9-37                     |

|         | General Description of I/O Descriptors             | 9-37                     |

|         | General Description of I/O Descriptors             | 9-38                     |

|         | General Description of Result Descriptor           | 9-38                     |

|         | Supervisory Printer I/O Result Descriptors         | 9-39                     |

|         | I/O Descriptor                                     | 9-39                     |

|         | Result Descriptor                                  | 9-39                     |

|         | Keyboard I/O Result Descriptors                    | 9-40                     |

|         | I/O Descriptors                                    | 9-40                     |

|         | Result Descriptor                                  | 9-40                     |

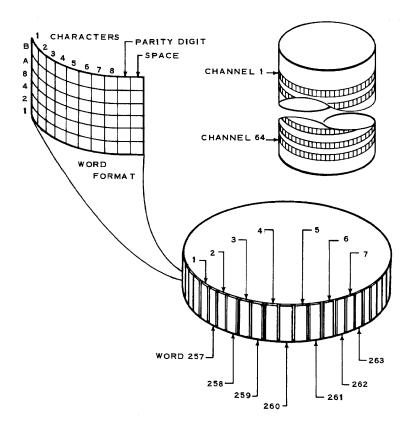

|         | Magnetic Drum                                      | 9-40                     |

|         | Magnetic Drum I/O Result Descriptors               | 9-40                     |

|         | I/O Descriptor                                     | 9-41                     |

|         | Drum Read Result Descriptor                        | 9-41                     |

|         | Drum Write Result Descriptor                       | 9-42                     |

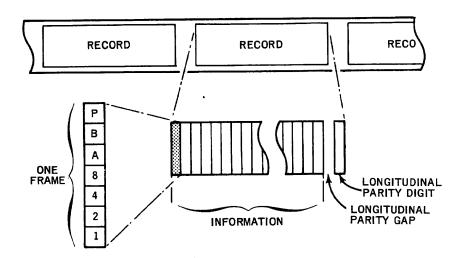

|         | Magnetic Tape Unit                                 | 9-42                     |

|         | Magnetic Tape I/O Result Descriptors               | 9-42                     |

|         | Alphanumeric Tape Read                             | 9-43                     |

|         | Control Bits:                                      | 9-43                     |

|         | Binary Tape Read:                                  | 9-44                     |

|         | Control Bits · · · · · · · · · · · · · · · · · · · | 9-44                     |

|         | Magnetic Tape Read Result Descriptor (Binary or    |                          |

|         | Alpha Mode):                                       | 9-44                     |

|         | Alphanumeric Tape Write:                           | 9-44                     |

|         | Control Bits                                       | 9-44                     |

|         | Binary Tape Write                                  | 9-45                     |

|         | Control Bits                                       | 9-45                     |

|         | Magnetic Tape Write Result Descriptors             | 9-45                     |

|         | Printer I/O - Result Descriptors                   | 9-45                     |

|         | I/O Descriptors                                    | 9-45                     |

|         | Result Descriptors                                 | 9-46                     |

|         | Card Reader I/O Result Descriptors                 | 9-46                     |

|         | I/O Descriptors                                    | 9-46                     |

|         | Result Descriptors                                 | 9-46                     |

|         | Punch I/O Result Descriptors                       | 9-46                     |

|         | I/O Pagult Descriptors                             | 9-46<br>9-46             |

|         | I/O Result Descriptors                             | 9-46<br>9-47             |

|         | Result Descriptors                                 |                          |

|         | Paper Tape Log Dead Descriptors                    | 9-47                     |

|         | Paper Tape I/O Read Descriptors                    | 9-47                     |

|         | Paper Tape Read Result Descriptors                 | 9-47                     |

|         | Paper Tape Punch I/O Descriptors                   | 9-47                     |

|         | Paper Tape Punch Result Descriptors                | 9-48                     |

|         | Disk File I/O Result Descriptors                   | 9-48                     |

| SECTION            | TITLE                                                    | PAGE |

|--------------------|----------------------------------------------------------|------|

| 9                  | Disk File I/O Descriptors                                | 9-48 |

|                    | Disk File Result Descriptor                              | 9-48 |

|                    | Data Communications                                      | 9-50 |

|                    | Input Operations                                         | 9-50 |

|                    | Output Operations                                        | 9-50 |

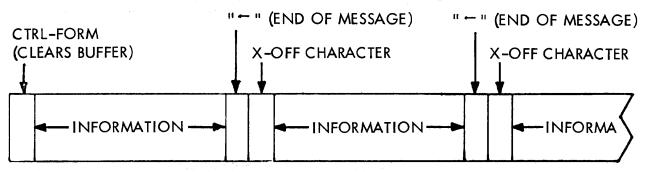

|                    | Not Exceeding Terminal Unit Buffer Capacity              | 9-50 |

|                    | Exceeding Terminal Unit Buffer Capacity                  | 9-50 |

|                    | Output Operation (Computer Initiated Messages - Teletype |      |

|                    | Terminal Units Only)                                     | 9-50 |

|                    | Data Communication I/O Result Descriptors                | 9-51 |

|                    | Inquiry Read Result Descriptor                           | 9-51 |

|                    | Inquiry Write Descriptor                                 | 9-51 |

|                    | Inquiry Write Result Descriptor                          | 9-52 |

|                    | Data Transmission                                        | 9-52 |

|                    | Typewriter/TWX Line Adaptor                              | 9-52 |

|                    | Teletype Line Adaptors                                   | 9-53 |

|                    | Dataspeed II Line Adaptor                                | 9-53 |

|                    | 801 Automatic Calling Line Adaptor                       | 9-53 |

|                    | IBM 1050 Line Adaptor                                    | 9-53 |

|                    | B 300, UNIVAC 1004 Line Adaptors                         | 9-54 |

|                    | Data Transmission I/O Result Descriptors                 | 9-54 |

| APPENDIX A         | - Codes                                                  | A-1  |

| APPENDIX B         | - Designation Number of Peripheral Unit                  | B-1  |

| APPENDIX C         | - Operators Alphabetical List                            | C-1  |

| APPENDIX D         | - Operators Numerical List                               | D-1  |

| APPENDIX E         | - Glossary                                               | E-1  |

| APPENDIX F         | - Abbreviations                                          | F-1  |

| INDEX              | ************************************                     | One  |

| ·- <b> · · · ·</b> |                                                          | One  |

## LIST OF ILLUSTRATIONS

| FIGURE       | TITLE                                                    | PAGE |

|--------------|----------------------------------------------------------|------|

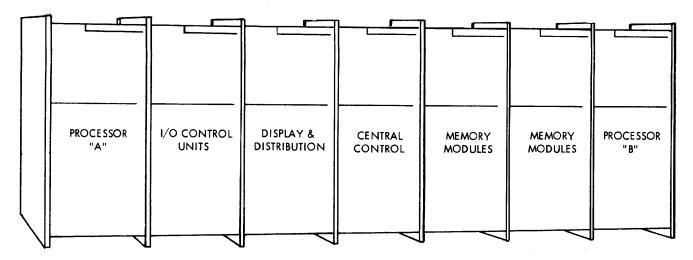

| 1-1          | Major System Cabinet Configuration                       | 1-2  |

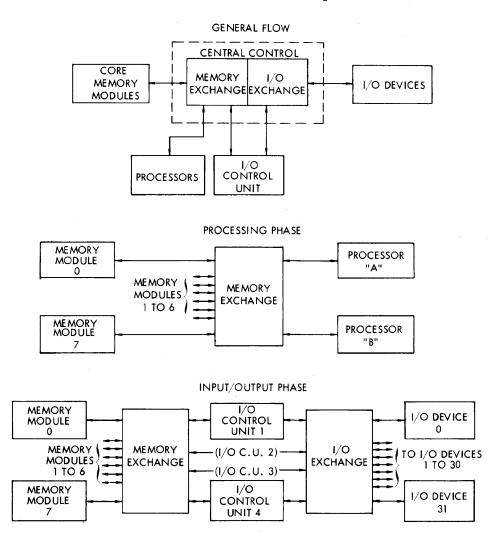

| 1-2          | Information Flow (General)                               | 1-6  |

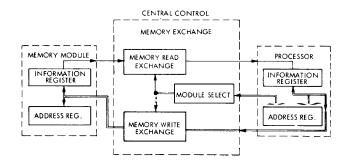

| 1-3          | Memory-Processor Communication                           | 1-7  |

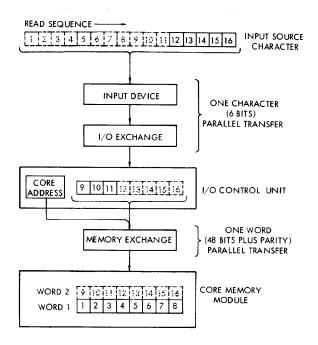

| 1-4          | Input Information Transfer                               | 1-8  |

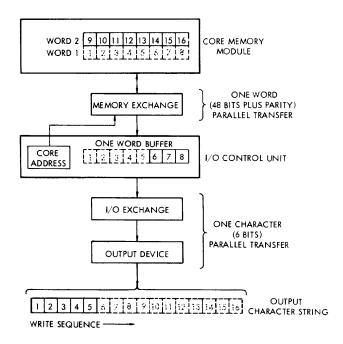

| 1-5          | Output Information Transfer                              | 1-9  |

|              |                                                          | 1-0  |

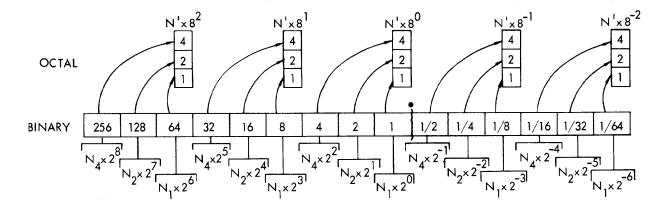

| 2-1          | Binary to Octal Conversion                               | 2-2  |

| 2-2          | Schematic of Binary to Octal Conversion of               |      |

| 2.2          | $325.75_{10} = 505.6_8 = 101000101.110$                  | 2-2  |

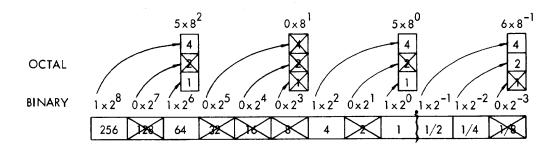

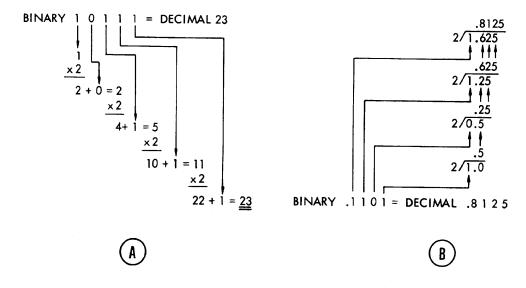

| 2-3          | Binary to Decimal Conversion                             | 2-3  |

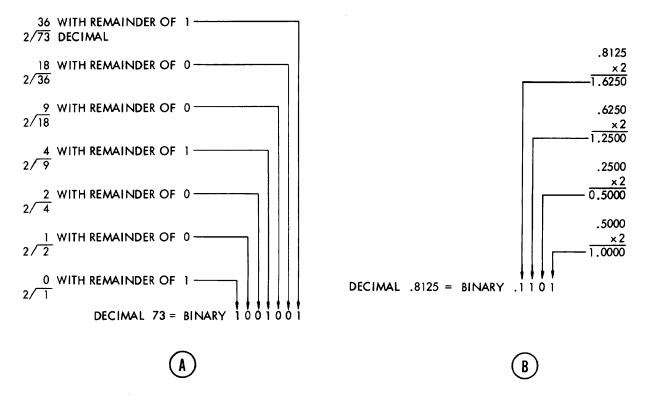

| 2-4          | Decimal to Binary Conversion                             | 2-4  |

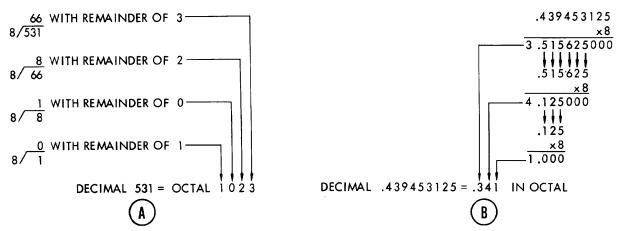

| 2-5          | Decimal to Octal Conversion                              | 2-5  |

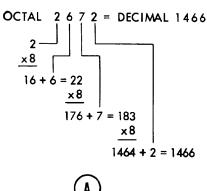

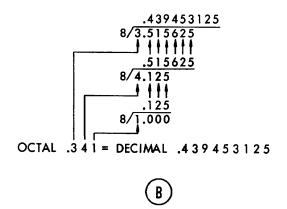

| 2-6          | Octal to Decimal Conversion                              | 2-6  |

| 2.7          | Binary Coded Decimal Representation                      | 2-7  |

| 2-8          | Character Mode Representation                            | 2-7  |

| 2-9          | Numeric Operand                                          | 2-7  |

| 2-10         | Logical Operand                                          | 2-8  |

| 3-1          | Evaluation of Polish String BC+7xA =                     | 0.0  |

| 3-2          | Execution Sequence and Stack Movement X+Y                | 3-2  |

| 3-3          | Execution Sequence and Stack Movement of Z-X+Y           | 3-4  |

| 3-4          | Stack Operation                                          | 3-6  |

|              | Stack Operation                                          | 3-9  |

| 4-1          | Processor Display Panel                                  | 4-5  |

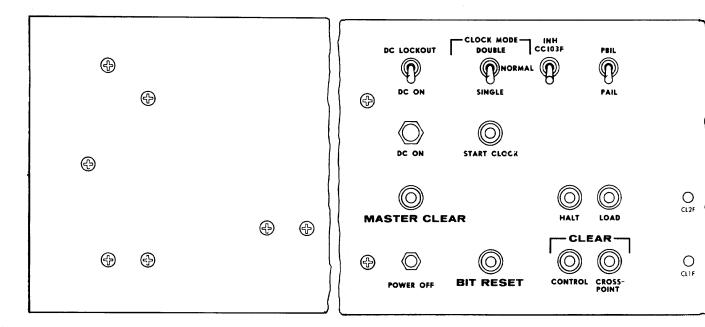

| 4-2          | Central Control Display Panel                            | 4-8  |

| 4-3          | Interrupt Priority and Addressing                        | 4-10 |

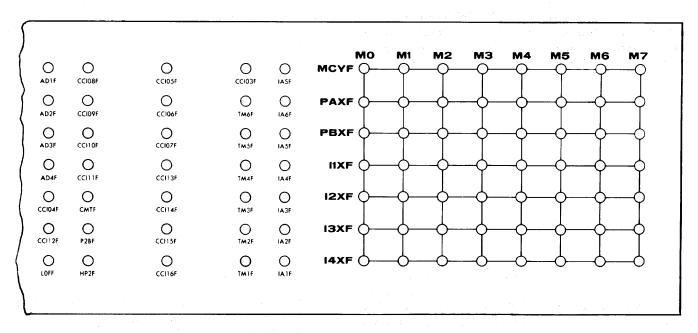

| 4-4          | I/O Display Panel                                        | 4-12 |

| 4-5          | Basic I/O Control Unit Data Flow                         | 4-15 |

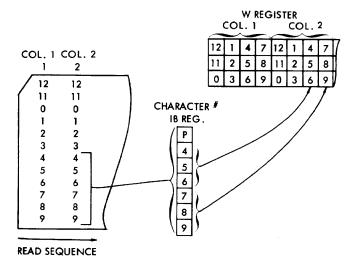

| 4-6          | Binary Card Read                                         | 4-15 |

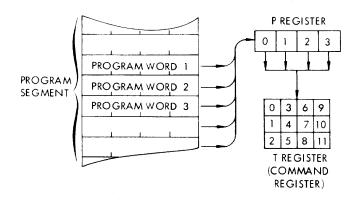

| 5-1          | Drogram Word in D. Bosiston                              |      |

| 5-2          | Program Syllable Seguence                                | 5-1  |

| 5-3          | Program Syllable Sequence                                | 5-1  |

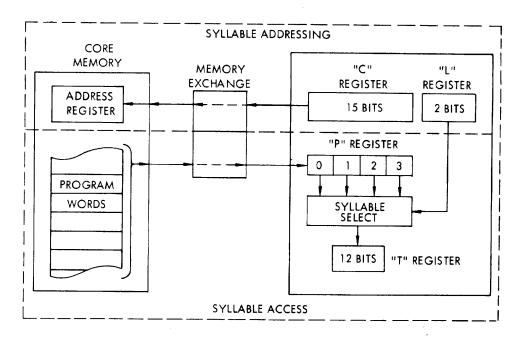

| 5-4          | Syllable Access and Address                              | 5-2  |

| 5-5          | Word Mode Syllable Format.                               | 5-2  |

| 5-6          | Generating a Syllable Using Octal Multiplication by Four | 5-3  |

| 5-7          | Decoding a Syllable Using Octal Division by Four         | 5-3  |

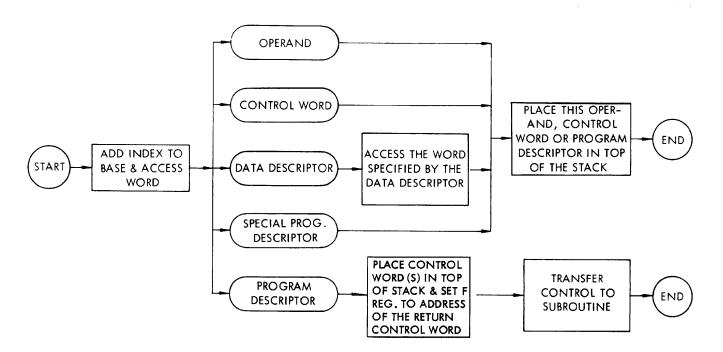

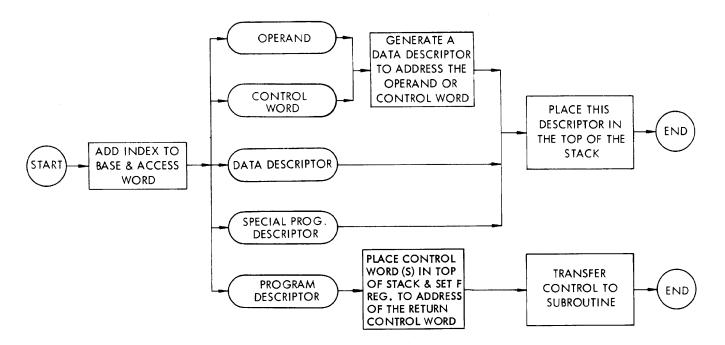

| 5- <b>8</b>  | General Flow for Operand Call Syllable                   | 5-6  |

| 5-8<br>5-9   | General Flow for Descriptor Call Syllable                | 5-7  |

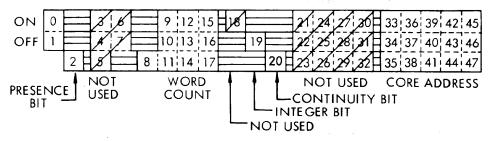

| 5-10         | Data Descriptor Exploded                                 | 5-8  |

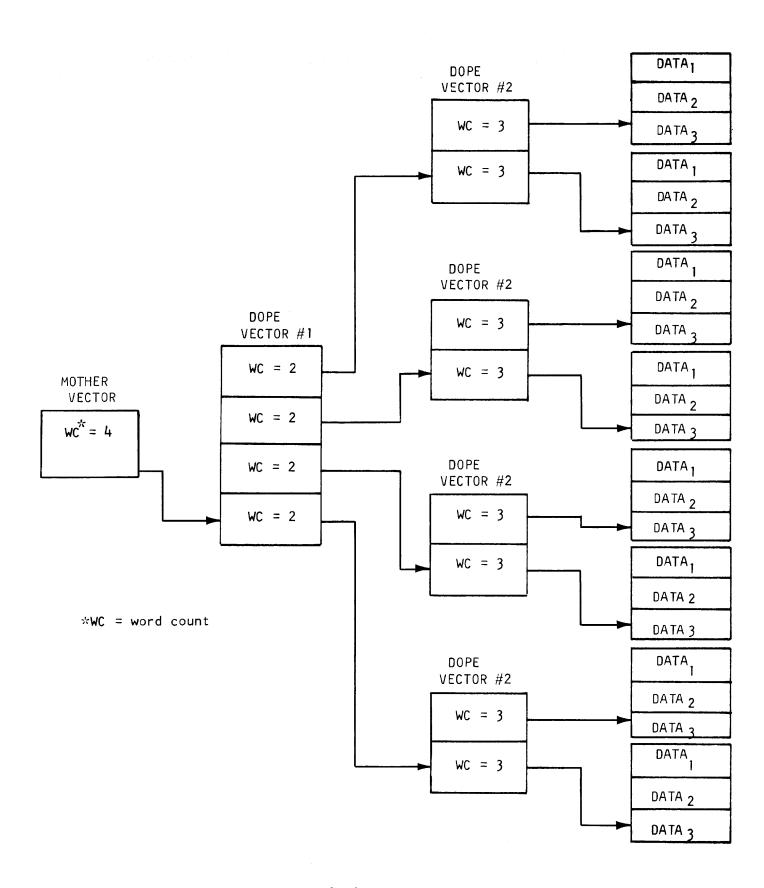

| 5-10<br>5-11 | Monte Stock Control Word Purish                          | 5-9  |

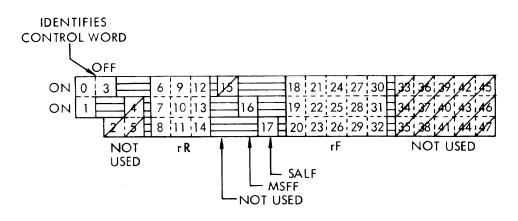

| 5-11<br>5-12 | Mark Stack Control Word Exploded                         | 5-11 |

| 5-12<br>5-13 | Program Descriptor Exploded                              | 5-12 |

| 5-13<br>5-14 | Return Control Word Exploded                             | 5-13 |

| 5-14<br>5-15 | Permissible Combinations of State, Level and Mode        | 5-15 |

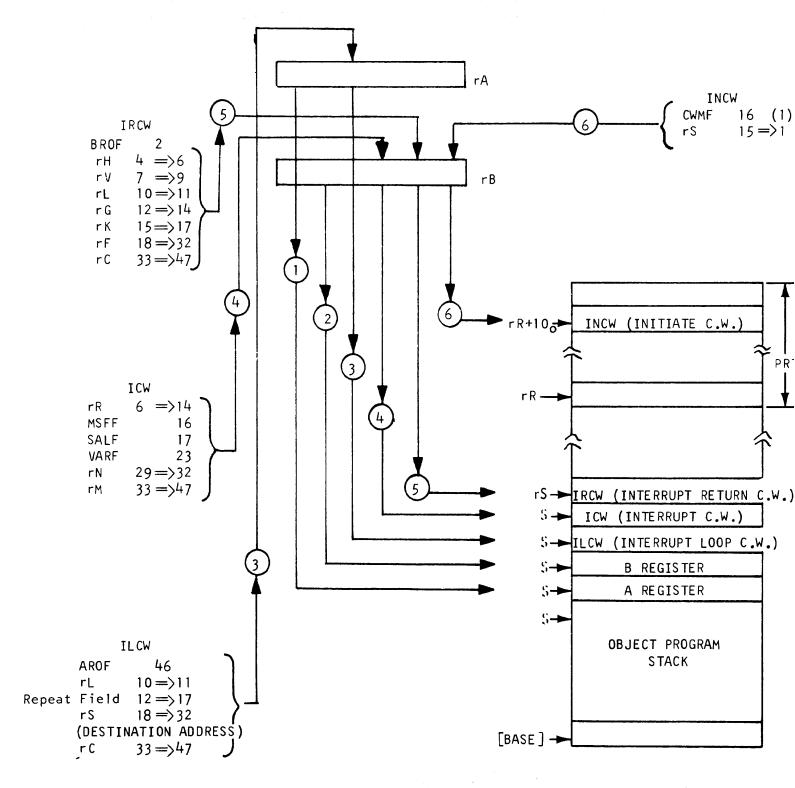

| 5-15<br>5-16 | Store for Interrupt (Word Mode)                          | 5-16 |

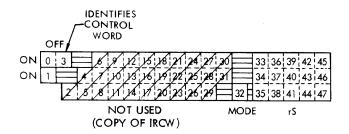

|              | Store for Interrupt (Character Mode)                     | 5-17 |

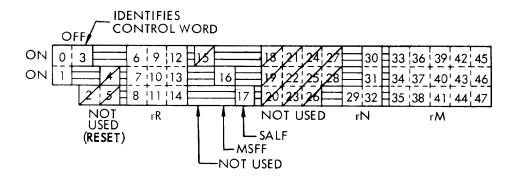

| 5-17<br>5-18 | Interrupt Control Word Exploded.                         | 5-18 |

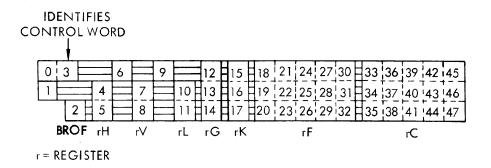

|              | interrupt Return Control Word Exploded                   | 5-19 |

| 5-19         | Initiate Control Word Exploded                           | 5-20 |

#### LIST OF ILLUSTRATIONS (CONT.)

| IGURE | ŢĬŢĹĔ                                                   | PAGE |

|-------|---------------------------------------------------------|------|

| 6-1   | Operand Call Syllable Flow Chart                        | 6-3  |

| 6-2   | Descriptor Call Syllable Flow Chart                     | 6-4  |

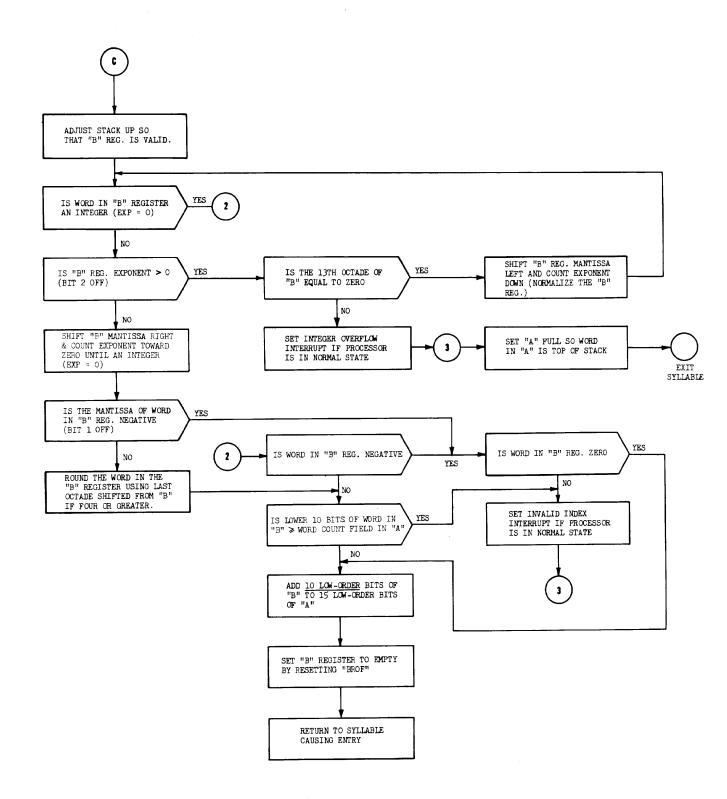

| 6-3   | Index Operations - Operand and Descriptor Call Syllable | 6-5  |

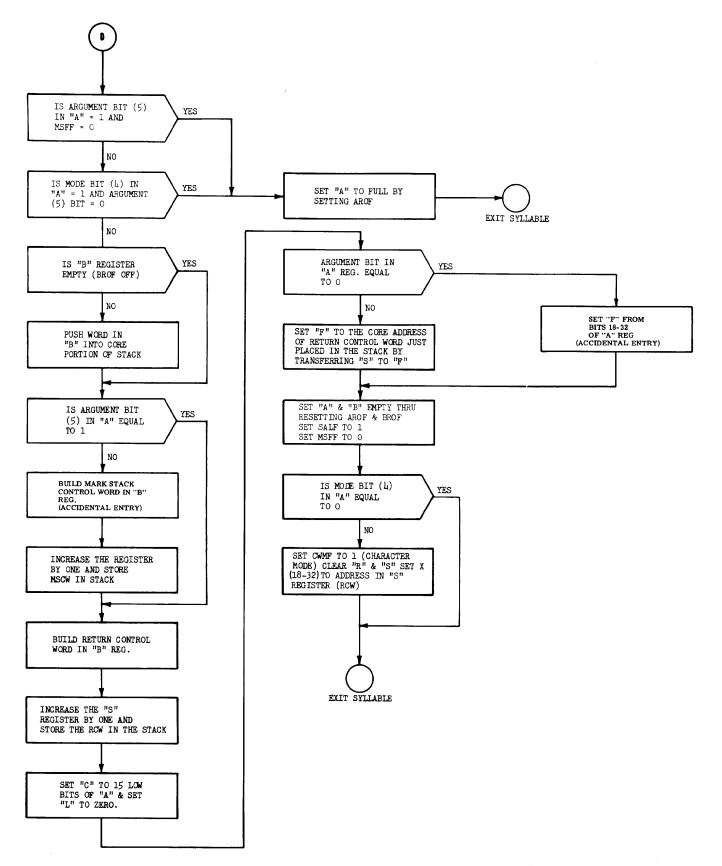

| 6-4   | Subroutine Entry - Operand or Descriptor Call Syllable  | 6-6  |

| 7-1   | Alphanumeric Character String                           | 7-2  |

| 7-2   | Alphanumeric Word                                       | 7-2  |

| 7-3   | Outgoing Alignment Station                              | 7-4  |

| 7-4   | Character Mode Syllable                                 | 7-5  |

| 7-5   | Loop Control Word Exploded                              | 7-7  |

| 7-6   | Interrupt Loop Control Word Exploded                    | 7-7  |

| 9-1   | B 122 Card Reader Control Panel                         | 9-1  |

| 9-2   | B 123/B 124 Card Reader Control Panel                   | 9-3  |

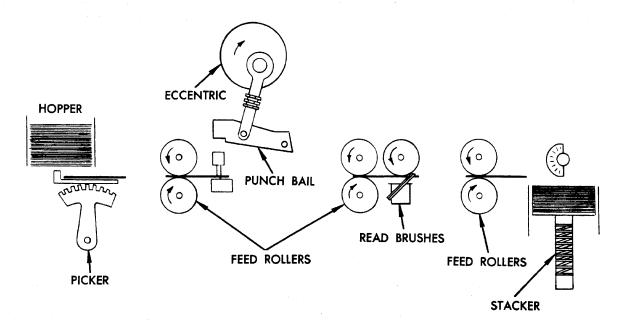

| 9-3   | B 303 Card Punch Feed Mechanism                         | 9-5  |

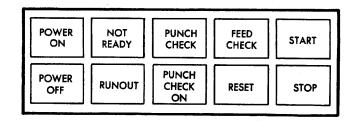

| 9-4   | B 303 Card Punch Control Panel                          | 9-5  |

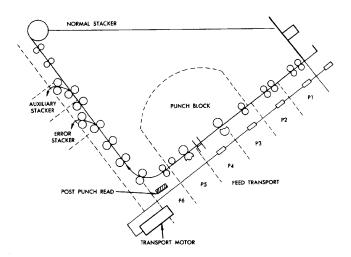

| 9-5   | B 304 Card Punch Feed Mechanism                         | 9-7  |

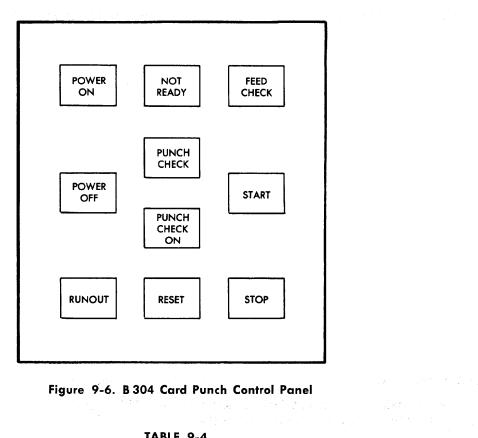

| 9-6   | B 304 Card Punch Control Panel                          | 9-8  |

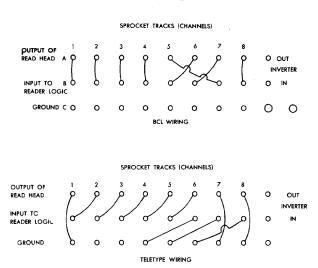

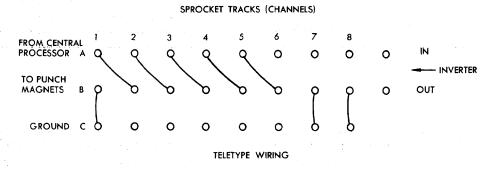

| 9-7   | Channel Select Plugboard                                | 9-10 |

| 9-8   | Plugboard Layout                                        | 9-11 |

| 9-9   | B 141 Paper Tape Reader Control Panel                   | 9-12 |

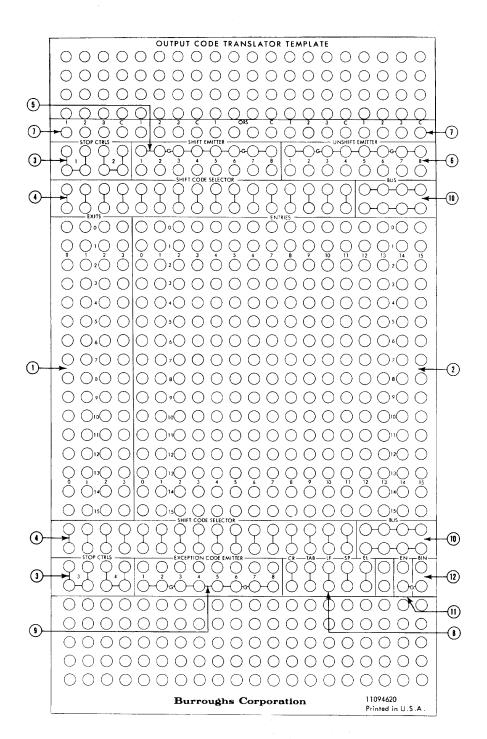

| 9-10  | Channel Select Plugboard                                | 9-15 |

| 9-11  | Plugboard Layout                                        | 9-17 |

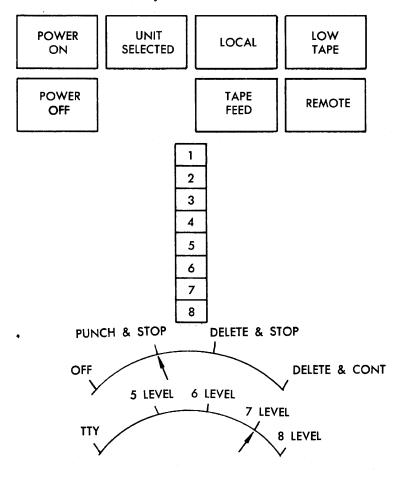

| 9-12  | B 341 Paper Tape Punch Control Panel                    | 9-18 |

| 9-13  | Special Character Set                                   | 9-20 |

| 9-14  | Carriage Control Tape                                   | 9-20 |

| 9-15  | B 320/B 321 Line Printer Control Panel                  | 9-21 |

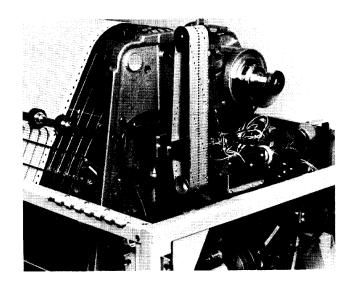

| 9-16  | B 422/B 423 Magnetic Tape Unit Transport Mechanism      | 9-23 |

| 9-17  | Magnetic Tape "Latch Leaders"                           | 9-24 |

| 9-18  | B 422/B 423 Magnetic Tape Unit Control Panel            | 9-24 |

| 9-19  | B 471 Disk File Electronics Unit Control Panel          | 9-26 |

| 9-20  | Possible Paper Tape Format                              | 9-33 |

| 9-21  | TWX Network                                             | 9-33 |

| 9-22  | Teletype Network                                        | 9-34 |

| 9-23  | 801 ACU Connection                                      | 9-35 |

| 9-24  | Magnetic Drum Format                                    | 9-41 |

| 9-25  | Tape Record Format                                      | 9-43 |

#### LIST OF TABLES

| TABLE   | TITLE                                                                  | PAG               |

|---------|------------------------------------------------------------------------|-------------------|

| 1-1     | B 5500 Configuration Chart                                             | 1-2<br>1-3<br>1-4 |

| 3-1     | Arithmetic Registers Relative to Core Portion of Stack                 | 3-7               |

| 3-2     | Description for Example of Stack Generation                            | 3-10              |

| 5-1     | Relative Addressing Table                                              | 5-4               |

| 6-1     | Relative Addressing Table                                              | 6-2               |

| 6-2     | Relation Between A Register Bit Position and Peripheral Unit           | 6-29,6-30         |

| 9-1     | B 122 Card Reader Control Panel Switches and Indicators                | 9-2               |

| 9-2     | B 123/B 124 Card Reader Control Panel Switches and Indicators          | 9-3,9-4           |

| 9-3     | B 303 Card Punch Control Panel Switches and Indicators                 | 9-6               |

| 9-4     | B 304 Card Punch Control Panel Switches and Indicators                 |                   |

| 9-5     | B 141 Paper Tape Reader Control Panel Switches and Indicators          | 9-13,9-14         |

| 9-6     | B 341 Paper Tape Punch Control Panel Switches and Indicators           | 9-19              |

| 9-7     | B 320/B 321 Line Printer Control Panel Switches and Indicators         | 9-21,9-22         |

| 9-8     | B 422/B 423 Magnetic Tape Unit Control Panel Switches and              |                   |

|         | Indicators                                                             | 9-25              |

| 9-9     | B 471 Disk File Electronics Unit Control Panel Switches and Indicators | 9-27              |

| 9-10    | Console Control Panel Switches and Indicators                          |                   |

| 9-11    | Supervisory Printer Switches and Indicators                            |                   |

| 9-12    | Descriptor Combinations                                                |                   |

| / · · - | Poporthor comprimuous                                                  | 0 10              |

# INTRODUCTION

This reference manual describes the hardware characteristics of the Burroughs B 5500 Information Processing System by presenting detailed information concerning the functional operation of the entire system. The B 5500 is a large-scale, high-speed, solid-state computer which represents a departure from the conventional computer system concept. It is a problem language oriented system rather than the conventional hardware oriented system. Because of the design concept of the B 5500, there exists a strong interdependence between the hardware and the Master Control Program which directs the system. The material presented herein pertains only to the hardware considerations, whereas the Master Control Program is discussed under separate cover.

# SECTION

# SYSTEMS DESCRIPTION

#### **GENERAL**

1-1. Without delving into such elements of computer design as circuitry and machine logic, this manual explains how the B 5500 achieves its flexibility and efficiency through a comprehensive systems approach to problem solving. The B 5500 is designed as a complete system, combining components and built-in aids, to bring simplified programing, ease of operation, and complete freedom of system expansion to the user. The B 5500 has compiler oriented machine language and logic which accept the common languages; ALGOL, FORTRAN, and COBOL. The machine language of the B 5500 is designed specifically for these problem languages, reducing compilation time and eliminating object program redundancies. The B 5500 automatically handles memory assignments, input/output unit assignments, segmentation of programs, and subroutine linkages, eliminating many arduous programing tasks and reducing the likelihood of error. Programs may be corrected at the source language level and are simplified by integral debugging aids.

#### MASTER CONTROL PROGRAM

1-2. The Master Control Program provides the over-all coordination and control of processing that is so important to total production through the maximum use of all B 5500 components. Operator intervention is

nearly eliminated because complete management of the system is assumed by the Master Control Program, a comprehensive operating system that provides simultaneous input/ output operations and multiprocessing. By controlling the sequence of processing, initiating all input/output operations and providing automatic handling procedures to meet virtually all processing conditions, the Master Control Program can obtain maximum use of the system components at all times. Because so many functions are performed under this centralized control, changes in schedule, system configuration, and program sizes can be readily accommodated; thus achieving greater over-all production and efficiency.

1-3. The configuration for a B 5500 system may vary considerably, depending on specific applications and expected workload. Both the possible components and the maximum configuration are listed in table 1-1.

# DESCRIPTION AND FUNCTION OF MAJOR UNITS

1-4. The major units of a maximum B 5500 configuration include central control unit, processors A and B, memory modules 0 to 7, input/output control units 0 to 3, and display and distribution unit. These major units are contained in a major system cabinet and must be arranged in a specific order (figure 1-1).

Figure 1-1. Major System Cabinet Configuration

TABLE 1-1

B 5500 Configuration Chart

| Unit<br>Number | Description           | Max. | Ability of<br>One Unit        | Notes                                        |  |

|----------------|-----------------------|------|-------------------------------|----------------------------------------------|--|

| B 5280         | Processor A           | 1    |                               |                                              |  |

| B 5281         | Processor B           | 1    |                               |                                              |  |

| B 460          | Memory Module         | 8    | 4096 words 6 μs<br>cycle time | B 460 and B 461 modules                      |  |

| B 461          | Memory Module         | 8    | 4096 words 4 µs<br>cycle time | cannot be mixed on any one system.           |  |

| B 430          | Storage Drum          | 2    | 32,768 words                  |                                              |  |

| B 5283         | Input/Output Channels | 4    |                               |                                              |  |

| B 422          | Magnetic Tape Unit    | 16   | 24-66KC                       | 16 Tape units maximum                        |  |

| B 423          | Magnetic Tape Unit    | 16   | 24KC                          | B 422 and B 423 units cannot be mixed. B 422 |  |

| B 424          | Magnetic Tape Unit    | 16   | 66KC                          | and B 424 can be mixed if                    |  |

| B 425*         | Magnetic Tape Unit    | 16   | 18-50-72KC                    | the B 422 operates at 120 inches per second. |  |

| B 320          | Line Printer          | 2    | 475 LPM, 120 chr.             |                                              |  |

| B 321          | Line Printer          | 2    | 700 LPM, 120 chr.             |                                              |  |

| B 325          | Line Printer          | 2    | 700 LPM, 132 chr.             | Two Line Printers Max.                       |  |

| B 328          | Line Printer          | 2    | 1040 LPM, 120 chr.            |                                              |  |

| B 329          | Line Printer          | 2    | 1040 LPM, 132 chr.            |                                              |  |

| B 122          | Card Reader           | 2    | 200 CPM                       | Two Card Readers Max.                        |  |

| B 123          | Card Reader           | 2    | 475 CPM                       | I wo Card Readers Wax.                       |  |

<sup>\*</sup> Requires Feature 872 Extended Magnetic Tape Capability.

TABLE 1-1 (Cont)

B 5500 Configuration Chart

| Unit<br>Number | Description                                         | Max. | Ability of<br>One Unit                                       | Notes                                                                       |  |

|----------------|-----------------------------------------------------|------|--------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| B 124          | Card Reader                                         | 2    | 800 CPM                                                      | Two Card Readers Max.                                                       |  |

| B 129          | Card Reader                                         | 2    | 1400 CPM                                                     | Two dard neaders max.                                                       |  |

| B 303          | Card Punch                                          | 1    | 10 <b>0</b> CPM                                              | One Card Punch Max.                                                         |  |

| В 304          | Card Punch                                          | 1    | 300 CPM                                                      |                                                                             |  |

| B 141          | Paper Tape Reader*                                  | 2    |                                                              | Three Paper Tape Units                                                      |  |

| B 341          | Paper Tape Punch*                                   | 2    |                                                              | Maximum                                                                     |  |

| B 450          | Disk/File/Data Com-<br>munications Basic<br>Control | 2    |                                                              | If system has two B 5470's and one B 5480, then two B 450's are are needed. |  |

| B 452          | Disk File/Data Trans-<br>mission Basic Control      | 8    | Can hold 2<br>B 487 DTTU's                                   | Required for B 487<br>DTTU's.                                               |  |

| B 5470         | Disk File Control<br>(DFC) Unit                     | 2    |                                                              |                                                                             |  |

| B 5480         | 0 Data Communication<br>Control (DCC) Unit          |      | Can service up to<br>15 Terminal Units<br>in any combination | B 487 DTTU's not<br>allowed                                                 |  |

| В 249          | Data Transmission<br>Control Unit                   | 1    | Can service up to<br>15 Terminal Units                       | All types of Terminal<br>Units                                              |  |

| B 451          | Disk File Expanded<br>Control                       | 4    | Service up to 5<br>5 DFE Units                               | Two per each B 5470                                                         |  |

| B 471          | Disk File Electronics<br>(DFE) Unit                 | 20   |                                                              | 10 DFE Units Max. per<br>each B5470 DFC Unit                                |  |

| B 475          | Disk File Storage<br>(DFS) Module                   | 100  | 9,600,000 BCL<br>Characters                                  | 5 DFS Modules Max. per<br>each B 471 DFE Unit                               |  |

| B 481          | Teletype (TTY)<br>Terminal Unit                     | 15   | Can service up to 399 teletype units                         |                                                                             |  |

| B 483          | Typewriter (TYP)<br>Terminal Unit                   | 15   | Can service up to<br>8 B 493 TIS stations<br>simultaneously  | 15 Terminal Units Max.                                                      |  |

| B 484          | TWX (TWX) Terminal<br>Unit                          | 15   | Can service up to<br>8 AT&T Data-sets<br>simultaneously      |                                                                             |  |

<sup>\*</sup> Feature 920 is available for code translation.

TABLE 1-1 (Cont)

#### **B 5500 Configuration Chart**

| Unit<br>Number                         | Description                                                                                              | Max. | Ability of<br>One Unit                                                           | Notes                                 |

|----------------------------------------|----------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------|---------------------------------------|

| B 487                                  | Data Transmission<br>Terminal Unit (DTTU)                                                                | 15   | Can service up to<br>16 adaptors                                                 | 15 Terminal Units Max.                |

| 980<br>981<br>982<br>983<br>984<br>985 | TYP/TWX Adaptor  TTY Adaptor  Data Speed II Adaptor  801 Auto Call Unit  U1004 Adaptor  IBM 1050 Adaptor |      | 1-TIS or 1-TWX<br>network<br>1-TTY network<br>1-1004 Station<br>25-1050 Stations |                                       |

| B 493                                  | Typewriter Inquiry<br>Station (TIS)                                                                      | 120  |                                                                                  | Only 8 TIS per each<br>B 483 TYP Unit |

#### Central Control Unit

1-5. The heart of every B 5500 system is the central control unit which is comprised of three sections: memory exchange, input/output exchange, and system control. A description of the basic function of each section follows.

1-6. MEMORY EXCHANGE. The memory exchange section provides access routes for requesting units (processors and input/output control units) to core memory modules. In order to connect the proper memory module to the requesting unit, the desired address is examined to determine which memory module is being addressed, then the proper routing is established. The design of the memory exchange allows the simultaneous access of different memory modules by multiple requesting units. (One requesting unit per one memory module.) After the route is established, all bits of a word are transferred in parallel to or from the requesting unit.

1-7. INPUT/OUTPUT EXCHANGE. The input/output exchange section provides the connection between any input/output device and any input/output control unit. Like the memory exchange, the input/output exchange permits simultaneous parallel transfer of information, thus providing multiple input/output operations. The routine established enables the flow of both information and control logic to each peripheral unit.

1-8. SYSTEM CONTROL. The system control section contains the master clock, a one-sixtieth of a second timer, and an interrupt system. The one-sixtieth second timer is included to provide a means of recording job run time. The interrupt system is the major portion of the system control section and will initiate Master Control Program routines to handle "exception conditions" when they are detected.

#### Processors A and B

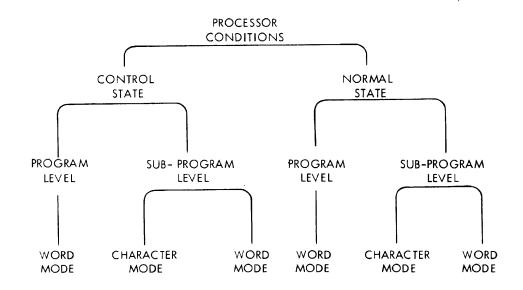

1-9. The processors of the B 5500 system are designed for maximum use of problem oriented languages. A B 5500 system may have two processors for simultaneous operation. Each processor is independent of the other in normal operation and may operate in one of two modes, word mode or character mode. Only one processor in each system can operate in either of two states, normal state or control state; the other processor must operate in normal state only.

1-10. WORD MODE. The usual mode of operation is word mode. In word mode, operators are primarily concerned with one or two complete words. Each word contains 48 bits. Registers are arranged (for display) in groups of three bits (an octade), coded in octal notation. Word mode operation uses a full parallel adder, with automatic floating point logic.

1-11. CHARACTER MODE. In character mode, a word consists of eight characters of six bits each. Operators primarily work with one character or one to six bits of a character. Character mode operation uses a serial adder and does not have automatic floating point logic. Numbers are represented in binary coded decimal (BCD).

1-12. NORMAL STATE. Instructions in this state are concerned with the conventional aspects of computation (adding, subtracting, information transfer, etc.). Any interrupt (detection of an "exceptional condition") that occurs while processing in normal state will suspend the normal state operation and transfer operation to control state in processor one.

1-13. CONTROL STATE. All operations that can be performed in normal state can also be performed in control state. Additional control operations are available while in control state. Unlike normal state, interrupts occurring in control state will not suspend processing. Most MCP (Master Control Program) routines are written to operate in the control state because of the additional control operators that are available.

1-14. OPERATORS (INSTRUCTIONS). In both normal and control state there are four operators in a word. The act of obtaining the next operator can occur simultaneously with the performance of other operations. This simultaneity of operations results in minimal time loss due to the lack of an instruction.

1-15. CLOCK. A one megacycle clock rate is used throughout the entire system. The clock rate plus the extremely efficient logic results in an average add time for two words of about  $3 \,\mu$  s. and an average multiply time for two words of about  $30 \,\mu$  s., both in floating-point.

#### Core Memory Module

1-16. A B 5500 system can have up to eight memory modules. (All eight must be either model B 460 or model B 461.) Each core memory module operates independently of any other module. Information stored in a core memory module is accessed through the memory exchange section of the central

control unit. As mentioned before, memory exchange permits parallel accesses to multiple modules (allows more than one core memory module to be accessed at the same time). Each module is a high speed (cycle time of either  $6 \mu$  s. or  $4 \mu$  s.), coincident current magnetic core memory. Every core memory module has its own address register and information buffer register. Each module contains 4096 words resulting in a maximum core memory size (for one system) of 32,768 words. One word of core memory consists of 48 bits plus one bit reserved for parity check. For the B 460 module and the B 461 module, memory cycle times are  $6 \mu$  s. and  $4 \mu$  s. respectively. When a word from either memory module B 460 or B 461 is read, the information is available for use in either 3  $\mu$  s. or 2  $\mu$  s. respectively.

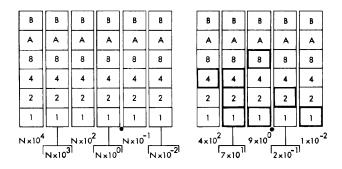

#### Input/Output Control Unit