# ELECTEC SALES, INC.

1249 BIRCHWOOD SUNNYVALE, CA. 94089 (408) 747-1722 TLX 171609 FAX - (408) 734-2043 **Communication Devices**

# 1987 Communication Devices Data Book

#### A WORD ABOUT TRADEMARKS . . .

The following AT&T trademarks are mentioned in this data book:

5ESS<sup>TM</sup> Switching Equipment, or Switch ESS<sup>TM</sup> Switching Equipment

The following AT&T registered trademarks are mentioned in this data book:

WE® 32100 Microprocessor, CPU SLC® Carrier System, or Carrier SLC® 96 Series 5 Carrier System, or Carrier System ODL® 50 Lightwave Data Link UNIX® Operating System, or System

# DATA SHEET STATUS MARKINGS . . .

Data sheets without a status marking are final and are issued when tool made samples are approved or when the product is delivered for usage, whichever occurs first. The other data sheet status markings used throughout this catalog are defined as:

ADVANCE — Issued at the exploratory stage of development when the principle characteristics are available. Some functional characteristics are subject to change.

**PRELIMINARY** — Issued after development for manufacture has been started. Some electrical and timing parameters are subject to change.

AT&T reserves the right to make changes to the product(s) or circuit(s) described herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product or circuit.

# 1987 COMMUNICATION DEVICES DATA BOOK

# **CONTENTS**

| A) | LPHANUMERIC INDEX                                                           | v     |

|----|-----------------------------------------------------------------------------|-------|

| 1. | GENERAL                                                                     |       |

|    | Introduction                                                                | 1-1   |

|    | Quality and Reliability                                                     | 1-1   |

|    | Handling and Mounting                                                       | 1-1   |

| 2. | NETWORK PRODUCTS                                                            |       |

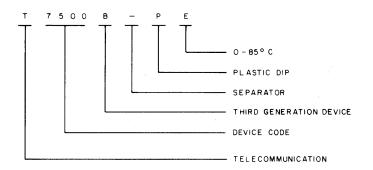

|    | T7500 PCM Codec With Filters                                                | 2-1   |

|    | T7501 PCM Codec With Filters                                                |       |

|    | T7513 PCM Codec With Filters                                                | 2-25  |

|    | T7520 High-Precision PCM Codec With Filters                                 | 2-41  |

|    | T7521 High-Precision PCM Codec Without Filters                              |       |

|    | T7522 High-Precision PCM Codec With Filters (T1 Compatible)                 |       |

|    | Custom Codecs                                                               | 2-87  |

| 3. | DATA COMMUNICATIONS                                                         |       |

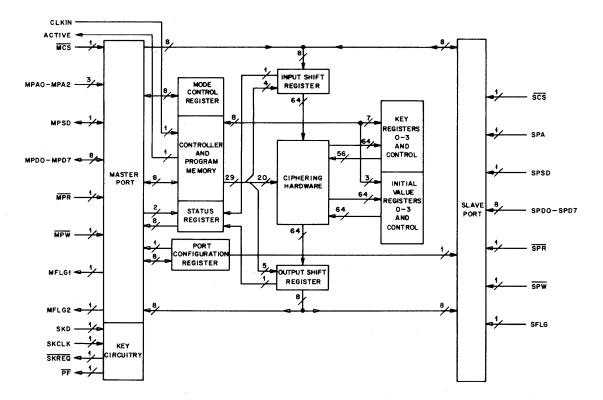

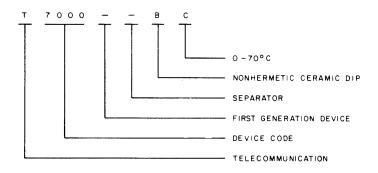

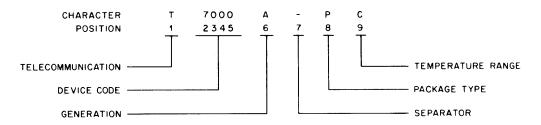

|    | T7000A Digital Encryption Processor                                         | 3-1   |

|    | T7001 Random Number Generator                                               | 3-29  |

|    | T7010 Switched Capacitor Modem                                              | 3-43  |

|    | T7011 Modem Interface Chip                                                  | 3-73  |

|    | T7018/T7019 2400 b/s Modem Chip Set                                         |       |

|    | T7100A X.25 Protocol Controller                                             |       |

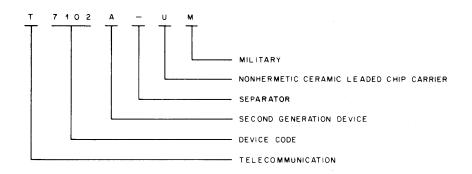

|    | T7102 X.25/X.75 Protocol Controller                                         | 3-113 |

|    | T7110 Synchronous Protocol Data Formatter With Serial Interface (SPYDER-S). | 3-16  |

|    | T7111 Synchronous Packet Data Formatter (ANT)                               | 3-19: |

|    | T7112 Asynchronous Receiver/Transmitter Interface (ARTI)                    | 3-217 |

| 4. | ISDN PRODUCTS                                                               |       |

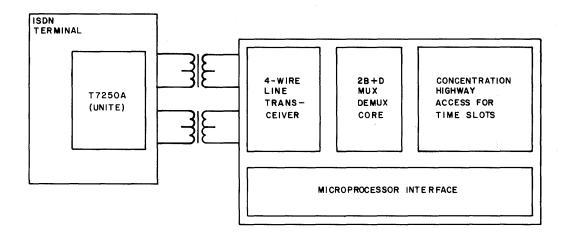

|    | T7250A User Network Interface for Terminal Equipment (UNITE)                | 4-1   |

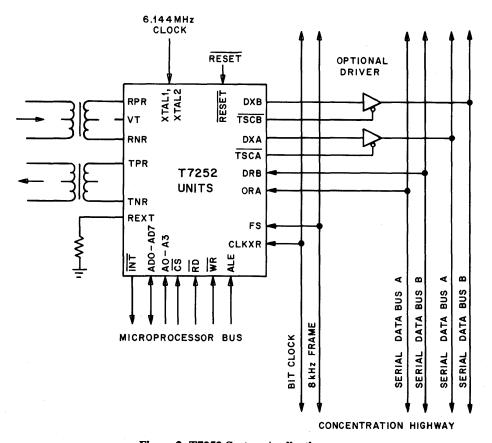

|    | T7252 ISDN Basic Access User Network Interface Termination for              |       |

|    | Switches (UNITS)                                                            |       |

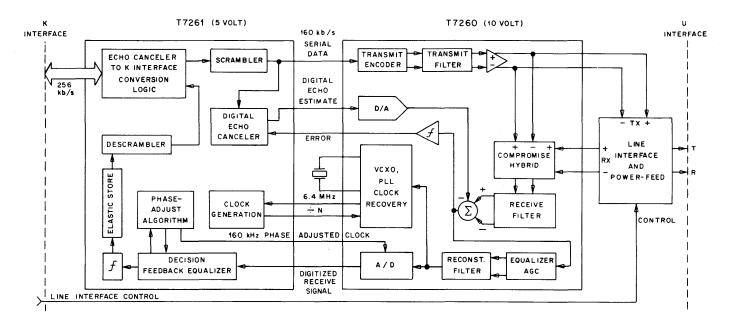

|    | T7260/T7261 U-Interface Basic Access Transceiver Chip Set                   | 4-3   |

| 5. | SIGNAL PROCESSING                                  |     |

|----|----------------------------------------------------|-----|

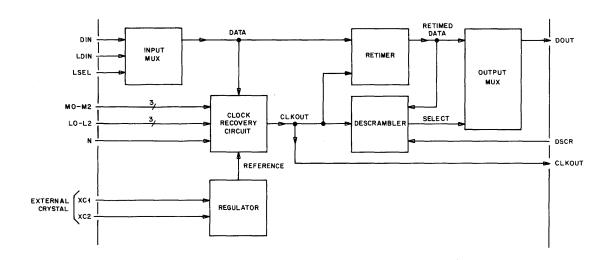

|    | T7032 Clock Recovery Circuit                       | 5-1 |

| 6. | APPLICATION AND TECHNICAL NOTE SUMMARIES           | 6-1 |

| 7. | PACKAGE INFORMATION                                | 7-1 |

| 8. | ORDERING INFORMATION                               | 8-1 |

| 9. | ACRONYMS AND DEFINITIONS                           | 9-1 |

| 1Λ | AT LT COMPONENTS LE EXTRONIC SYSTEMS SALES OFFICES | 10  |

# **ALPHANUMERIC INDEX**

| Custom Codecs                                                                   | 2-87  |

|---------------------------------------------------------------------------------|-------|

| T7000A Digital Encryption Processor                                             | 3-1   |

|                                                                                 | 3-29  |

| T7010 Switched Capacitor Modem                                                  | 3-43  |

| T7011 Modem Interface Chip                                                      | 3-73  |

| T7018/T7019 2400 b/s Modem Chip Set                                             | 3-83  |

| T7032 Clock Recovery Circuit                                                    | 5-1   |

| T7100A X.25 Protocol Controller                                                 | 3-85  |

| T7102 X.25/X.75 Protocol Controller                                             | 3-113 |

| T7110 Synchronous Protocol Data Formatter With Serial Interface (SPYDER-S)      | 3-161 |

|                                                                                 |       |

| T7112 Asynchronous Receiver/Transmitter Interface (ARTI)                        | 3-217 |

| T7250A User Network Interface for Terminal Equipment (UNITE)                    | 4-1   |

| T7252 ISDN Basic Access User Network Interface Termination for Switches (UNITS) | 4-29  |

| T7260/T7262 U-Interface Basic Access Transceiver Chip Set                       | 4-31  |

|                                                                                 | 2-1   |

| T7501 PCM Codec With Filters                                                    | 2-13  |

| T7513 29C13 Equivalent Codec                                                    | 2-25  |

| T7520 High-Precision PCM Codec With Filters                                     | 2-41  |

| T7521 High-Precision PCM Codec Without Filters                                  | 2-57  |

| T7522 High-Precision PCM Codec With Filters (T1 Compatible)                     | 2-71  |

v

#### INTRODUCTION

For more than a century, AT&T has set the standard for information exchange. AT&T innovation and excellence have created the most extensive, efficient, and reliable communications system in the world. This sophisticated voice and data communication system demands components of superior technology, quality, and reliability.

AT&T manufactures integrated circuits specifically designed to meet the needs of the communications market. The strong research and design capabilities of AT&T Bell Laboratories, combined with the high volume, high quality manufacturing capabilities of AT&T Technology Systems, allow us to maintain the leading edge in advanced technology devices.

In this new Information Age, the telephone and the computer are becoming one, and AT&T is building upon this merger with new products and services. New devices have been developed to interface these two complex fields into a highly flexible and reliable network. This catalog contains the technical information on devices used for switching, analog and digital transmission, data transmission and protocol control, integrated services digital network (ISDN) interfacing, and signal processing.

#### **QUALITY AND RELIABILITY**

AT&T standards and stringent processing controls, along with the design and construction techniques developed at AT&T Bell Laboratories, ensure the excellent quality and reliability of AT&T devices. Laboratory tests and field failure data confirm that high quality, reliable products are produced at the component, circuit pack/board, and system levels. Devices are tested by a comparison of the actual electrical, mechanical, or visual properties of the device against what is specified to the user or what is specified as a manufacturing requirement. Quality is determined at a single point in time; reliability is ascertained over a longer period of time.

The engineering quality control (QC) and final inspection (FI) organizations located at each integrated circuit (IC) manufacturing plant perform the actual inspection and testing of devices. After the products have been inspected, the resident quality assurance (QA) organizations audit the results of the tests to determine acceptability. Quality is usually stated in terms of the number of defects contained in an IC population.

Various mechanical tests are performed to ensure the integrity of internal lead bonds and the strength of exterior leads. Packages are visually inspected during assembly to check for defects such as poor alignment of bonds or damaged wires that could be a reliability risk. Assembly shop tests are then repeated by QA and FI on a sample of devices prior to shipment. Tests performed include worst-case conditions, speed, leakage, power supply current, etc. The tests are usually performed at room temperature and/or elevated temperature.

Operational life testing (OLT) is a method of testing for reliability using simulated worst-case field conditions. Mechanical and electrical stress conditions beyond normal specifications are applied to accelerate latent manufacturing defects. Effective screens for mechanical problems are thermal cycling and hot testing, since some mechanical defects are only minimally affected by accelerated stress conditions.

#### HANDLING AND MOUNTING

AT&T products have long life expectancy with a corresponding low failure rate when handling and operating specifications are followed by the user. Operating specifications include product mounting, use, operating limits, power requirements, environmental conditions, and other items specific to the product.

Device temperature specifications are usually given as TA (temperature ambient).

Precaution against static discharge must always be observed since devices may be damaged or destroyed by electrostatic discharge. This includes grounding all personnel and equipment before contact with static-sensitive devices. Circuit packs/boards must be shipped in conductive plastic bags and stored in conductive plastic bags until used. Nonconductive plastic foam or boxes must never be used for device storage.

Integrated circuit devices may be inserted directly into printed circuit boards and mounted in any position. It is acceptable to bend the leads on the opposite side of the board to facilitate assembly. The devices may be soldered to printed circuit boards or inserted into sockets. The devices are not intended for spring-type socket insertion.

In assembly, the device solder bath (fountain) temperature should not exceed 300 °C for a maximum bath time limited to 10 seconds unless otherwise stated. For installation with a soldering iron, the iron temperature (tip) should not exceed 500 °C, and solder time per lead should be limited to 5 seconds unless otherwise stated.

Following completion of assembly and soldering operations, all printed wiring assemblies should be cleaned to remove fingerprints, dust, dirt, grease, excessive flux residue, and other foreign matter. A brush cleaning process using solvents is an acceptable cleaning method, provided only occasional isolated droplets of solvent come in contact with the devices and the component side of the board. The recommended solvents are chlorinated hydrocarbons such as trichloroethylene, 1,1,1-trichloroethane, and perchloroethylene.

Where aggressive fluxes are employed in assembly of printed wiring, total immersion cleaning with high velocity spraying of aqueous solution or solvents such as fluorinated azeotrope is required. Stringent requirements must be placed on the cleanliness of the assemblies to assure removal of ionic residues.

#### **FEATURES**

- AT&T/CCITT compatible

- Pin-selectable μ-law or A-law operation

- Pin-selectable transmit and receive gain

- Variable data rate (128 kHz to 4.096 MHz)

- On-chip voltage reference

- TTL-compatible I/O

- No external components required

- ±5 V supply

- Latch-up free CMOS technology

- Low power dissipation

- □ 20 mW typical power-down

- □ 80 mW typical operation

#### DESCRIPTION

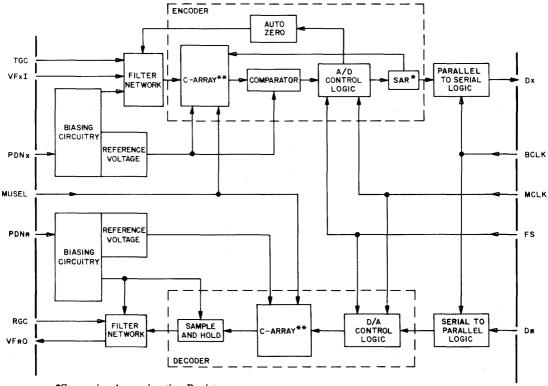

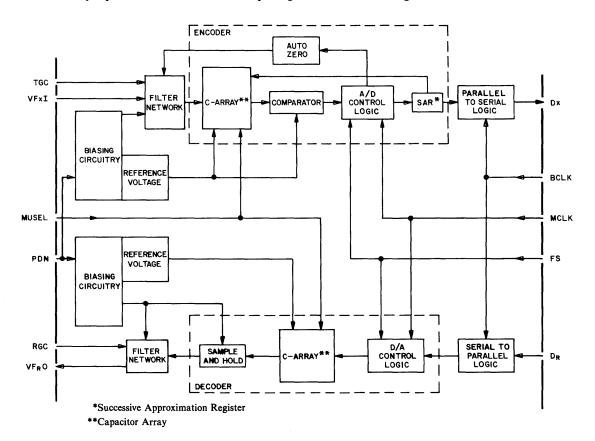

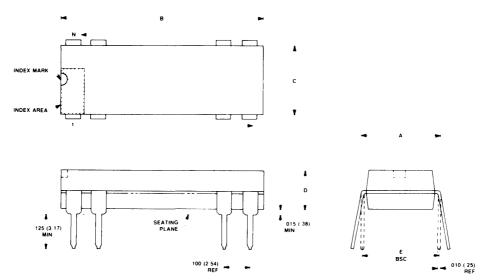

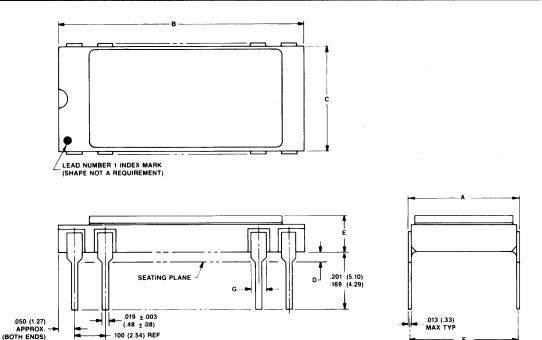

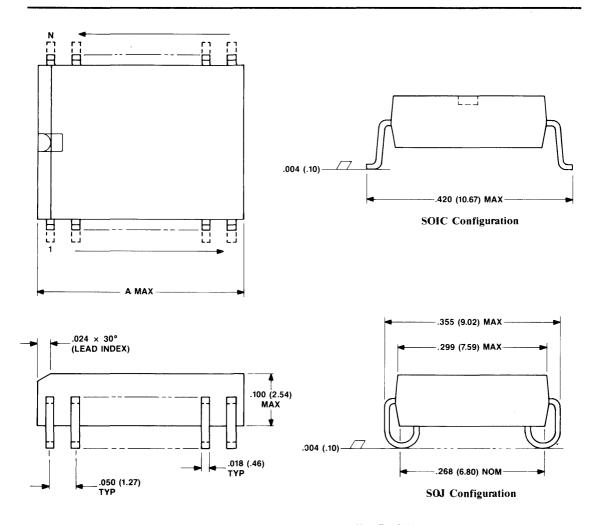

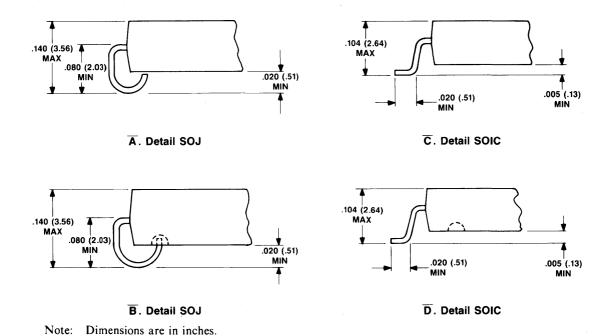

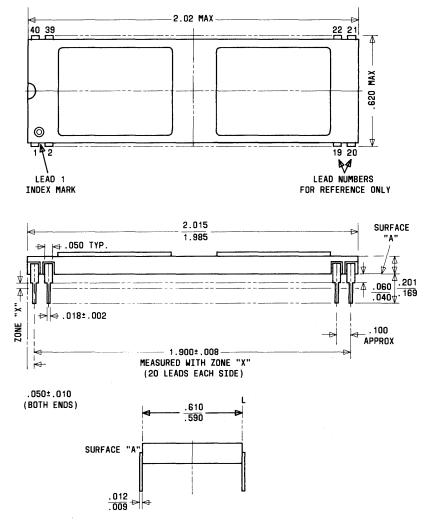

The T7500 PCM Codec With Filters is a single-chip integrated circuit that provides analog-to-digital and digital-to-analog conversion, as well as the transmit and receive filtering necessary to interface a voice telephone circuit to a time division multiplexed system. The T7500 device is available in an 18-pin plastic DIP or a 20-pin plastic small-outline J (SOJ) package for surface mounting.

<sup>\*</sup>Successive Approximation Register

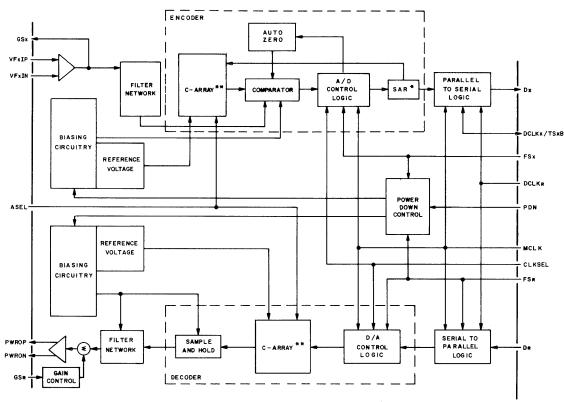

Figure 1. T7500 PCM Codec With Filters Block Diagram

<sup>\*\*</sup>Capacitor Array

#### **USER INFORMATION**

# **Pin Descriptions**

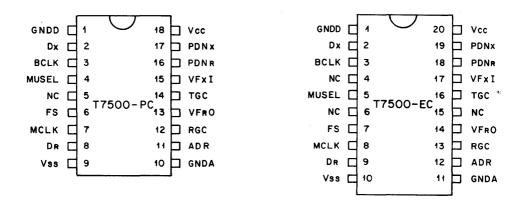

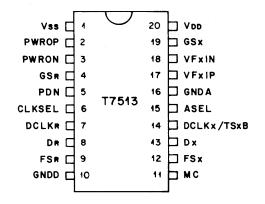

Figure 2. T7500 18-Pin Plastic DIP and 20-Pin Plastic SOJ Pin Function Diagrams

| Table 1. T7500 Pin Descriptions |          |                                                                                                                                               |  |  |  |  |  |

|---------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                          | Туре     | Name/Function                                                                                                                                 |  |  |  |  |  |

| GNDD                            | _        | Ground (Digital).                                                                                                                             |  |  |  |  |  |

| Dx                              | 0        | Data Transmit. Eight-bit μ-law or A-law PCM inverted binary output.                                                                           |  |  |  |  |  |

| BCLK                            | I        | Bit Clock. PCM is transmitted and received at a rate defined by this input clock (128 kHz - 4.096 MHz).                                       |  |  |  |  |  |

| MUSEL                           | I        | $\mu$ -law Select. A high (1) or no connection on this pin results in $\mu$ -law conversion. Apply a low (0) to this pin for A-law encodings. |  |  |  |  |  |

| NC                              | _        | No Connection.                                                                                                                                |  |  |  |  |  |

| FS                              | I        | Frame Synchronization. An 8 kHz timing pulse is applied to this pin to initiate A/D and D/A conversion processes.                             |  |  |  |  |  |

| MCLK                            | I        | Master Clock. 2.048 MHz                                                                                                                       |  |  |  |  |  |

| Dr                              | I        | Data Receive. This is the 8-bit $\mu$ -law or A-law PCM inverted binary input.                                                                |  |  |  |  |  |

| Vss                             | _        | -5 V Supply (±5%).                                                                                                                            |  |  |  |  |  |

| GNDA                            | <b> </b> | Ground (Analog).                                                                                                                              |  |  |  |  |  |

2-2

|        | Table 1. T7500 Pin Descriptions (Continued) |                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|--------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol | Туре                                        | Name/Function                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| ADR    | I                                           | Address. A low (0) or no connection on this pin enables the FS pulse. It is used for channel selection when more than one codec is used on a PCM bus.                                                                                                                           |  |  |  |  |  |  |

| RGC    | I                                           | Receive Gain Control. A low (0) or no connection this pin sets the gain to 0 dB (0 output TLP); a h (1) on this pin sets the receive gain to $+3 \pm 0.1$ d (+3 output TLP). When high, the gain is set with respect to the gain measured at 0 dB setting.                      |  |  |  |  |  |  |

| VFRO   | 0                                           | Voice Frequency Receive Output. The maximum load permitted on this pin is 20 k $\Omega$ in parallel with 50 pF.                                                                                                                                                                 |  |  |  |  |  |  |

| TGC    | I                                           | Transmit Gain Control. A high (1) or no connection on this pin sets the transmit gain to 0 dB (0 input TLP); a low (0) sets the transmit gain to $-3 \pm 0.1$ dB (+3 input TLP). When low, the gain is set with respect to the gain measured at 0 dB setting.                   |  |  |  |  |  |  |

| VFxI   | I                                           | Voice Frequency Transmit Input. Analog input to the transmit filters. The input impedance on this pin is greater than 400 k $\Omega$ .                                                                                                                                          |  |  |  |  |  |  |

| PDNR   | I                                           | Power-Down Receive. A high (1) on this pin causes power-down of receive side. During receive-side power-down, VFRO is grounded through a low impedance and the receive-side analog circuitry is disabled. A low (0) or no connection allows normal receive-side operation.      |  |  |  |  |  |  |

| PDNX   | I                                           | Power-Down Transmit. A high (1) on this pin causes power-down of transmit side. A transmit power-down causes the DX buffer to go into a high-impedance state and all encoder analog circuitry to be disabled. A low (0) or no connection allows normal transmit-side operation. |  |  |  |  |  |  |

| Vcc    | _                                           | 5 V Supply (±5%).                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

#### Overview

The T7500 PCM Codec is a synchronous device with a common master clock and synchronization input that drives both the transmit and receive sections. Device operation requires three logic inputs: MCLK, FS, and BCLK.

On power-up, the codec becomes active only after receiving a FS and ADR signal. The serial transfer of data to DR and from Dx proceeds at a rate determined by BCLK (see Figure 4).

The digital output returns to a high-impedance state upon completion of this process and remains in this state until another set of synchronization and address signals is received. This allows the device to be used with a shared PCM bus (up to 64 channels at 4.096 MHz).

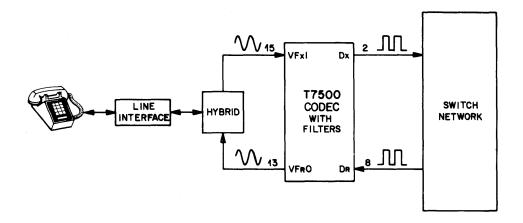

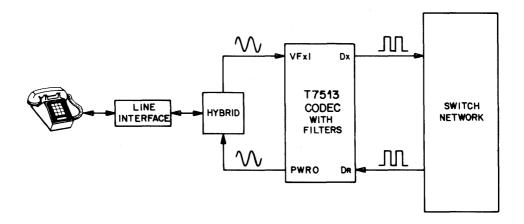

Figure 3. PCM System Block Diagram

The T7500 Codec has a power-down mode that reduces power consumption and heat dissipation when device operation is not required. Two pins are used for this power-down option. A high (1) applied to PDNR disables the receive side of the device; PDNx performs the same function on the transmit side of the device. Each side can be independently disabled. When the receive side is powered down, output VFRO is grounded through a low impedance and all receive-side analog circuitry is disabled. Transmit power-down results in output Dx going into a high-impedance state and all transmit-side analog circuitry being disabled. The device is activated by applying a low (0) to both leads.

This device implements either  $\mu$ -law or A-law PCM encoding. MUSEL is used to determine the type of encoding. Inverted binary format is used for  $\mu$ -law encoding. Alternate digit inversion is used for A-law transmission.

Separate gain controls provide gain settings for the transmit and receive sections. Either 0 dB or -3 dB gain can be selected for the transmit side and either 0 dB or +3 dB for the receive side.

On-chip voltage referencing is provided, eliminating the need for external circuitry and gain trimming.

#### **CHARACTERISTICS**

#### **DC** Characteristics

TA = 0 to 70 °C; VCC = 5 V  $\pm$  5%; VSS = -5 V  $\pm$  5%; GNDA = 0 V; GNDD = 0 V; OTLP, unless otherwise specified. Typical values are for TA = 25 °C and nominal power supply values.

2-4 Network Products

#### **Digital Interface**

| Symbol | Parameter                 | Min | Max | Unit | Test Condition         |

|--------|---------------------------|-----|-----|------|------------------------|

| IIL    | Low-Level Input Current   | -20 | _   | μА   | $GNDD \le VIN \le VIL$ |

| IIH    | High-Level Input Current  | _   | 20  | μΑ   | $VIH \le VIN \le VCC$  |

| VIL    | Input Low Voltage         | _   | 0.8 | V    | _                      |

| VIH    | Input High Voltage        | 2.0 | _   | V    | _                      |

| Vol    | Output Low Voltage        | _   | 0.4 | V    | · <b>-</b>             |

| Vон    | Output High Voltage       | 2.4 |     | V    | _                      |

| Cı     | Digital Input Capacitance | _   | 5   | pF   | -                      |

| IL     | Output Leakage Current    | -50 | 50  | μΑ   | _                      |

#### **Power Dissipation**

All measurements made at fBCLK = 2.048 MHz, outputs loaded.

| Symbol         | Parameter                   | Min   | Тур  | Max    | Unit |

|----------------|-----------------------------|-------|------|--------|------|

| ICC1           | VCC Operating Current       | _     | 8.5  | 15     | mA   |

| ISS1           | VSS Operating Current       | _     | -7.5 | -13    | mA   |

| ICC0           | VCC Power-Down Current      |       | 2.0  | 7.0    | mA   |

| ISS0           | VSS Power-Down Current      | -     | -2.0 | -4.0   | mA   |

| Vcc            | Positive Operating Voltage  | 4.75  | 5    | 5.25*  | V    |

| Vss            | Negative Operating Voltage  | -4.75 | -5   | -5.25* | V    |

| P <sub>1</sub> | Operating Power Dissipation | _     | 80   | 147    | mW   |

| P <sub>0</sub> | Power-Down Dissipation      | -     | 20   | 55     | mW   |

<sup>\*</sup>Absolute maximum ratings are VCC = 7.5 V, VSS = -7.5 V. Exceeding these values may result in permanent internal damage.

# Analog Interface - Transmit Filter Input Stage

| Symbol Parameter |                             | Min | Тур | Max | Unit |

|------------------|-----------------------------|-----|-----|-----|------|

| RI               | Input Resistance @ VFXI     | 0.4 | 1.1 | _   | ΜΩ   |

| Voff             | Input Offset Voltage @ VFXI | _   | _   | 20  | mV   |

| CL               | Load Capacitance @ VFxI     | _   | 20  | 40  | pF   |

# Analog Interface - Receive Filter Driver Amplifier Stage

| Symbol | Parameter                                                   | Min                | Тур | Max              | Unit | Test Conditions        |

|--------|-------------------------------------------------------------|--------------------|-----|------------------|------|------------------------|

| Ro     | Output Resistance @ VFRO for Voice Frequencies              | _                  | 50  | _                | Ω    | _                      |

| Voff   | Output DC Offset @ VFRO                                     | _                  | 50  | -                | mV   | Relative to GNDA       |

| CL     | Load Capacitance @ VFRO                                     | _                  | _   | 50               | pF   | _                      |

| Vo     | Maximum Voltage Output<br>Swing across RL,<br>μ-law (A-law) | -2.229<br>(-2.229) | _   | 2.229<br>(2.229) | V    | RGC = High<br>(+3 TLP) |

|        | μ-ιαw (A-ιαw)                                               | -1.578<br>(-1.572) | _   | 1.578<br>(1.572) | v    | RGC = Low<br>(0 TLP)   |

| RL     | Load Resistance @ VFRO                                      | 20                 | _   | _                | kΩ   | _                      |

# **Timing Characteristics**

|                      | Clock Section              |              |                                         |            |      |  |  |  |  |  |

|----------------------|----------------------------|--------------|-----------------------------------------|------------|------|--|--|--|--|--|

| Symbol               | Parameter                  | Min          | Тур                                     | Max        | Unit |  |  |  |  |  |

| tBCHBCH <sup>1</sup> | Bit Clock Period           | .244         | _                                       | 7.8        | μs   |  |  |  |  |  |

| tBCHBCL              | Bit Clock Pulse Width      | .4tBCHBCH    | .5tBCHBCH                               | .6tBCHBCH  | _    |  |  |  |  |  |

| tMCHMCH <sup>2</sup> | Master Clock Period        | _            | 488                                     | _          | ns   |  |  |  |  |  |

| tMCHMCL              | Master Clock Pulse Width   | .4tMCHMCH    | .5tMCHMCH                               | .6tMCHMCH  | -    |  |  |  |  |  |

|                      | <del> </del>               | Data Section | = = = = = = = = = = = = = = = = = = = = |            |      |  |  |  |  |  |

| Symbol               | Parameter                  | Min          | Тур                                     | Max        | Unit |  |  |  |  |  |

| tFSLMCH              | Sync Set-Up Time<br>Ref MC | 90           | .5tMCHMCH                               | tMCHMCH    | ns   |  |  |  |  |  |

| tFSLAH <sup>3</sup>  | Address Hold Time          | 1.5tBCHBCH   | 3tBCHBCH                                |            | _    |  |  |  |  |  |

| tALFSL               | Address Set-Up Time        | 10           | .5tBCHBCH                               |            | ns   |  |  |  |  |  |

| tFSLFSH <sup>4</sup> | Sync Pulse Width           | 1.5tBCHBCH   | 2tBCHBCH                                | 63         | μs   |  |  |  |  |  |

| tFSLBCL              | Sync Set-Up Time           | 75           | 200                                     | tBCHBCH-50 | ns   |  |  |  |  |  |

| tDRVBCL              | DR Set-Up Time             | 50           | 200                                     | _          | ns   |  |  |  |  |  |

| tBCLDRX              | DR Hold Time               | 50           | 300                                     | _          | ns   |  |  |  |  |  |

| tBCHDXV <sup>5</sup> | DX Delay Time              | 30           | 80                                      | 150        | ns   |  |  |  |  |  |

$<sup>^{1}</sup>BCLK$  ranges from 128 kHz to 4.096 MHz.  $^{2}2.048$  MHz.

$<sup>^{3}</sup>$ Max = constant low.

<sup>&</sup>lt;sup>4</sup>Negative logic sense. <sup>5</sup>DX max load ≤ 300 pF plus 1 medium-power TTL load.

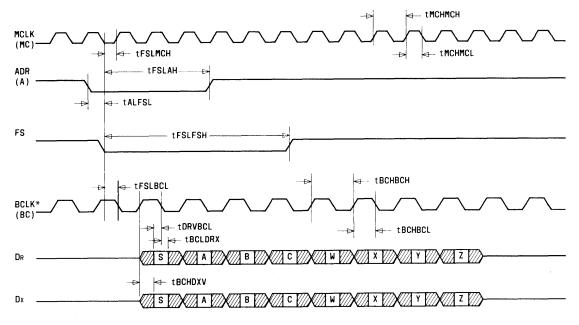

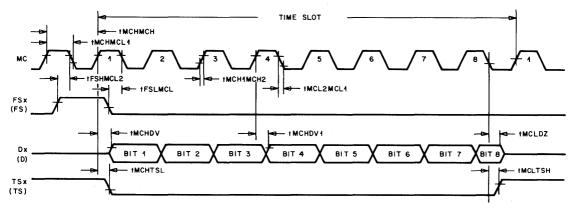

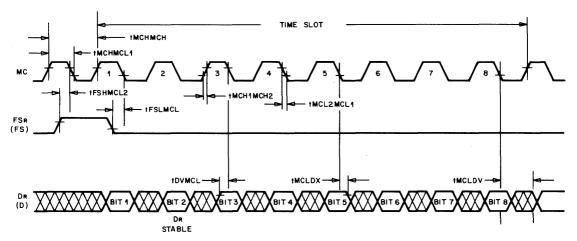

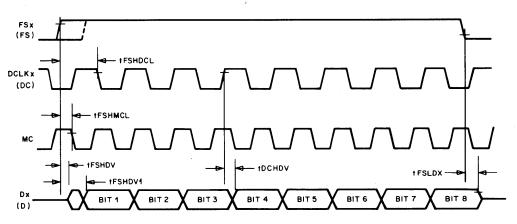

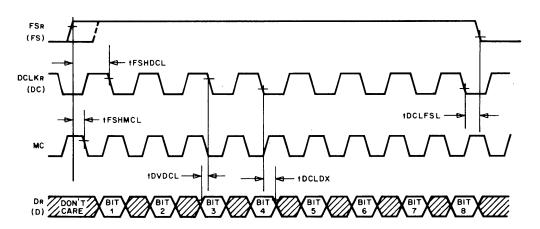

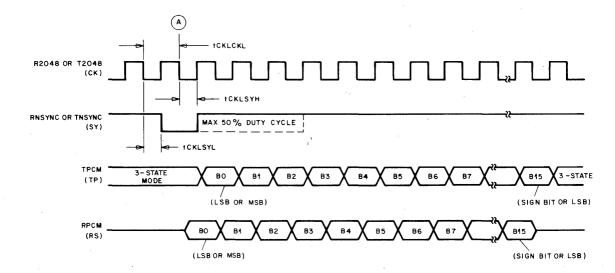

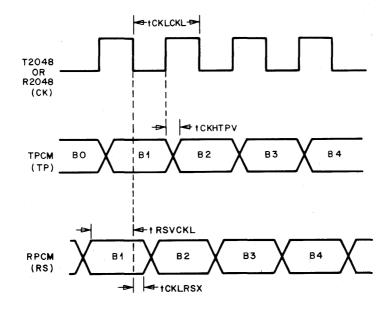

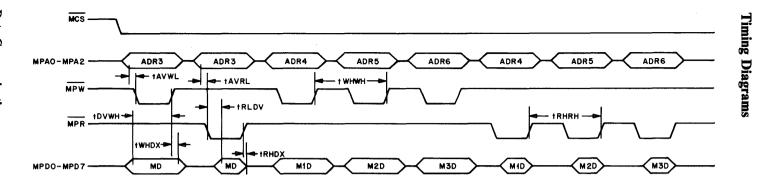

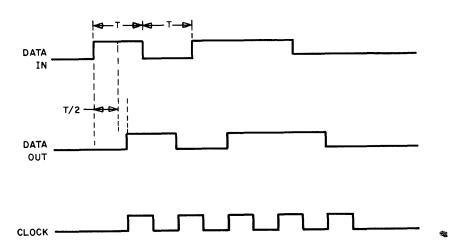

#### **Timing Diagram**

<sup>\*</sup> BCLK RANGES FROM 128 KHz TO 4.096 MHz, IT DETERMINES ADR, FS, DR, AND Dx TIMING

Figure 4. I/O Timing

# AC Characteristics - Transmission Parameters

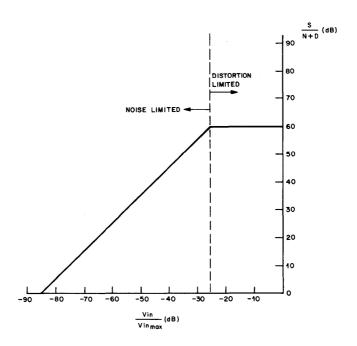

#### Gain and Dynamic Range

| Symbol | Parameter                                            | Min   | Тур        | Max   | Unit | Test Conditions           |

|--------|------------------------------------------------------|-------|------------|-------|------|---------------------------|

| GE     | Encoder Milliwatt Response (Transmit Gain Tolerance) |       |            |       |      | Signal input = .7746 Vrms |

|        |                                                      |       |            |       |      |                           |

|        | μ-law                                                | -0.15 | $\pm 0.08$ | 0.15  | dBm0 | VCC and VSS are ± 5 %     |

|        | A-law                                                | -0.18 | ±0.08      | ±0.18 | dBm0 | TA = 0 to 70 °C           |

| GD     | Digital Milliwatt Response                           |       |            |       |      |                           |

|        | (Receive Gain Tolerance)                             |       |            |       |      |                           |

|        | μ-law                                                | -0.15 | ±0.08      | 0.15  | dBm0 | VCC and VSS are ± 5 %     |

|        | A-law                                                | -0.18 | ±0.08      | 0.18  | dBm0 | TA = 0 to 70 °C           |

Gain Tracking - Reference Level = 1.02 kHz, 0 dBm0

| Symbol           | Parameter                     | Min   | Max  | Unit | Test Conditions |

|------------------|-------------------------------|-------|------|------|-----------------|

| GTXμ             | Transmit Gain Tracking Error: | -0.25 | 0.25 | dB   | 3 to -37 dBm0   |

|                  | Sinusoidal Input, μ-law       | -0.50 | 0.50 | dB   | -37 to -50 dBm0 |

| GTXA             | Transmit Gain Tracking Error: | -0.25 | 0.25 | dB   | 3 to -37 dBm0   |

|                  | Sinusoidal Input, A-law       | -0.50 | 0.50 | dB   | -37 to -50 dBm0 |

| GTR <sub>µ</sub> | Receive Gain Tracking Error:  | -0.25 | 0.25 | dB   | 3 to -37 dBm0   |

|                  | Sinusoidal Input, μ-law       | -0.50 | 0.50 | dB   | -37 to -50 dBm0 |

| GTRA             | Receive Gain Tracking Error:  | -0.25 | 0.25 | dB   | 3 to -37 dBm0   |

|                  | Sinusoidal Input, A-law       | -0.50 | 0.50 | dB   | -37 to -50 dBm0 |

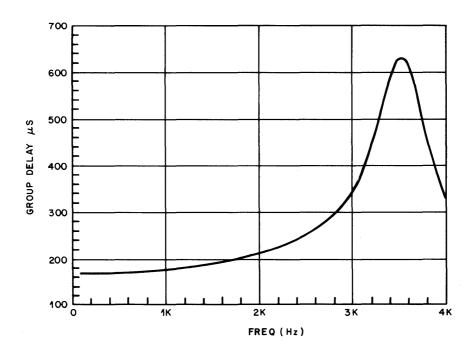

#### Distortion

| Symbol | Parameter                                                         | Min                        | Тур                                | Max        | Unit                       | Test Conditions                                                                    |

|--------|-------------------------------------------------------------------|----------------------------|------------------------------------|------------|----------------------------|------------------------------------------------------------------------------------|

| Dxs    | Transmit Signal to Distortion:<br>Sinusoidal Input, μ-law (A-law) | 36(35)<br>30(29)<br>25(25) | _                                  | _          | dB<br>dB<br>dB             | 0 ≤ VFXI ≤ -30 dBm0<br>-40 dBm0<br>-45 dBm0<br>(Input = 1.02 kHz)                  |

| DRS    | Receive Signal to Distortion:<br>Sinusoidal Input, μ-law (A-law)  | 36(35)<br>30(29)<br>25(25) | _                                  | _          | dB<br>dB<br>dB             | 0 ≤ DR ≤ -30 dBm0<br>-40 dBm0<br>-45 dBm0<br>(Input = 1.02 kHz)                    |

| DxsF   | Transmit Single Frequency: Distortion Products                    | _                          | _                                  | -28<br>-40 | dBm0<br>dBm0               | $0 \le Input \le 2 MHz$<br>$0 \le Input \le 3.4 kHz$                               |

| DRSF   | Receive Single Frequency: Distortion Products                     |                            | _                                  | -28<br>-40 | dBm0<br>dBm0               | $0 \le \text{Input} \le 2 \text{ MHz}$<br>$0 \le \text{Input} \le 3.4 \text{ kHz}$ |

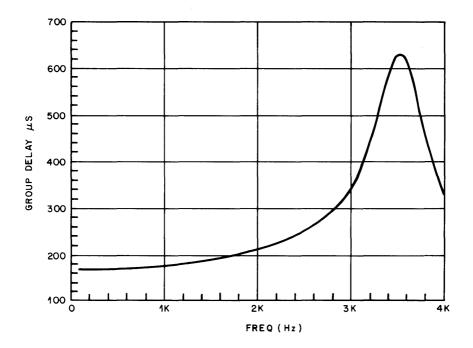

| DXD    | Transmit Absolute Delay                                           | _                          | 340                                | _          | μs                         | _                                                                                  |

| DRD    | Receive Absolute Delay                                            | _                          | 240                                | _          | μs                         | -                                                                                  |

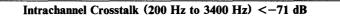

| DDAA   | Delay Distortion:<br>Analog-to-Analog                             | _                          | 250<br>60<br>20<br>20<br>50<br>220 |            | μs<br>μs<br>μs<br>μs<br>μs | f = 500 Hz<br>f = 1 kHz<br>f = 1.5 kHz<br>f = 2 kHz<br>f = 2.5 kHz<br>f = 3 kHz    |

2-8

#### Noise

| Symbol | Parameter                                                           | Min | Тур | Max             | Unit             | Test Conditions                                                                                  |

|--------|---------------------------------------------------------------------|-----|-----|-----------------|------------------|--------------------------------------------------------------------------------------------------|

| Fxc    | Transmit Idle Channel Noise:<br>C-Message Weighted                  | _   | 14  | 18<br>23        | dBrnC0<br>dBrnC0 | μ-law<br>A-law                                                                                   |

| FRC    | Receive Idle Channel Noise:<br>C-Message Weighted                   | _   | 9   | 13<br>15        | dBrnC0<br>dBrnC0 | μ-law<br>A-law                                                                                   |

| FXP    | Transmit Idle Channel Noise:<br>Phosphometric Weighted              | _   | -69 | -67             | dBm0p            | _                                                                                                |

| FRP    | Receive Idle Channel Noise:<br>Phosphometric Weighted               | _   | -81 | <del>-7</del> 5 | dBm0p            | _                                                                                                |

| PSRXCC | VCC Power Supply Rejection:<br>Transmit Channel                     | -30 | -35 | _               | dB               | Idle channel; 100<br>mVpp, 1.02 kHz<br>signal on dc supply;<br>measured 1.02 kHz<br>signal at DX |

| PSRXSS | Vss Power Supply Rejection:<br>Transmit Channel                     | -30 | -35 | _               | dB               | Idle channel; 100<br>mVpp, 1.02 kHz<br>signal on dc supply;<br>measured 1.02 kHz<br>signal at DX |

| PSRRCC | VCC Power Supply Rejection:<br>Receive Channel                      | -30 | -35 | _               | dB               | Idle channel; 100<br>mVpp, 1.02 kHz<br>signal on dc supply;<br>measured 1.02 kHz<br>at VFRO      |

| PSRRSS | VSS Power Supply Rejection:<br>Receive Channel                      | -30 | -35 | _               | dB               | Idle channel; 100<br>mVpp, 1.02 kHz<br>signal on dc supply;<br>measured 1.02 kHz<br>at VFRO      |

| FCXR   | Crosstalk: Transmit to Receive, Single-Ended Outputs, μ-law (A-law) | _   |     | -71<br>(-70)    | dB               | VFxI = 0 dBm0;<br>1.02 kHz signal<br>measured at<br>VFRO; DR = idle<br>code                      |

| FCRX   | Crosstalk: Receive to Transmit, Single-Ended Outputs, μ-law (A-law) |     | _   | -71<br>(-70)    | dB               | DR = 0 dBm0;<br>VFXI = GNDA;<br>1.02 kHz signal<br>measured at DX                                |

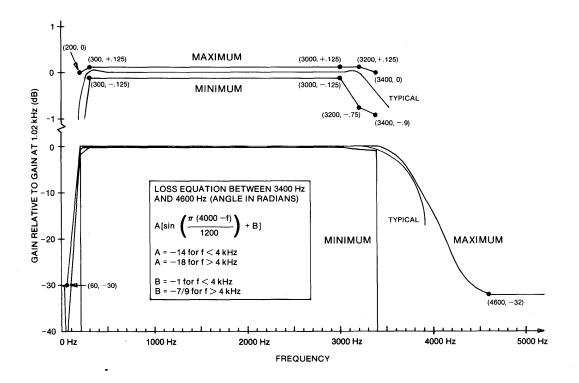

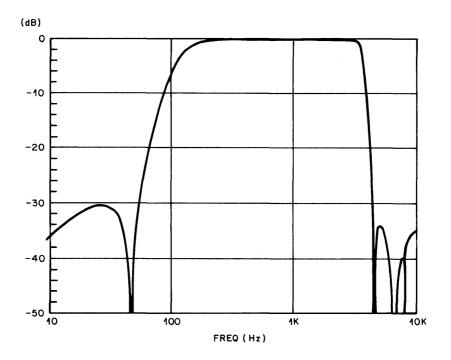

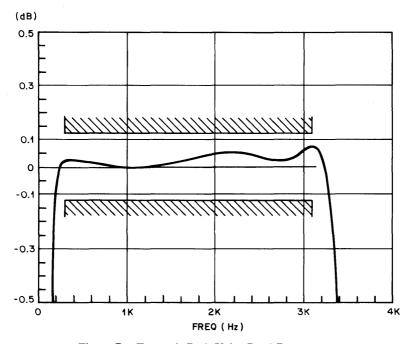

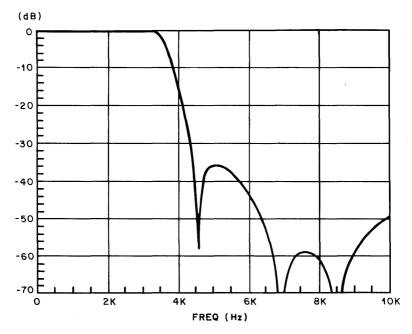

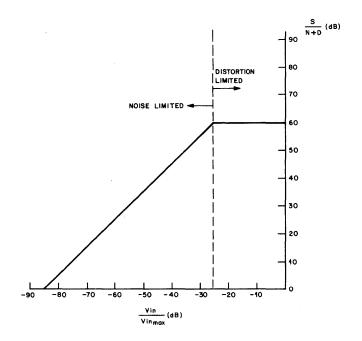

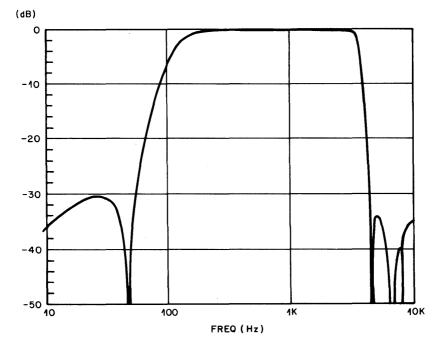

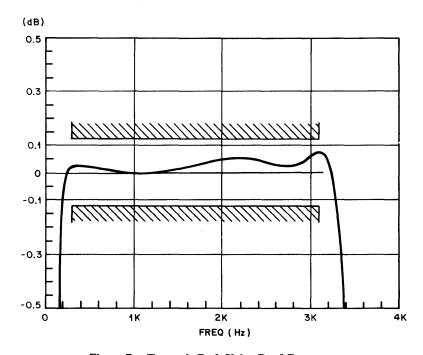

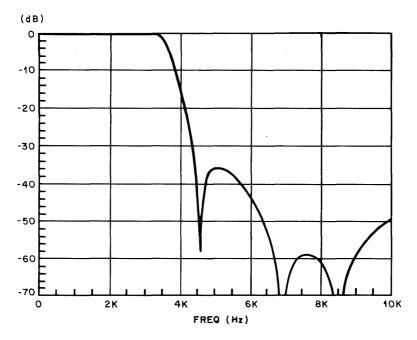

#### **Transmit Filter Transfer Characteristics**

| Transmit Gain Relative to Gain at 1.02 kHz (GRX)* |        |       |       |      |  |  |  |  |

|---------------------------------------------------|--------|-------|-------|------|--|--|--|--|

| Frequency                                         | Min    | Тур   | Max   | Unit |  |  |  |  |

| 16.67 Hz                                          | _      | -35   | -30   | dB   |  |  |  |  |

| 50 Hz                                             | _      | -33   | -30   | dB   |  |  |  |  |

| 60 Hz                                             | _      | -40   | -30   | dB   |  |  |  |  |

| 200 Hz                                            | -1.8   | -0.5  | 0     | dB   |  |  |  |  |

| 300 to 3000 Hz                                    | -0.125 | ±0.04 | 0.125 | dB   |  |  |  |  |

| 3140 Hz                                           | -0.57  | 0.01  | 0.125 | dB   |  |  |  |  |

| 3380 Hz                                           | -0.885 | -0.7  | 0.015 | dB   |  |  |  |  |

| 3980 Hz                                           | _      | -15.6 | -13.3 | dB   |  |  |  |  |

| 4600 Hz and above                                 | _      | _     | -32   | dB   |  |  |  |  |

<sup>\*0</sup> dBm0 signal input at VFxI.

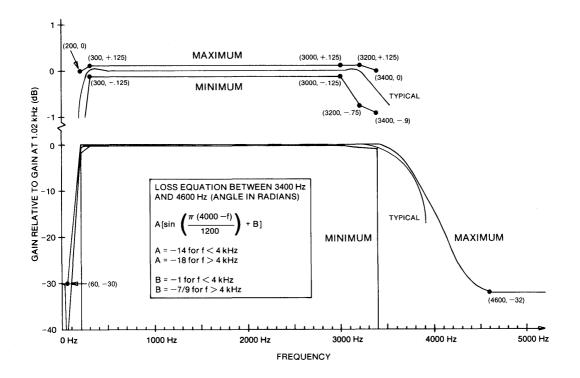

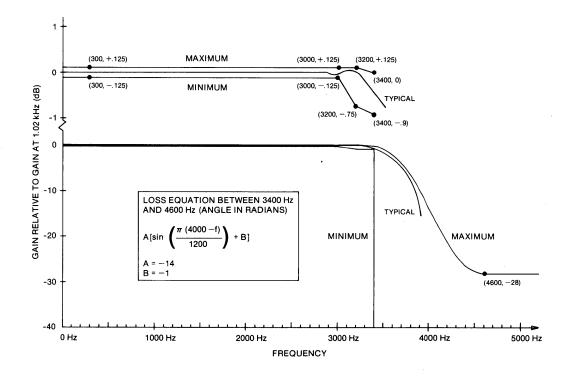

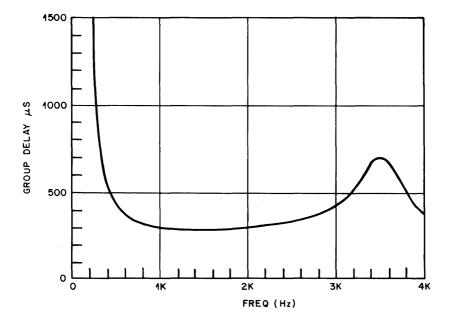

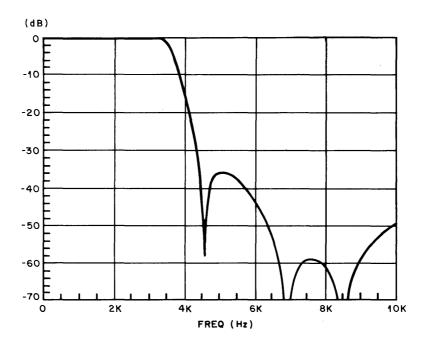

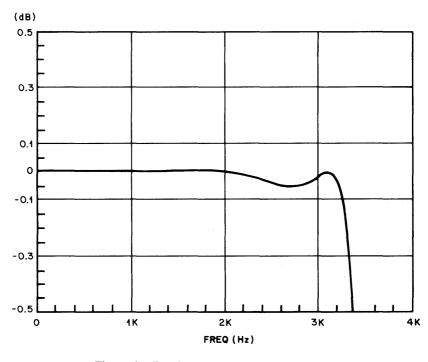

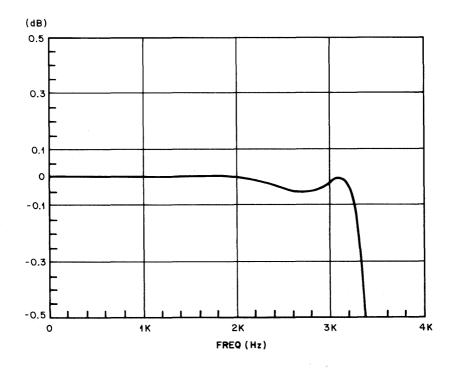

Figure 5. Transmit Filter Characteristics

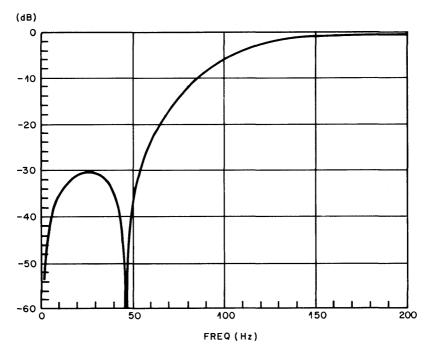

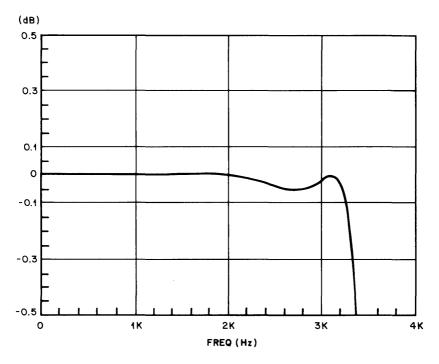

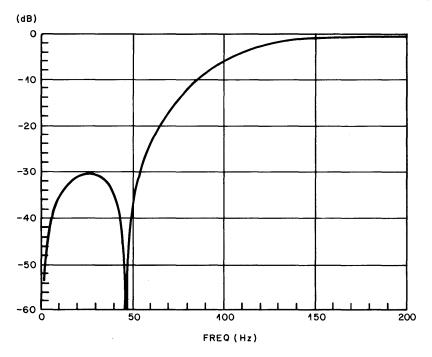

#### **Receive Filter Transfer Characteristics**

| Receive Gain Relative to Gain at 1.02 kHz (GRR)* |        |       |        |      |  |  |  |  |

|--------------------------------------------------|--------|-------|--------|------|--|--|--|--|

| Frequency                                        | Min    | Тур   | Max    | Unit |  |  |  |  |

| Below 3000 Hz                                    | -0.125 | ±0.04 | 0.125  | dB   |  |  |  |  |

| 3140 Hz                                          | -0.57  | ±0.04 | 0.125  | dB   |  |  |  |  |

| 3380 Hz                                          | -0.885 | -0.58 | -0.015 | dB   |  |  |  |  |

| 3980 Hz                                          | _      | -15.7 | -13.3  | dB   |  |  |  |  |

| 4600 Hz and above                                | _      |       | -28    | dB   |  |  |  |  |

<sup>\*0</sup> dBm0 signal input at DR.

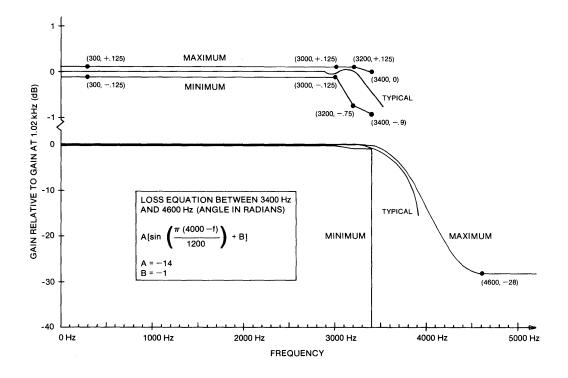

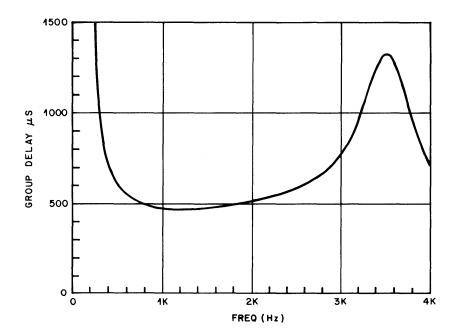

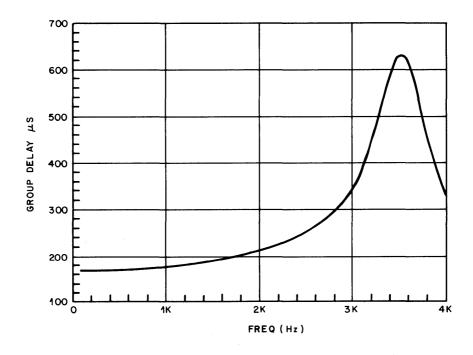

Figure 6. Receive Filter Characteristics

#### **FEATURES**

- AT&T/CCITT compatible

- Pin-selectable μ-law or A-law operation

- Pin-selectable transmit and receive gain

- Variable data rate (128 kHz to 4.096 MHz)

- On-chip voltage reference

- TTL-compatible I/O

- No external components required

- ±5 V supply

- Latch-up free CMOS technology

- Low power dissipation

- □ 20 mW typical power-down

- □ 80 mW typical operation

#### **DESCRIPTION**

The T7501 PCM Codec With Filters is a single-chip integrated circuit that provides analog-to-digital and digital-to-analog conversion, as well as the transmit and receive filtering necessary to interface a voice telephone circuit to a time division multiplexed system. The T7501 device is available in an 18-pin plastic DIP or a 20-pin plastic small outline J (SOJ) package for surface mounting.

Figure 1. T7501 PCM Codec With Filters Block Diagram

#### **USER INFORMATION**

# **Pin Descriptions**

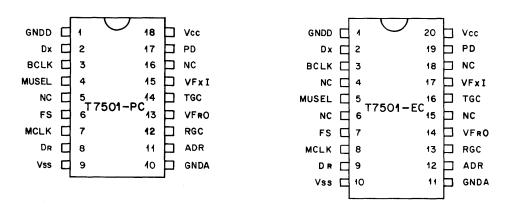

Figure 2. T7501 18-Pin Plastic DIP and 20-Pin Plastic SOJ Pin Function Diagrams

| Table 1. T7501 Pin Descriptions |      |                                                                                                                                               |  |  |  |  |

|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                          | Туре | Name/Function                                                                                                                                 |  |  |  |  |

| GNDD                            | _    | Ground (Digital).                                                                                                                             |  |  |  |  |

| Dx                              | 0    | Data Transmit. Eight-bit μ-law or A-law PCM inverted binary output.                                                                           |  |  |  |  |

| BCLK                            | I    | Bit Clock. PCM is transmitted and received at a rate defined by this input clock (128 kHz - 4.096 MHz).                                       |  |  |  |  |

| MUSEL                           | I    | $\mu$ -Law Select. A high (1) or no connection on this pin results in $\mu$ -law conversion. Apply a low (0) to this pin for A-law encodings. |  |  |  |  |

| NC                              | _    | No Connection.                                                                                                                                |  |  |  |  |

| FS                              | I    | Frame Synchronization. An 8 kHz timing pulse is applied to this pin to initiate A/D and D/A conversion processes.                             |  |  |  |  |

| MCLK                            | I    | Master Clock. 2.048 MHz                                                                                                                       |  |  |  |  |

| Dr                              | I    | Data Receive. This is the 8-bit $\mu$ -law or A-law PCM inverted binary input.                                                                |  |  |  |  |

| Vss                             | _    | -5 V Supply (± 5%).                                                                                                                           |  |  |  |  |

| GNDA                            |      | Ground (Analog).                                                                                                                              |  |  |  |  |

2-14

|        | Table | 1. T7501 Pin Descriptions (Continued)                                                                                                                                                                                                                                                                                                                    |

|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | Туре  | Name/Function                                                                                                                                                                                                                                                                                                                                            |

| ADR    | I     | Address. A low (0) on this pin enables the FS pulse. It is used for channel selection when more than one codec is used on a PCM bus. A high (1) or no connection on this pin disables FS.                                                                                                                                                                |

| RGC    | I     | Receive Gain Control. A low (0) on this pin sets the gain to 0 dB (0 output TLP); a high (1) or no connection on this pin sets the receive gain to +3 ±0.1 dB (+3 output TLP). When high, the gain is set with respect to the gain measured at 0 dB setting.                                                                                             |

| VFRO   | 0     | Voice Frequency Receive Output. The maximum load permitted on this pin is 20 k $\Omega$ in parallel with 50 pF.                                                                                                                                                                                                                                          |

| TGC    | I     | Transmit Gain Control. A high (1) or no connection on this pin sets the transmit gain to 0 dB (0 input TLP); a low (0) sets the transmit gain to $-3 \pm 0.1$ dB (+3 input TLP). When low, the gain is set with respect to the gain measured at the 0 dB setting.                                                                                        |

| VFxI   | I     | Voice Frequency Transmit Input. Analog input to the transmit filters. The input impedance on this pin is greater than 400 k $\Omega$ .                                                                                                                                                                                                                   |

| NC     |       | No Connection.                                                                                                                                                                                                                                                                                                                                           |

| PD     | I     | Power-Down. A high (1) or no connection on this pin causes power-down. The power-down causes the Dx buffer to go into a high-impedance state and all encoder analog circuitry to be disabled, VFRO to be grounded through a low impedance, and the receive-side analog circuitry to be disabled. A low (0) allows normal transmit and receive operation. |

| Vcc    | _     | 5 V Supply (±5%).                                                                                                                                                                                                                                                                                                                                        |

#### Overview

The T7501 PCM Codec is a synchronous device with a common master clock and synchronization input that drives both the transmit and receive sections. Device operation requires three logic inputs: MCLK, FS, and BCLK.

On power-up, the codec becomes active only after receiving a FS and ADR signal. The serial transfer of data to DR and from DX proceeds at a rate determined by BCLK (see Figure 4).

The digital output returns to a high-impedance state upon completion of this process and remains in this state until another set of synchronization and address signals is received. This allows the device to be used with a shared PCM bus (up to 64 channels at 4.096 MHz).

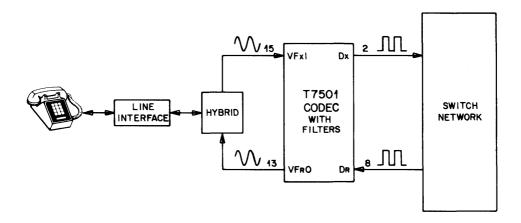

Figure 3. PCM System Block Diagram

The T7501 Codec has a power-down mode that reduces power consumption and heat dissipation when device operation is not required. A logic 1 applied to PD disables the receive and transmit functions of the device. When the device is powered down, output VFRO is grounded through a low impedance and all receive-side analog circuitry is disabled. Transmit power-down results in output DX going into a high-impedance state and all transmit-side analog circuitry being disabled.

A low (0) applied to PD activates the device. The analog transmit circuitry requires a setting time of 50 ms to guarantee that the DC offset will be less than 16 least significant bits. The 16 LSBs correspond to the first  $\mu$ -law chord boundary.

This device implements either  $\mu$ -law or A-law PCM encoding. MUSEL is used to determine the type of encoding. Inverted binary format is used for  $\mu$ -law encoding. Alternate digit inversion is used for A-law transmission.

Separate gain controls provide gain settings for the transmit and receive sections. Either 0 dB or -3 dB gain can be selected for the transmit side and either 0 dB or +3 dB for the receive side.

On-chip voltage referencing is provided, eliminating the need for external circuitry and gain trimming.

#### **CHARACTERISTICS**

#### **DC** Characteristics

TA = 0 to 70 °C; VCC =  $5 \pm 5\%$ ; VSS =  $-5 \text{ V} \pm 5\%$ ; GNDA = 0 V; GNDD = 0 V; OTLP, unless otherwise specified. Typical values are for TA =  $25 \, ^{\circ}\text{C}$  and nominal power supply values.

2-16 Network Products

#### **Digital Interface**

| Symbol | Parameter                 | Min | Max | Unit | Test Condition         |

|--------|---------------------------|-----|-----|------|------------------------|

| IIL    | Low-Level Input Current   | -20 | _   | μΑ   | $GNDD \le VIN \le VIL$ |

| IIH    | High-Level Input Current  | _   | 20  | μΑ   | $VIH \le VIN \le VCC$  |

| VIL    | Input Low Voltage         | _   | 0.8 | V    | _                      |

| Vih    | Input High Voltage        | 2.0 | _   | V    | _                      |

| Vol    | Output Low Voltage        | _   | 0.4 | V    | _                      |

| Vон    | Output High Voltage       | 2.4 | _   | V    | _                      |

| Cı     | Digital Input Capacitance | _   | 5   | pF   | _                      |

| IL     | Output Leakage Current    | -50 | 50  | μΑ   | _                      |

# **Power Dissipation**

All measurements made at fBCLK = 2.048 MHz, outputs loaded.

| Symbol     | Parameter                   | Min   | Тур  | Max    | Unit |

|------------|-----------------------------|-------|------|--------|------|

| ICC1       | VCC Operating Current       | _     | 8.5  | 15     | mA   |

| ISS1       | VSS Operating Current       | _     | -7.5 | -13    | mA   |

| Icco       | VCC Power-Down Current      | _     | 2.0  | 7.0    | mA   |

| ISS0       | VSS Power-Down Current      | -     | -2.0 | -4.0   | mA   |

| Vcc        | Positive Operating Voltage  | 4.75  | 5    | 5.25*  | V    |

| Vss        | Negative Operating Voltage  | -4.75 | -5   | -5.25* | V    |

| <b>P</b> 1 | Operating Power Dissipation |       | 80   | 147    | mW   |

| Po         | Power-Down Dissipation      | _     | 20   | 55     | mW   |

<sup>\*</sup>Absolute maximum ratings are VCC = 7.5 V, VSS = -7.5 V. Exceeding these values may result in permanent internal damage.

# Analog Interface - Transmit Filter Input Stage

| Symbol | Parameter                   | Min | Тур | Max | Unit |

|--------|-----------------------------|-----|-----|-----|------|

| Rı     | Input Resistance @ VFxI     | 0.4 | 1.1 | _   | МΩ   |

| Voff   | Input Offset Voltage @ VFxI | _   | _   | 20  | mV   |

| CL     | Load Capacitance @ VFXI     | _   | 20  | 40  | pF   |

# Analog Interface - Receive Filter Driver Amplifier Stage

| Symbol | Parameter                                             | Min                | Тур      | Max              | Unit | Test Conditions        |

|--------|-------------------------------------------------------|--------------------|----------|------------------|------|------------------------|

| Ro     | Output Resistance @ VFRO for Voice Frequencies        | _                  | 50       | _                | Ω    | _                      |

| Voff   | Output DC Offset @ VFRO                               | _                  | 50       | _                | mV   | Relative to GNDA       |

| CL     | Load Capacitance @ VFRO                               |                    | _        | 50               | pF   | _                      |

| Vo     | Maximum Voltage Output Swing across RL, μ-law (A-law) | -2.229<br>(-2.229) | _        | 2.229<br>(2.229) | V    | RGC = High<br>(+3 TLP) |

|        | μ-law (A-law)                                         | -1.578<br>(-1.572) | <u>-</u> | 1.578<br>(1.572) | V    | RGC = Low<br>(0 TLP)   |

| RL     | Load Resistance @ VFRO                                | 20                 | _        | _                | kΩ   | _                      |

# **Timing Characteristics**

|                      | and the second s | Clock Section |           |            |      |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|------------|------|--|--|--|--|

| Symbol               | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min           | Тур       | Max        | Unit |  |  |  |  |

| tBCHBCH <sup>1</sup> | Bit Clock Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .244          | _         | 7.8        | μs   |  |  |  |  |

| tBCHBCL              | Bit Clock Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .4tBCHBCH     | .5tBCHBCH | .6tBCHBCH  | _    |  |  |  |  |

| tMCLMCL <sup>2</sup> | Master Clock Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | 488       | _          | ns   |  |  |  |  |

| tMCLMCH              | Master Clock Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .4tMCLMCL     | .5tMCLMCL | .6tMCLMCL  | -    |  |  |  |  |

|                      | Data Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |           |            |      |  |  |  |  |

| Symbol               | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min           | Тур       | Max        | Unit |  |  |  |  |

| tFSLMCL              | Sync Set-Up Time<br>Ref MC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 90            | .5tMCLMCL | tMCLMCL    | ns   |  |  |  |  |

| tFSLAH <sup>3</sup>  | Address Hold Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.5tBCHBCH    |           | _          | _    |  |  |  |  |

| tALFSL               | Address Set-Up Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10            | .5tBCHBCH |            | ns   |  |  |  |  |

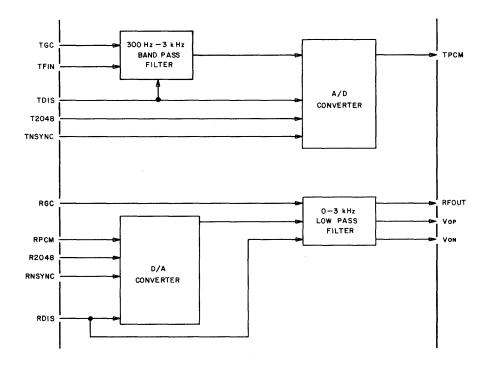

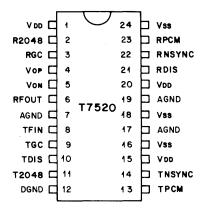

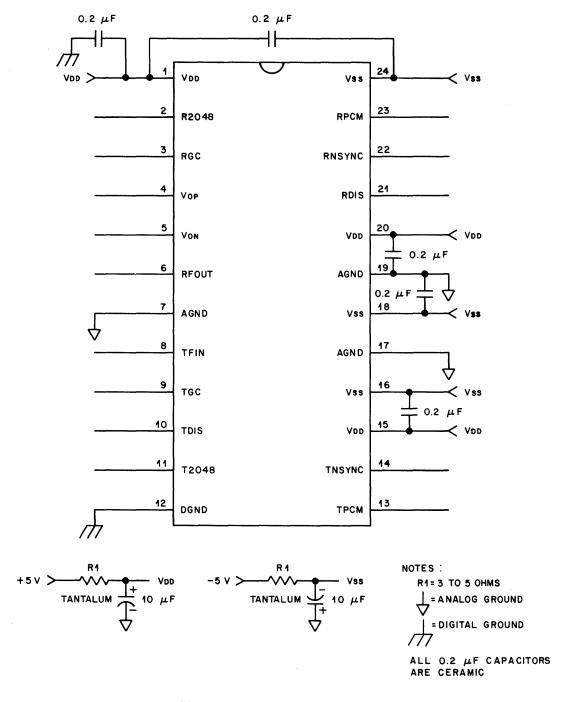

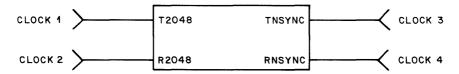

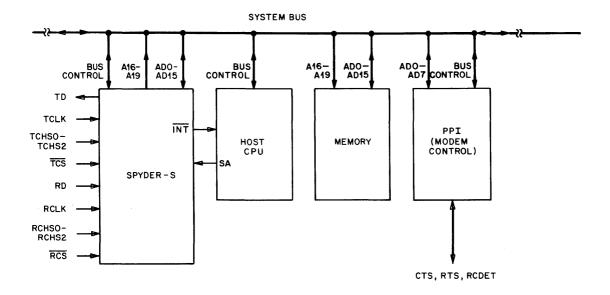

| tFSLFSH <sup>4</sup> | Sync Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.5tBCHBCH    | 2tBCHBCH  | 63         | μs   |  |  |  |  |