# PM-DL11W Serial Line Interface Manual

# PM-DL11W Serial Line Interface Manual

## PM-DL11W Serial Line Interface Manual

October 1979 - Revision D

Copyright (C) Plessey Peripheral Systems

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE 52648

CODE IDENT NO. DWG NO.

SCALE

REV

SHEET 0-0

|  |  | , |  |

|--|--|---|--|

|  |  |   |  |

### **Contents**

### SECTION 1 - GENERAL INFORMATION

| 1.1<br>1.2<br>1.3 | INTRODUCTION                                | 1-1<br>1-2<br>1-2 |

|-------------------|---------------------------------------------|-------------------|

|                   | SECTION 2 - INSTALLATION                    |                   |

| 2.1               | UNPACKING AND INSPECTION                    |                   |

| 2.3               | BOARD INSTALLATION                          |                   |

|                   | OPTIONS                                     |                   |

|                   | SECTION 3 - FUNCTIONAL DESCRIPTION          |                   |

| 3.1               | SERIAL LINE INTERFACE                       |                   |

| 3.2               |                                             |                   |

| 3.3<br>3.4        |                                             |                   |

|                   | DEVICE REGISTERS                            |                   |

| J.J               | 3.5.1 RECEIVER STATUS REGISTER              |                   |

|                   | 3.5.2 RECEIVER DATA BUFFER                  |                   |

|                   | 3.5.3 TRANSMITTER STATUS REGISTER           | 3-8               |

|                   | 3.5.4 TRANSMITTER DATA BUFFER               | 3-9               |

|                   | 3.5.5 CLOCK STATUS REGISTER                 |                   |

| 3.6               | PDP-11/20 MOD-MICRO 1 MOD                   | 3-10              |

|                   | SECTION 4 - MAINTENANCE AND TROUBLESHOOTING |                   |

|                   |                                             |                   |

|                   | PRINTED CIRCUIT BOARD CLEANING              |                   |

| 4.2               | TROUBLESHOOTING                             | 4-1               |

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

SCALE

CODE IDENT NO. DWG NO.

52648

REV

MA 701320

SHEET 0-1

## **Tables**

| Table l | L-1: | Power Requirements       | -3  |

|---------|------|--------------------------|-----|

| Table 2 | 2-1: | UART Function Switches   | -3  |

| Table 2 | 2-2: | SW2 Switch Settings      | -4  |

| Table 2 | 2-3: | Vector Address Selection | -5  |

| Table 2 | 2-4: | SW4 Address Selection    | -6  |

| Table 2 | 2-5: | Jumper Priority Chart    | -13 |

# **Figures**

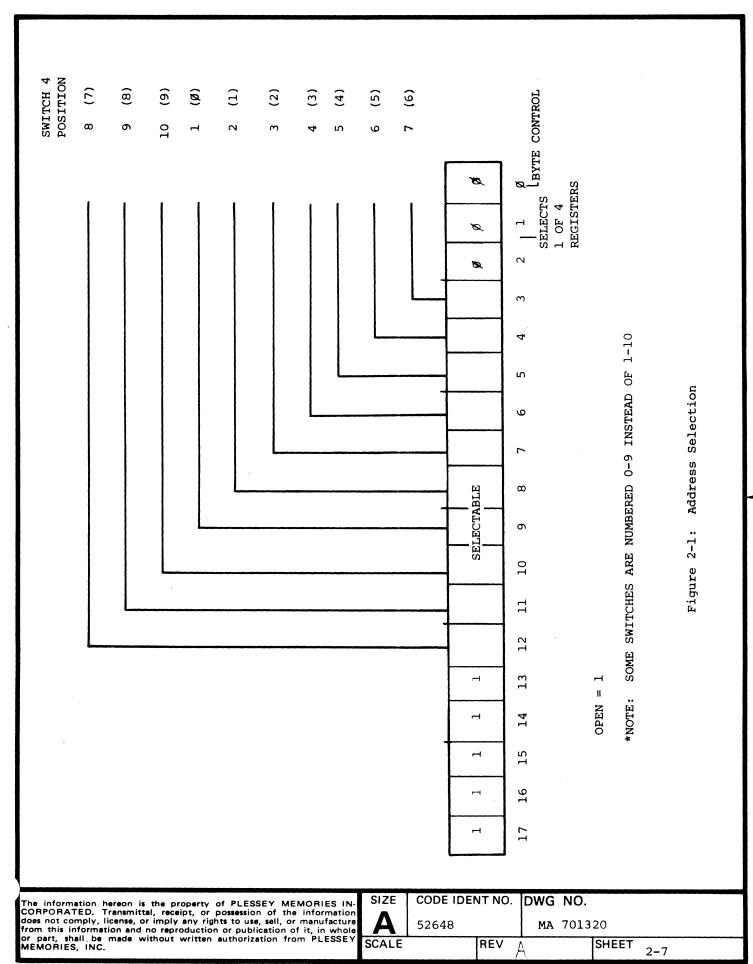

| Figure 2-1: | Address Selection                      | 2-7  |

|-------------|----------------------------------------|------|

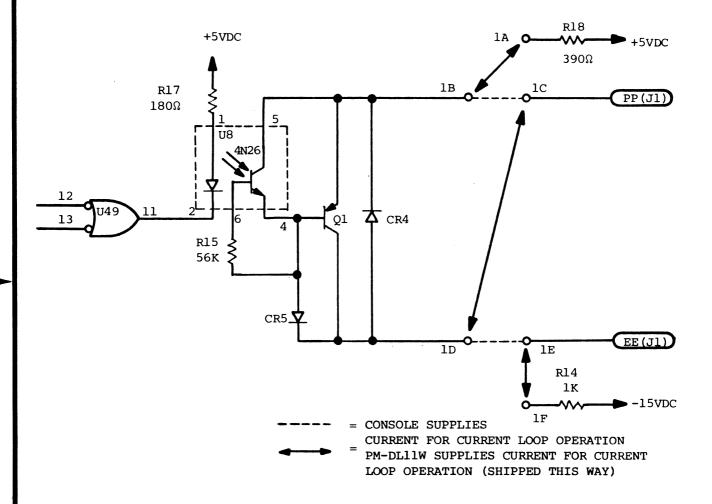

| Figure 2-2: | Reader Enable Circuit Options          | 2-8  |

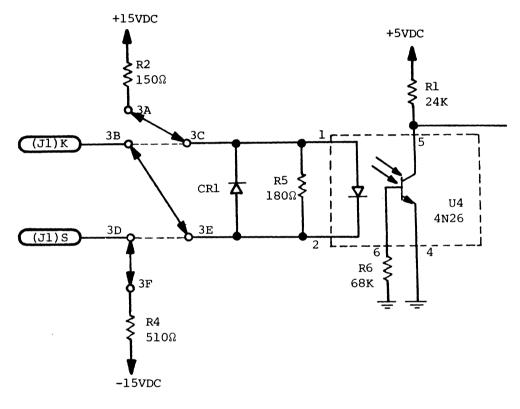

| Figure 2-3: | Receiver Circuit Options               | 2-9  |

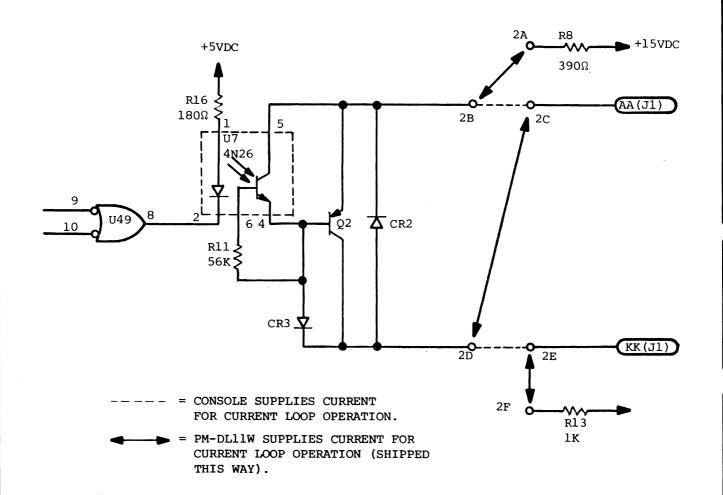

| Figure 2-4: | Transmitter Circuit Options            | 2-10 |

| Figure 2-5: | PM-DL11W Switch Locations              | 2-11 |

| Figure 2-6: | PM-DL11W Jumper Connections            | 2-12 |

| Figure 3-1: | PM-DL1W Interface Block Diagram        | 3-2  |

| Figure 3-2: | Line Clock Block Diagram               | 3-4  |

| Figure 3-3: | Data Word Format                       | 3-5  |

| Figure 3-4: | Receiver Status Register Bit Format    | 3-6  |

| Figure 3-5: | Receiver Data Buffer Bit Format        | 3-7  |

| Figure 3-6: | Transmitter Status Register Bit Format | 3-8  |

| Figure 3-7: | Transmitter Data Buffer Bit Format     | 3-9  |

| Figure 3-8: | Clock Status Register Bit Format       | 3-10 |

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

IZE CODE IDENT NO.

DWG NO.

Δ

52648

MA 701320

SCALE

REV

SHEET 0-2

### Section 1

### General Information

#### 1.1 INTRODUCTION

This manual provides the information needed to install and operate the PM-DL1LW serial line interface with line time clock manufactured by Plessey Peripheral Systems, Irvine, California 92714.

The material is arranged into three sections as follows:

Section 1 - GENERAL INFORMATION. This section contains a brief description of the PM-DL11W and a list of the physical specifications of the interface.

Section 2 - INSTALLATION. This section explains the requirements and procedures for equipment installation. Interface information and switch settings for each option are provided.

Section 3 - FUNCTIONAL DESCRIPTION. This section contains a detailed functional description of the PM-DL11W including the format of the data word and function of each device register.

Section 4 - MAINTENANCE AND TROUBLESHOOTING. This section provides a brief description of board maintenance procedures.

Drawing Package: A separate drawing package is available. This document MD 701320 contains assembly drawings, parts lists, and schematics required for a complete understanding of the PM-DL11W.

#### 1.2 GENERAL DESCRIPTION

The PM-DL11W is a serial line interface and a line time clock designed to operate in the Digital Equipment Corporation (DEC) PDP-11 series computers.\* It is directly compatible to and is a plug for plug replacment for the DEC DL11-W. As a serial line interface it receives asynchronous serial data from an external device such as a teletype or CRT display and converts it to parallel data for transfer to the Unibus.\* Parallel data from the Unibus is converted to serial data to be transmitted to the external device. As a line time clock the PM-DL11W initiates interrupt sequences at intervals determined by the line frequency.

\*Teletype is a registered trademark of Teletype Corporation.

\*DEC, PDP, and Unibus are registered trademarks of Digital Equipment Corp.

The information hereon is the property of PLESSEY PERIPHERAL SYS. Transmittal receipt or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or in part, shall be made without written authorization from PLESSEY PERIPHERAL SYS.

| SIZE  | CODE IDEN | NT NO. | DWG NO. |       |     |

|-------|-----------|--------|---------|-------|-----|

| Α     | 52648     |        | MA 70   | 1320  |     |

| SCALE |           | REV    |         | SHEET | 7 1 |

The PM-DL11W contains a control and status register for programmer control and a data buffer register for storage of data prior to transfer to the external device.

Switch selection on the PM-DLllW card provides the flexibility to handle a variety of different terminals such as a teletype or a high speed CRT. The user may also select line speed, character size, stop code length, and parity error detection.

#### 1.3 SPECIFICATIONS

The PM-DL11W is contained on a single 8.96" x 15.58" quad height printed circuit board. It can be used in conjunction with or in place of the DEC DL11-W serial line interface and line time clock.

The PM-DL11W can be mounted in any small peripheral controller (SPC) slot of a PDP-11 computer or any of the following backplanes:

| <ul><li>PM-Dl1/SPC-1</li></ul> | Plessey double systems unit       |

|--------------------------------|-----------------------------------|

| <ul><li>PM-D11/SPC-2</li></ul> | Plessey single systems unit       |

| <ul><li>PM-F11/SPC</li></ul>   | Plessey double systems unit       |

| • PM-F11/SPC-1                 | Plessey single systems unit       |

| DEC DD11-A                     | DEC single systems unit           |

| <ul> <li>DEC DD11-B</li> </ul> | DEC single systems unit           |

| • DEC DD11-C                   | DEC single systems unit           |

| ● DEC DD11-D                   | DEC double systems unit           |

| • DEC DD11-P                   | DEC processor double systems unit |

#### 1.3.1 CONFIGURATION

PM-DL11W

The PM-DL11W is available in three versions as follows:

| PM-DL11WA | - | This version is used as a 20mA current loop       |

|-----------|---|---------------------------------------------------|

|           |   | electrical interface. It is furnished with a 4    |

|           |   | foot cable terminated with Mate-N-Lock connectors |

|           |   | suitable for connection to DEC terminals.         |

This version consists of the board assembly only.

| PM-DL11WB | <br>This version is used to interface with EIA  |

|-----------|-------------------------------------------------|

|           | RS232C. It is supplied with a 25 foot cable     |

|           | terminated by a Cinch DB25P plug for connection |

|           | to equipment with EIA interface.                |

| The information hereon is the property of PLESSEY MEMORIES IN-                                                                                | SIZE  | CODE IDEN | NINO. | DWG NO.   |              |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-------|-----------|--------------|

| CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture | ΙΑΙ   | 52648     |       | MA 701320 |              |

| or part, shall be made without written authorization from PLESSEY MEMORIES, INC.                                                              | SCALE |           | REV   | A,        | SHEET<br>1-2 |

FORM 000021

PM-DL11WC This version is used to interface with ADM3 type terminal interfaces. It is supplied with a 25 foot cable and requires no additional adapters.

#### 1.3.2 POWER REQUIREMENTS

The current required to operate the PM-DL11W is shown in Table 1-1.

| VOLTAGES   | TYPICAL OPERATING CURRENT |

|------------|---------------------------|

| +5V        | 2.0A                      |

| -15V       | 150 mA                    |

| +9 to +15V | 50mA                      |

Table 1-1: Power Requirements

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

SCALE

CODE IDENT NO. DWG NO.

52648

REV

MA 701320

SHEET 1-3

### Section 2

### Installation

This section provides information for the installation of the PM-DLllW board. It also lists the various options available on the board and explains their incorporation.

#### 2.1 UNPACKING AND INSPECTION

The PM-DL11W is shipped in a special packing carton designed to keep the board from vibrating and to give it maximum protection during shipment. The packing carton should be retained in case the interface requires reshipment.

To unpack the PM-DL11W, remove any packing materials and visually inspect for physical damage.

#### 2.2 ASSEMBLY PART NUMBERS

| PART NUMBER                            | ASSEMBLY                                                                         |

|----------------------------------------|----------------------------------------------------------------------------------|

| 701065-100<br>701116-100<br>701117-100 | Top Assembly, PM-DL11W Cable Assembly for PM-DL11WB Cable Assembly for PM-DL11WA |

| 701239-100                             | Cable Assembly for PM-DL11WC                                                     |

### 2.3 BOARD INSTALLATION

The PM-DL11W can be mounted in any small peripheral controller (SPC) slot of the PDP-11/05, 11/10, 11/35, and 11/40 processor backplanes. It can also be mounted in any of the following backplanes:

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

CODE IDENT NO.

DWG NO.

MA 701320

SCALE

52648

REV

SHEET 2-1

| • | PM-D11/SPC-1 | Plessey double systems unit backplane. |

|---|--------------|----------------------------------------|

| • | PM-D11/SPC-2 | Plessey single systems unit backplane. |

| • | PM-F11/SPC   | Plessey double systems unit backplane. |

| • | PM-F11/SPC-1 | Plessey single systems unit backplane. |

| • | DEC DD11-A   | DEC single systems unit.               |

| • | DEC DD11-B   | DEC single systems unit.               |

| • | DEC DD11-C   | DEC single systems unit.               |

| • | DEC DD11-D   | DEC double systems unit.               |

| • | DEC DD11-P   | DEC processor double systems unit.     |

Mount the PM-DL11W in connectors C through F with the components facing connector row 1.

### 2.4 OPTIONS

The PM-DL11W contains four DIP switches for selection of baud rate, break bit enable, data word format, address selection, and vector address selection. Active and passive modes of operation are jumper selectable.

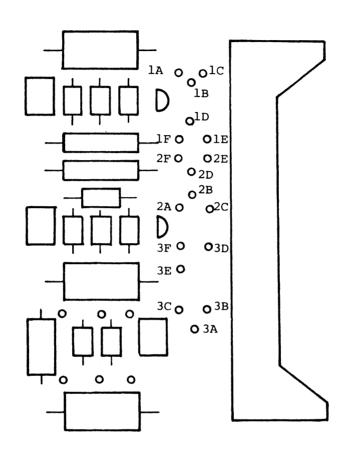

Refer to Figures 2-5 and 2-6 at the end of the section for location of switches and jumper configurations on the board. Directions for setting each switch and jumper are contained in the following.

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE CODE IDENT NO. DWG NO.

52648

MA 701320

SCALE REV A SHEET 2-2

### SWITCH SW1

Switch SWl controls the optional UART functions including data word format, break disable, and disable error bits. The format of the data word contains the following switch-selectable options: odd or even parity, number of data bits from 5 to 8, one or two stop bits and parity enable. Table 2-1 lists the UART options and their corresponding switch settings. Figure 2-5 at the end of the section shows the location of the switches on the board.

| SWITCH 1<br>POSITION | FUNCTION                                                                                                                                                  | ı                |                                                          |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------|--|--|

| 1                    | BREAK DISABLE. Op                                                                                                                                         | pening this swit | tch disables the break                                   |  |  |

| 2                    | Not used.                                                                                                                                                 |                  |                                                          |  |  |

| 3                    | ODD OR EVEN PARITY. This switch is open for even parity and closed for odd parity.                                                                        |                  |                                                          |  |  |

| 5, 4                 | DATA BITS. These two switch positions select the number of data bits in a serial character. Switch settings are as follows where 1 = open and 0 = closed. |                  |                                                          |  |  |

|                      | NUMBER OF BITS                                                                                                                                            | POSITION 5       | POSITION 4                                               |  |  |

|                      | 5<br>6<br>7<br>8                                                                                                                                          | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1                                         |  |  |

| 6                    |                                                                                                                                                           | l character. T   | the number of stop<br>he switch is open for<br>stop bit. |  |  |

| 7                    | 1                                                                                                                                                         |                  | is closed it enables<br>sables parity operation.         |  |  |

| 8                    |                                                                                                                                                           |                  | witch is open it disables<br>the receiver data buffer    |  |  |

Table 2-1: UART Function Switches

| The information hereon is the property of PLESSEY MEMORIES IN-                                                                                                                                                         | SIZE                   | CODE IDEN | NT NO. | DWG            | NO.   |           |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|--------|----------------|-------|-----------|--|

| CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole | $\mid \mathbf{A} \mid$ | 52648     |        | MA             | 70132 | 0         |  |

| or part, shall be made without written authorization from PLESSEY MEMORIES, INC.                                                                                                                                       | SCALE                  |           | REV    | $\overline{c}$ |       | SHEET 2-3 |  |

#### SWITCH SW2

Switch SW2 controls baud rate selection and line time clock enable.

The PM-DL11W provides completely independent speed selection for data transmission and reception. Baud rates for the receiver and transmitter are selectable using switch SW2 to any of the following rates: 50, 75, 110, 134.5, 150, 200, 300, 600, 1200, 1800, 2400, 4800, and 9600. Table 2-2 shows the switch settings for baud rates and line time clock enable. Figure 2-5 at the end of the section shows the location of the switches on the board.

#### RECEIVER BAUD RATE

#### TRANSMITTER BAUD RATE

| SWI                           | TCH 2                                 | POS                                                 | ITION                              | BAUD RATE                                                                                        | SWI                                  | rch 2                                   | POSI                                        | TION                               | BAUD RATE                                                                                        |

|-------------------------------|---------------------------------------|-----------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------|---------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|

| 7<br>(6)                      | 5<br>(4)                              | 3<br>(2)                                            | 1<br>(0)*                          |                                                                                                  | 8<br>(7)                             | 6<br>(5)                                | 4<br>(3)                                    | 2<br>(1)*                          |                                                                                                  |

| ON ON ON ON ON ON OFF OFF OFF | ON ON ON OFF OFF OFF ON ON ON OFF OFF | ON OFF ON | ON OFF ON OFF ON OFF ON OFF ON OFF | 0<br>0<br>50<br>75<br>134.5<br>200<br>600<br>2400<br>9600<br>4800<br>1800<br>1200<br>2400<br>300 | ON ON ON ON ON ON ON OFF OFF OFF OFF | ON ON ON OFF OFF OFF ON ON ON ON ON OFF | ON ON OFF ON OFF ON OFF ON ON OFF ON ON OFF | ON OFF ON OFF ON OFF ON OFF ON OFF | 0<br>0<br>50<br>75<br>134.5<br>200<br>600<br>2400<br>9600<br>4800<br>1800<br>1200<br>2400<br>300 |

| OFF<br>OFF                    | OFF<br>OFF                            | OFF<br>OFF                                          | ON<br>OFF                          | 150<br>110                                                                                       | OFF<br>OFF                           | OFF<br>OFF                              | OFF                                         | ON<br>OFF                          | 150<br>110                                                                                       |

#### LTC ENABLE

| FUNCTION     | POSITION 9 (8)* | POSITION 10 (9) |  |

|--------------|-----------------|-----------------|--|

| LTC enabled  | ON              | OFF             |  |

| LTC disabled | OFF             | ON              |  |

\*NOTE: Some switches are numbered 0-9 instead of 1-10.

Table 2-2: SW2 Switch Settings

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

| SIZE  | CODE IDEN | NT NO. | DWG | NO.   |       |     |

|-------|-----------|--------|-----|-------|-------|-----|

| Α     | 52648     |        | MA  | 70132 | 20    |     |

| SCALE |           | REV    | A   |       | SHEET | 2-4 |

#### SWITCH SW3

Switch SW3 is used to select the vector address as illustrated in Table 2-3. Figure 2-5 at the end of the section shows the location of the switches on the board. Normally the vector assigned to the PM-DL11W for console device is  $60_{\circ}$ .

|          |            |                | SAMPLE | SETTINGS |

|----------|------------|----------------|--------|----------|

| SWITCH 3 | ASSOCIATED |                | VECTOR | VECTOR   |

| POSITION | ADDRESS    | SETTING        | 60     | 300      |

| 1        | Not used   | Always ON      | ON     | ON       |

| 2        | ADD2       |                | ON     | ON       |

| 3        | ADD3       |                | ON     | ON       |

| 4        | ADD4       | 2 through 7    | OFF    | ON       |

| 5        | ADD5       | OFF = 1 on Bus | OFF    | ON       |

| 6        | ADD6       |                | ON     | OFF      |

| 7        | ADD7       |                | ON     | OFF      |

| 8        | ADD8       | OFF = Ø on Bus | OFF    | OFF      |

Table 2-3: Vector Address Selection

#### SWITCH SW4

Switch SW4 is used for address selection. The PM-DL11W card may be addressed in the range of 776000 to 777770. The address format and switch positions are shown in Figure 2-1. Table 2-4 shows sample switch settings.

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC. SIZE CODE IDENT NO. DWG NO.

REV

52648

MA 701320

|                 | SAM                   | IPLE SETTINGS         |                       |

|-----------------|-----------------------|-----------------------|-----------------------|

| SW4<br>POSITION | BUS ADDRESS<br>177560 | BUS ADDRESS<br>176500 | BUS ADDRESS<br>176510 |

| 1               | OFF                   | ON                    | ON                    |

| 2               | OFF                   | OFF                   | OFF                   |

| 3               | ON                    | ON                    | ON                    |

| 4               | OFF                   | OFF                   | OFF                   |

| 5               | OFF                   | ON                    | ON                    |

| 6               | OFF                   | ON                    | OFF                   |

| 7               | ON                    | ON                    | ON                    |

| 8               | OFF                   | OFF                   | OFF                   |

| 9               | OFF                   | OFF                   | OFF                   |

| 10              | OFF                   | OFF                   | OFF                   |

Table 2-4: SW4 Address Selection

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittel, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE A SCALE

CODE IDENT NO.

REV

DWG NO.

52648

MA 701320

SHEET 2-6

FORM 000021

A

#### JUMPER CONFIGURATIONS

Jumpers on the board allow a reader enable for applications such as an ASR 33 teletype reader. Figure 2-2 depicts the jumper configuration for reader enable. Refer also to Figure 2-6 for location of jumpers on the board.

Figure 2-2: Reader Enable Circuit Options 20mA Current Loop

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE CODE IDENT NO. DWG NO.

52648

MA 701320

SCALE REV

SHEET

2-8

The PM-DL11WA with 20mA current loop interface can be operated in two modes: active and passive. The PM-DL11W is normally the active source of the 20mA current. However, when operating with two current loops and two processing systems only one device may provide the current; the other device is passive and receives current from the active device.

Figure 2-3 shows the jumper configuration for the receiver; and Figure 2-4 contains the transmitter configuration. Refer also to Figure 2-6 for jumper locations on the board.

---- = CONSOLE SUPPLIES CURRENT FOR

CURRENT LOOP OPERATION.

= PM-DL11W SUPPLIES CURRENT FOR

CURRENT LOOP OPERATION (SHIPPED

THIS WAY)

Figure 2-3: Receiver Circuit Options 20mA Current Loop

The information hereon is the property of PLESSEY MEMORIES INCORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE CODE IDENT NO.

MA 701320

SCALE

REV

SHEET

2-9

Figure 2-4: Transmitter Circuit Options 20mA Current Loop

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SCALE REV A

A SHEET 2-10

SW2 SEE FIGURE SW4 2-2 SW3 SWl TBl Figure 2-5: PM-DLllW Switch Locations he information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC. CODE IDENT NO. DWG NO. SIZE A 52648 MA 701320 SCALE REV SHEET 2-11

Figure 2-6: PM-DL11W Jumper Connections

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE CODE IDENT NO. DWG NO.

52648 MA 701320

SCALE REV A

SHEET 2-12

#### PRIORITY LEVELS

The PM-DL11W also has a 16-pin socket (TB1) for setting priority of the BR level. In general the PM-DL11W should always be set at BR4 and the clock is fixed at BR6. The following jumper chart should be used to set the proper BR level strapping.

|               | TBl |

|---------------|-----|

| Level 4 (BR4) | 195 |

| Level 5 (BR5) | 196 |

| Level 6 (BR6) | 197 |

| Level 7 (BR7) | 198 |

Table 2- : Jumper Priority Chart

#### 2.5 EXAMPLE CONFIGURATIONS

Example 1: If the PM-DL11W is interfaced to a terminal such as a TTY that is used as the console device using 110 baud rate, 8 bit characters, no parity, and 20mA current loop, the switch settings are as follows:

SW1-1 Off (Must be on to run PM-DL11W diagnostics) -2 -3 -4 Off -5 Off -6 Off -7 On -8 Off (Must be on to run PM-DL11W diagnostics) SW2-1 Off Off -2 -3 Off -4 Off -5 Off -6 Off -7 Off -8 Off -9 On \ Enables clock. Used only when no other Off ( -10 clock is present.

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

ZE CODE IDENT NO. DWG NO.

52648

MA 701320

SCALE

REV

SHEET

SW3-1 Vector address 60<sub>o</sub>. -2 On -3 On -4 Off -5 Off -6 On -7 On Off -8 SW4-1 Off Address 777560 . -2 Off -3 On -4 Off -5 Off Off -6 -7 On -8 Off -9 Off -10 Off

Note that this setting is for a console device.

Where: the Receiver Status Register is 777560

the Receiver Data Buffer Register is 777562 the Transmitter Status Register is 777564 the Transmitter Data Buffer Register is 777566

The Clock Status Register is fixed at 777546.

If additional PM-DL11W units are installed, the address selection must fall into the preassignment space as follows:

| lst unit  | 776xx0<br>xx2<br>xx4<br>xx6          | Where: XX = 50 through 67    |

|-----------|--------------------------------------|------------------------------|

| 16th unit | 776670<br>776672<br>776674<br>776676 |                              |

| Also      | 77xxx0<br>77xxx2<br>77xxx4<br>77xxx6 | Where: XXX = 561 through 617 |

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

CODE IDENT NO. DWG NO.

REV

52648

MA 701320

SCALE

SHEET 2-14

The PM-DL11W is normally used as the active device and the option jumpers should be installed as shown in Figures 2-2 through 2-6. These jumpers are installed at the factory and normally should not require changes.

Example 2: If the PM-DLllW is to be used as the console device with the DEC VT52AE set up as 300 baud, no parity, 8 bit character, EIA interface, the unit should be set up as follows:

| • | SW1-1                                                                                     | Off                                            | (Must b  | e on  | to   | run               | diagnosti | .cs) |

|---|-------------------------------------------------------------------------------------------|------------------------------------------------|----------|-------|------|-------------------|-----------|------|

|   | -2                                                                                        |                                                |          |       |      |                   |           |      |

|   | -3                                                                                        |                                                |          |       |      |                   |           |      |

|   | -4                                                                                        | Off                                            |          |       |      |                   |           |      |

|   | -5                                                                                        | Off                                            |          |       |      |                   |           |      |

|   | <del>-</del> 6                                                                            | On                                             |          |       |      |                   |           |      |

|   | -7                                                                                        | On                                             |          |       |      |                   |           |      |

|   | -8                                                                                        | Off                                            | (Must be | e on  | to   | run               | diagnosti | .cs) |

|   |                                                                                           |                                                |          |       |      |                   |           |      |

| • | SW2-1                                                                                     | Off                                            |          |       |      |                   |           |      |

|   | <b>-</b> 2                                                                                | Off                                            |          |       |      |                   |           |      |

|   | -3                                                                                        | On                                             |          |       |      |                   |           |      |

|   | -4                                                                                        | On                                             |          |       |      |                   |           |      |

|   | <del>-</del> 5                                                                            | Off                                            |          |       |      |                   |           |      |

|   | -6                                                                                        | Off                                            |          |       |      |                   |           |      |

|   | -7                                                                                        | Off                                            |          |       |      |                   |           |      |

|   | -8                                                                                        | Off                                            |          |       |      |                   |           |      |

|   | -9                                                                                        | On (                                           | LTC enal | h1 a  |      |                   |           |      |

|   | -10                                                                                       | Off∫                                           | ric ella | ore   |      |                   |           |      |

|   |                                                                                           |                                                |          |       |      |                   |           |      |

|   |                                                                                           |                                                |          |       |      |                   |           |      |

| • | SW3-1                                                                                     | _                                              | Vector a | addre | ss   | 60 <sub>g</sub> . |           |      |

| • | -2                                                                                        | On                                             | Vector a | addre | ss   | 60 <sub>8</sub> . |           |      |

| • | -2<br>-3                                                                                  | On                                             | Vector a | addre | ss ( | 60 <sub>8</sub> . |           |      |

| • | -2<br>-3<br>-4                                                                            | On<br>Off                                      | Vector a | addre | ss ' | 60 <sub>8</sub> . |           |      |

| • | -2<br>-3<br>-4<br>-5                                                                      | On<br>Off<br>Off                               | Vector a | addre | SS ( | 60 <sub>8</sub> . |           |      |

| • | -2<br>-3<br>-4<br>-5<br>-6                                                                | On<br>Off<br>Off<br>On                         | Vector a | addre | SS ( | 60 <sub>8</sub> . |           |      |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7                                                          | On<br>Off<br>Off<br>On<br>On                   | Vector a | addre | SS   | 60 <sub>8</sub> . |           |      |

| • | -2<br>-3<br>-4<br>-5<br>-6                                                                | On<br>Off<br>Off<br>On                         | Vector a | addre | SS   | 60 <sub>8</sub> . |           |      |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7                                                          | On<br>Off<br>Off<br>On<br>On<br>Off            |          |       |      |                   |           |      |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8                                                    | On Off Off On On Off                           |          |       |      |                   | sole devi | ce)  |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8<br>SW4-1                                           | On Off Off On On Off Off                       |          |       |      |                   |           | ce)  |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8<br>SW4-1<br>-2<br>-3                               | On Off Off On On Off Off Off Off               |          |       |      |                   |           | ce)  |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8<br>SW4-1<br>-2<br>-3<br>-4                         | On Off Off On Off Off Off Off Off              |          |       |      |                   |           | ce)  |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8<br>SW4-1<br>-2<br>-3<br>-4<br>-5                   | On Off Off On Off Off Off Off Off On Off       |          |       |      |                   |           | ce)  |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8<br>SW4-1<br>-2<br>-3<br>-4<br>-5<br>-6             | On Off Off On Off Off Off Off Off Off Of       |          |       |      |                   |           | ce)  |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8<br>SW4-1<br>-2<br>-3<br>-4<br>-5<br>-6<br>-7       | On Off Off On Off Off Off Off Off Off Of       |          |       |      |                   |           | ce)  |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8<br>SW4-1<br>-2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8 | On Off Off On On Off Off Off Off On Off On Off |          |       |      |                   |           | ce)  |

| • | -2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8<br>SW4-1<br>-2<br>-3<br>-4<br>-5<br>-6<br>-7       | On Off Off On Off Off Off Off Off Off Of       |          |       |      |                   |           | ce)  |

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

CODE IDENT NO. DWG NO. SIZE 52648

MA 701320

SCALE

REV

SHEET 2-15

### Section 3

## **Functional Description**

This section describes the functional units of the PM-DL11W serial line interface and line time clock.

### 3.1 SERIAL LINE INTERFACE

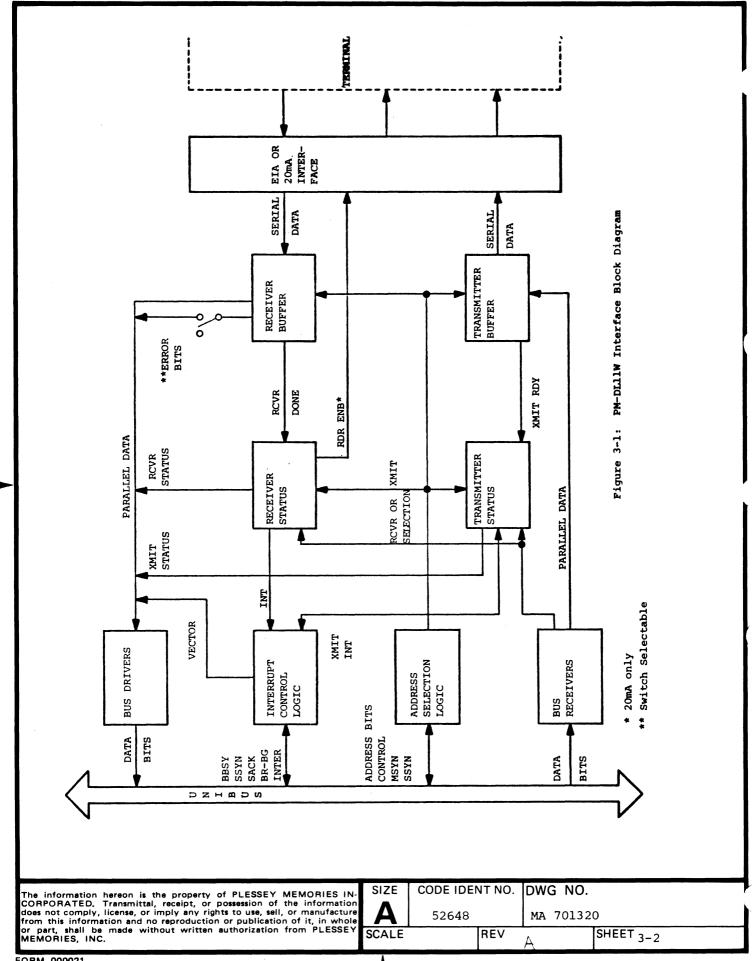

Figure 3-1 contains a simplified block diagram of the interface functions of the PM-DL11W. Each functional unit of the interface is described below.

SELECTION LOGIC: The selection logic of the PM-DLllW determines if the interface has been selected and which of five internal registers is selected and whether it is to perform an input or output function.

REGISTERS: The PM-DLllW contains five internal registers which provide data transfer, and control and status information for the interface. They are program addressable and are described in detail later in the section.

INTERRUPT CONTROL LOGIC: Permits the line clock, receiver, or transmitter to request and gain control of the Unibus for a vectored interrupt.

RECEIVER STATUS REGISTER: This register provides status indicators for the receiver logic. Status indicators include the receiver active flag, receiver done flag and the interrupt enable bit which is used to initiate interrupts when the done flag is set.

RECEIVER BUFFER REGISTER: This register which is part of the UART holds the character received from the external device prior to transfer to the Unibus.

TRANSMITTER STATUS REGISTER: This register provides the interrupt enable bit and the transmitter ready flag so that transmitter logic can be monitored and an interrupt intitiated. It also provides a maintenance bit and a break bit which generates a continuous space.

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC. SIZE | CODE IDENT NO. | DWG NO. | S2648 | MA 701320

SCALE

REV A

SHEET 3-1

TRANSMITTER BUFFER REGISTER: This register which is contained in the UART holds the character to be transferred to the external device.

BUS RECEIVERS: Parallel data from the Unibus is received by the bus receivers and then transferred to the appropriate device registers.

BUS DRIVERS: The parallel data from the registers, UART, or vector is gated onto the Unibus by the bus drivers.

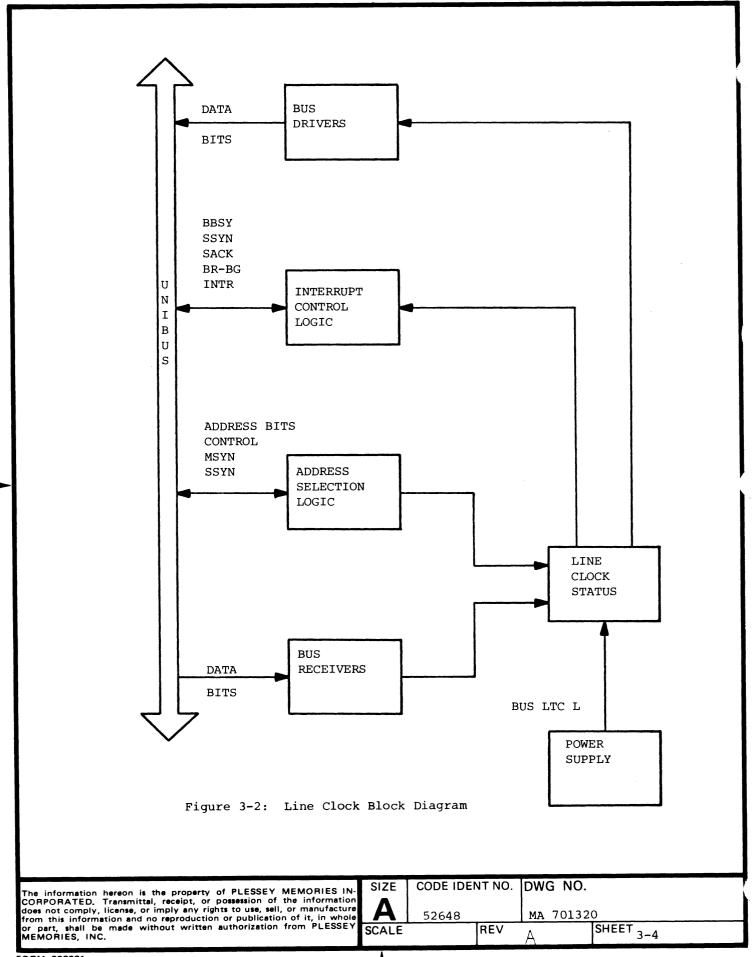

#### 3.2 LINE TIME CLOCK

A 50 or 60 cycle AC input generated by the power supply is monitored by the PM-DL1LW line time clock circuit. This signal, designated LTC, generates an interrupt each 16 2/3ms for 60 cycle current and each 20ms for 50 cycle current. The program can enable or disable LTC interrupts by setting the LTC INT ENB bit of the clock status register word.

Figure 3-2 shows a simplified block diagram of the line time clock. The line time clock status register provides the interrupt enable bit and the line clock monitor bit to allow program monitoring of the line clock signal or timed interrupt sequences to be initiated as desired. The other functional units in the diagram are identical to those described for the serial interface.

#### 3.3 INTERRUPTS

The PM-DLllW has two interrupt channels, one for the receiver and transmitter section, and one for the line time clock. The receiver and transmitter section may be strapped to operate on BUS REQUEST 4-7 (BR4-BR7) priority levels. The line time clock is fixed at BUS REQUEST 6 (BR6) priority level.

The PM-DLllW can be used as a console interface card by selecting vector address  $60_8$  and  $64_8$ . If the unit is used as a communications interface other than a console interface, the vector addresses are assigned in the range of  $300_8$  to  $777_8$ . Vector addresses are selected using a switch. The vector interrupt for the line time clock is 100.

#### 3.4 DATA FORMAT

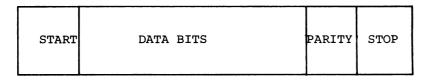

Figure 3-3 depicts the format of the eleven bit data word. The data word consists of a start bit, five to eight data bits, a parity bit, and one, one and a half, or two stop bits.

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SCALE REV

SHEET

3-3

FORM 000021

Ø 1 2 3 4 5 6 7 8 9 1Ø 11

Figure 3-3: Data Word Format

Each field of the data word is described in the following:

| BIT   |           | DESCRIPTION                                                                                                                                   |

|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| ø     | START     | Indicates to the interface receiver logic that serial data is ready to be loaded into the reader buffer register.                             |

| 1-8   | DATA BITS | From five to eight data bits may be used. When fewer than eight bits are used, they are left adjusted to the lowest significant bit position. |

| 9     | PARITY    | When set, the parity bit enables parity checking functions.                                                                                   |

| 10-11 | STOP      | Stop bits indicate the end of the data word. One, one and one half or two stop bits may be selected.                                          |

#### 3.5 DEVICE REGISTERS

Software control of the PM-DL11W is accomplished via device registers. The registers and corresponding addresses are:

| Receiver Status Register    | 76xxxø |

|-----------------------------|--------|

| Receiver Data Buffer        | 76XXX2 |

| Transmitter Status Register | 76XXX4 |

| Transmitter Data Buffer     | 76xxx6 |

he information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE CODE IDENT NO. DWG NO.

REV

**SCALE** 52648

MA 701320 SHEET 3-5 Each of the registers is described below.

#### 3.5.1 RECEIVER STATUS REGISTER

This register contains status indicators for the PM-DLllW receiver logic. The format of the receiver status register bit assignments is shown in Figure 3-4.

| NOT USED | RCVR<br>ACT | NOT USED | RCVR<br>DONE | RCVR<br>INT<br>ENB | NOT USED | RDR<br>ENB |

|----------|-------------|----------|--------------|--------------------|----------|------------|

| 1        |             |          |              | LIND               |          |            |

15 14 13 12 11 1Ø 7 8 6 5 3 2 . 1 Ø

Figure 3-4: Receiver Status Register Bit Format

| BIT |                                 | DESCRIPTION                                                                                                                                                                                                                    |

|-----|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ø   | READER ENABLE                   | Write only. This bit advances the paper tape reader of an ASR teletype (20mA current loop) and clears bit 7. Reader enable is cleared when a valid start bit is detected or by the INIT signal. Setting this bit clears bit 7. |

| 1-5 | NOT USED                        |                                                                                                                                                                                                                                |

| 6   | RECEIVER<br>INTERRUPT<br>ENABLE | Read/Write. Alows an interrupt when bit 7 is also set. Bit 6 is cleared by the INIT signal.                                                                                                                                    |

| 7   | RECEIVER DONE                   | Read only. Bit 7 is set when data is ready for transfer to the Unibus. If bit 6 is set, receiver done causes an interrupt. It can be cleared by setting bit Ø, referencing the Receiver Data Buffer, or by the INIT signal.    |

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

CODE IDENT NO.

DWG NO.

SCALE

52648

REV

MA 701320

SHEET 3-6 8-1Ø NOT USED

11 RECEIVER ACTIVE

Read only. When set, this bit indicates that the receiver is busy. It is set when a start bit is detected. It is cleared at the leading edge of the receiver done signal or by the INIT signal.

#### 3.5.2 RECEIVER DATA BUFFER

The receiver data buffer holds the data character received from an external device prior to transfer to the Unibus. It also contains four read only error indicator bits as described below.

| <br> | <br>P<br>ERR | NOT USED | RECEIVER DATA BITS |

|------|--------------|----------|--------------------|

|      |              |          |                    |

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Figure 3-5: Receiver Data Buffer Bit Format

| BIT  |                         | DESCRIPTION                                                                                                                                                                                         |

|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ø-7  | RECEIVED DATA<br>BITS   | Read only. These bits contain the data from the external device.                                                                                                                                    |

| 8-1Ø | NOT USED                |                                                                                                                                                                                                     |

| 12   | RECEIVE PARITY<br>ERROR | Read only. This bit is set when a parity error is detected. If the non-parity option is selected, this bit is always zero.                                                                          |

| 13   | FRAMING ERROR           | Read only. This bit is set if the word read does not contain a valid stop bit. It is also used to detect a break in transmission or a break caused by pressing the BREAK character on the keyboard. |

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE CODE IDENT NO. DWG NO.

52648

MA 701320

SCALE

REV

SHEET

EET 3-7

| 14 | OVERRUN | Read only. This bit is set if the RCVR DONE bit (bit 7 of the Receiver Status Register word) is not reset before the following character is read. |

|----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | ERROR   | Read only. This bit indicates whether any of the above errors have been detected. It is set if bits 12, 13, or 14 are set.                        |

NOTE: Error bits 12-15 may be disabled via a switch on the card.

#### 3.5.3 TRANSMITTER STATUS REGISTER

The transmitter status register provides status indicators for the transmitter logic. It also contains a maintenance bit which can be set by a program to facilitate maintenance and a BREAK bit which if enabled (SW1) generates a continuous space.

15 14 13 12 11 10 1

Figure 3-6: Transmitter Status Register Bit Format

| <br>BIT |             | DESCRIPTION                                                                                                                                                                                                                              |

|---------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ø       | BREAK       | Read/Write. When set, this bit transmits a continuous space. It is cleared by the INIT signal. This bit may be disabled by a switch on the card.                                                                                         |

| 1       | NOT USED    |                                                                                                                                                                                                                                          |

| 2       | MAINTENANCE | Read/Write. When set, this bit disables the serial line input to the receiver and connects it to the serial output of the transmitter causing the PM-DL11W to be bypassed for maintenance purposes. Bit 2 is cleared by the INIT signal. |

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

SCALE

CODE IDENT NO. DWG NO.

REV

52648

MA 701320

SHEET 3-8

| 3-5 | NOT USED                           |                                                                                                                                                                                                                                    |

|-----|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | TRANSMITTER<br>INTERRUPT<br>ENABLE | Read/Write. This bit allows an interrupt sequence for the transmitter if bit 7 is also set. It is cleared by the INIT signal.                                                                                                      |

| 7   | TRANSMITTER<br>READY               | Read only. This bit sets when the Transmitter Data Buffer is ready to accept another word (INIT is generated). It is cleared when the Transmitter Data Buffer is loaded. When set, it initiates an interrupt if bit 6 is also set. |

#### 3.5.4 TRANSMITTER DATA BUFFER

This register holds the data prior to its transmission to an external device. The format of the data depends upon the switch settings on the PM-DLllW board. Figure 3-7 shows the bit format for seven bits of data.

| NOT USED | DATA BITS |

|----------|-----------|

|----------|-----------|

15 14 13 12 11 1ø 1

Figure 3-7: Transmitter Data Buffer Bit Format

| E | BIT  |           | DESCRIPTION                                                                                                 |

|---|------|-----------|-------------------------------------------------------------------------------------------------------------|

| Ø | Ø-7  | DATA BITS | Write only. This field contains the data<br>bits which are ready for transmission to<br>an external device. |

| 8 | 8-15 | NOT USED  |                                                                                                             |

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

CODE IDENT NO. DWG NO.

Д

52648

MA 701320

SCALE

REV

SHEET 3-9

#### 3.5.5 CLOCK STATUS REGISTER

The clock status register contains the interrupt enable bit and the line clock monitor bit which allows program monitoring of the line clock signal and initiation of timed interrupts. Figure 3-8 shows the bit format for the clock status register word.

| NOT USED | MON | INT<br>ENB | NOT USED |

|----------|-----|------------|----------|

|          |     |            |          |

15 14 13 12 11 10 9 8 7 6 2 1 Ø

Figure 3-8: Clock Status Register Bit Format

| BIT |                     | DESCRIPTION                                                                                                                              |

|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Ø-5 | NOT USED            |                                                                                                                                          |

| 6   | INTERRUPT<br>ENABLE | Read/Write. When set, this bit allows an interrupt if bit 7 is also set.                                                                 |

| 7   | MONITOR             | Read/Clear. This bit is set by the line frequency clock signal LTC. It can be cleared by the programmer and is reset by the INIT signal. |

#### 3.6 PDP-11/20 MOD - MICRO 1 MOD

During operation in most PDP-11 computers when an CPR occurs right after an interrupt has been requested, the NPR will block the bus grant to the interrupting device. When this happens the CPU waits a short time for the interrupting device to respond. When no response happens, the CPU cancels the interrupt grant and services the NPR. In a PDP-11/20 or a Micro 1 (LSI-11 based system) when an interrupt is started it must be finished. If no response is given to the bus grant, the CPU will time out and trap.

The -101 version of the DL11W takes care of this problem. The etch between W1 and W2 on the solder side of the board must be cut.

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE

SCALE

CODE IDENT NO. DWG NO.

REV

52648

MA 701320

SHEET

3-10

### Section 4

## Maintenance and Troubleshooting

This section contains maintenance and troubleshooting information. drawings in the appendix are provided for further reference.

#### 4.1 PRINTED CIRCUIT BOARD CLEANING

The printed circuit contacts should be cleaned when dust or dirt has builtup on the surfaces. Instant Contact Cleaner, alcohol, and freon have been approved for cleaning contacts. When printed circuit contacts must be cleaned, hold the card so the contacts are pointed down and thoroughly saturate the contact area. While the contacts are still wet, scrub with a soft natural bristle brush.

CAUTION

Under no circumstances should an eraser or other abrasive be used on gold plated contacts.

To remove dust from printed circuit boards, a soft brush should be used. Clear, oil-free, pressurized air (5 psi max) can be sprayed over the board.

#### 4.2 TROUBLESHOOTING

In the case of an apparent malfunction, do the following:

- Reset each switch to be sure that it is properly seated.

- 2. Make sure that the strapping plug is installed and oriented properly (See Section 2).

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture 52648 from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC. SCALE

CODE IDENT NO. DWG NO. SIZE

MA 701320

REV

SHEET 4-1 Make sure that the I/O cable is installed correctly and check it for any broken wires.

If the malfunction persists, it is recommended that the board be returned to the factory for repair.

The information hereon is the property of PLESSEY MEMORIES IN-CORPORATED. Transmittal, receipt, or possession of the information does not comply, license, or imply any rights to use, sell, or manufacture from this information and no reproduction or publication of it, in whole or part, shall be made without written authorization from PLESSEY MEMORIES, INC.

SIZE А

CODE IDENT NO. DWG NO.

52648

MA 701320

SCALE

REV

SHEET 4-2