# Features of the MSP430 Bootstrap Loader

Franz Graf

**MSP430**

#### ABSTRACT

The MSP430 bootstrap loader (BSL) enables users to communicate with embedded memory in the MSP430 microcontroller during the prototyping phase, final production, and in service. Both the programmable memory (flash memory) and the data memory (RAM) can be modified as required.

The commonly used UART protocol with RS232 interfacing is supported, allowing flexible use of both hardware and software.

To use the bootstrap loader, a specific BSL entry sequence has to be applied to specific device pins. An added sequence of commands initiates the desired function. A boot loading session can be exited by continuing operation at a defined user program address, or by the reset condition.

Access to the MSP430 memory via the bootstrap loader is protected against misuse by a user-defined password.

#### Contents

| 1 | Intro | oductio | n                                                     | 2   |

|---|-------|---------|-------------------------------------------------------|-----|

| 2 | Star  | ndard R | ESET and BSL Entry Sequence                           | 3   |

|   | 2.1   |         | 30 20- and 28-Pin Flash Devices With Shared JTAG Pins |     |

|   | 2.2   | MSP43   | 30 Flash Devices With Dedicated JTAG Pins             | 4   |

| 3 |       | RT Prot |                                                       |     |

| 4 |       |         | zation Sequence                                       | . 4 |

| 5 | -     |         | S                                                     |     |

| • |       |         | ected Commands                                        |     |

|   |       |         | ord Protected Commands                                |     |

| 6 | Pro   | gramm   | ing Flow                                              | 5   |

| 7 | Data  | a Frame | ,<br>,                                                | 5   |

|   | 7.1   |         | tream Structure                                       |     |

|   | 7.2   | Check   | sum                                                   | . 6 |

|   | 7.3   | Comm    | ands - Detailed Description                           | 7   |

|   |       | 7.3.1   | General                                               |     |

|   |       | 7.3.2   | RX Data Block                                         | . 8 |

|   |       | 7.3.3   | RX Password                                           | . 8 |

|   |       | 7.3.4   | Mass Erase                                            | . 8 |

|   |       | 7.3.5   | Erase Segment                                         | . 9 |

|   |       | 7.3.6   | Erase Check                                           | . 9 |

|   |       | 7.3.7   | Change Baud Rate                                      | 10  |

|   |       | 7.3.8   | Load PC                                               | 10  |

|   |       | 7.3.9   | TX Data Block                                         | 11  |

|   |       | 7.3.10  | TX BSL Version                                        | 11  |

| 8   | Loadable BSL                                          |      |

|-----|-------------------------------------------------------|------|

| 9   | Exiting the BSL                                       | . 12 |

| 10  | Password Protection                                   | . 13 |

| 11  | Code Protection Fuse                                  | . 13 |

| 12  | BSL Internal Settings and Resources                   | . 13 |

|     | 12.1 Chip Identification and BSL Version              | . 13 |

|     | 12.2 Vectors                                          |      |

|     | 12.3 Initialization Status                            |      |

|     | 12.4 Memory Allocation and Resources                  | . 15 |

| 13  | Special Consideration for BSL Version 1.10            | . 15 |

|     | •                                                     |      |

| Арр | endix A. Differences Between Devices and BSL Versions | . 17 |

#### Figures

| Figure 1. Standard RESET Sequence                   | . 3 |

|-----------------------------------------------------|-----|

| Figure 2. BSL Entry Sequence at Shared JTAG Pins    | . 3 |

| Figure 3. BSL Entry Sequence at Dedicated JTAG Pins | 4   |

#### Tables

| Table 1. | Data Frame of BSL Commands                                                                                                  | 6  |

|----------|-----------------------------------------------------------------------------------------------------------------------------|----|

|          | Recommendations for MSP430F149 [F449] ( $T_A = 25^{\circ}C$ , $V_{CC} = 3.0 \text{ V}$ , $f_{max} = 6.7 \text{ MHz}$ ) (see |    |

|          | Note 2)                                                                                                                     | 10 |

| Table 3. | BSL Version 1.10 on F13x, F14x(1), F11x, and F11x1                                                                          | 17 |

| Table 4. | BSL Version 1.30 on F41x, F11x, and F11x1                                                                                   | 18 |

| Table 5. | BSL Version 1.40 on F12x                                                                                                    | 19 |

| Table 6. | BSL Version 1.60 on F11x2, F12x2, F43x, F44x, FE42x, FW42x, FG43x                                                           | 20 |

| Table 7. | BSL Version 1.61 on F15x, F16x, F161x                                                                                       | 21 |

#### 1 Introduction

This bootstrap loader (BSL) provides a method to program the flash memory during MSP430 project development and updates. It can be activated by a utility that sends commands via the familiar UART protocol. The BSL enables the user to control the activity of the MSP430 and to exchange data using a personal computer or other device the supports a UART protocol.

To avoid accidental overwriting of the BSL code, this code is stored in a special factory-masked boot ROM. The BSL cannot ever be erased. The BSL code is highly optimized for the BSL function and is accessed using commands described later in this document. For security purposes and to prevent unwanted source readout, user code protection is very important. Any BSL command that directly or indirectly allows data reading is password protected.

To invoke the bootstrap loader, a BSL entry sequence has to be applied to dedicated pins. After that, a synchronization character, followed by the data frame of a specific command, initiates the desired function.

# 2 Standard RESET and BSL Entry Sequence

#### 2.1 MSP430 20- and 28-Pin Flash Devices With Shared JTAG Pins

Applying an appropriate entry sequence on the -RST/NMI and TEST pins forces the MSP430 to start program execution at the BSL RESET vector instead of at the RESET vector located at address FFFEh.

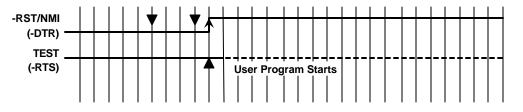

If the application interfaces with a computer UART, these two pins may be driven by the -DTR and -RTS signals of the serial communication port (RS232) after passing level shifters. Detailed descriptions of the hardware and related considerations are given in a separate document (see *References*, Section 14). The normal user reset vector at FFFEh is used, if TEST is kept low while RST/NMI rises from low to high (standard method, see Figure 1).

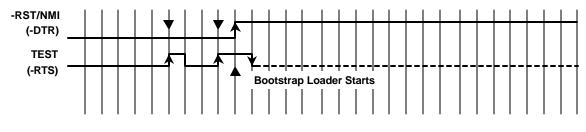

The BSL program execution starts whenever the TEST pin has received a minimum of two positive transitions and if TEST is high while -RST/NMI rises from low to high (BSL entry method, see Figure 2). This level/transition triggering improves BSL startup reliability.

Figure 1. Standard RESET Sequence

The TEST signal is normally used simply to switch the port pins P1.7 – P1.4 between their application function and the JTAG function. If the second rising edge at the TEST pin is applied while -RST/NMI is still low, the TEST signal is kept low internally (application mode).

The BSL will not be started (via the BSL RESET vector), if:

- There are less than two positive edges at the TEST pin while -RST/NMI is low

- TEST is low when -RST/NMI rises from low to high

- JTAG has control over the MSP430 resources

- Supply voltage V<sub>cc</sub> drops down and a power-on reset (POR) is executed

- -RST/NMI pin is configured for NMI functionality (NMI bit is set)

Figure 2. BSL Entry Sequence at Shared JTAG Pins

### 2.2 MSP430 Flash Devices With Dedicated JTAG Pins

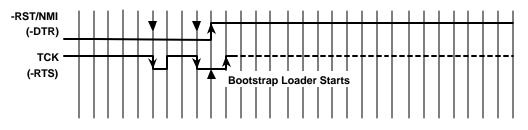

Devices with dedicated JTAG pins use the TCK pin instead of the TEST pin.

The BSL program execution starts whenever the TCK pin has received a minimum of two negative transitions and TCK is low while -RST/NMI rises from low to high (BSL entry method, see Figure 3). This level/transition triggering improves BSL start-up reliability.

Figure 3. BSL Entry Sequence at Dedicated JTAG Pins

The BSL will not be started (via the BSL RESET vector), if:

- There are less than two negative edges at TCK pin while -RST/NMI is low

- TCK is high if -RST/NMI rises from low to high

- JTAG has control over the MSP430 resources

- Supply voltage VCC drops down and a power on reset (POR) is executed

- -RST/NMI pin is configured for NMI functionality (NMI bit is set)

## 3 UART Protocol

The UART protocol applied here is defined as:

- Baud rate is fixed to 9600 baud in half duplex mode (one sender at a time).

- Start bit, 8 data bits (LSB first), an even parity bit, 1 stop bit.

- Handshake is performed by an acknowledge character.

**NOTE:** Applying baud rates other than 9600 baud at initialization results in communication problems or violates the flash memory write timing specification. The flash memory may be extensively stressed or may react with unreliable program/erase operations.

## 4 Synchronization Sequence

Before receiving any command, a synchronization character (SYNC) with its value of 80h has to be received by the BSL. This character is necessary to calculate all the essential internal parameters, which maintain UART and flash memory programming/erasing timings. It provides the BSL system time reference.

Next, an acknowledge DATA\_ACK = 90h is sent back by the BSL to confirm successful reception.

**NOTE:** The synchronization character is not part of the Data Frame described later.

### 5 Commands

Two categories of commands are available: commands needing a password and commands that do not require a password. The password protection safeguards every command that *potentially allows direct or indirect data access.*

#### 5.1 Unprotected Commands

- Receive password

- Mass erase (erase entire flash memory, main- as well as information-memory)

- Transmit BSL version (V1.60 or higher or in loadable BL\_150S\_14x.txt)

- Change baud rate (V1.60 or higher or in loadable BL\_150S\_14x.txt)

#### 5.2 Password Protected Commands

- Receive data block to program flash memory, RAM, or peripherals

- Transmit data block

- Erase segment

- Erase check (V1.60 or higher or in loadable BL\_150S\_14x.txt)

- Load program counter and start user program

## 6 **Programming Flow**

The write access (RX data block command) to the flash memory/RAM or peripheral modules area is executed *online*. That means a data byte/word is processed immediately after receipt and the write cycle is finished before a following byte/word has completely arrived. Therefore, the entire write time is determined by the baud rate and no buffering mechanism is necessary.

Data sections located below the flash memory area address are assumed to be loaded into the RAM or peripheral module area, and thus no specific flash control bits are affected.

**NOTE:** When losing control over the UART protocol either by line faults or by violating the data frame conventions, the only way to recover is to rerun the BSL entry sequence to initiate another BSL session.

### 7 Data Frame

The data frame used follows the TI MSP430 serial standard protocol (SSP) rules extended with a preceding synchronization sequence (SS) as previously described. The BSL is considered as a receiver in Table1.

The obvious redundancy of some parameters results from the adaptation to the SSP or to save boot ROM space.

For more information on serial standard protocol (SSP), see Application of Bootstrap Loader in MSP430 With Flash Hardware and Software Proposal (SLAA096).

#### 7.1 Data Stream Structure

- The first 8 bytes (HDR through LH) are mandatory (xx represents dummy data).

- Data bytes D1 to Dn are optional.

- Two bytes (CKL and CKH) for checksum are mandatory.

- Acknowledge done by the BSL is mandatory except with the TX data block and TX BSL version commands.

#### 7.2 Checksum

The 16-bit (2 bytes) checksum is calculated over all received/transmitted bytes B1 ... Bn in the data frame except the checksum bytes themselves by XORing words (2 successive bytes) and inverting the result.

#### Formula:

CHECKSUM = INV [ (B1 + 256\*B2) XOR (B3 + 256\*B4) XOR ... XOR (Bn-1 + 256\*Bn) ]

or

CKL = INV [ B1 XOR B3 XOR ... XOR Bn–1 ]; CKH = INV [ B2 XOR B4 XOR ... XOR Bn ]

| Received<br>BSL<br>Command | H<br>D<br>R | C<br>M<br>D | L1 | L2 | AL | АН | LL        | LH | D1 | D2 Dn   | C<br>K<br>L | C<br>K<br>H | A<br>C<br>K |

|----------------------------|-------------|-------------|----|----|----|----|-----------|----|----|---------|-------------|-------------|-------------|

| RX data block              | 80          | 12          | n  | n  | AL | AH | n–4       | 0  | D1 | D2 Dn–4 | CKL         | СКН         | ACK         |

| RX password                | 80          | 10          | 24 | 24 | хх | ХХ | хх        | хх | D1 | D2 D20  | CKL         | СКН         | ACK         |

| Erase segment              | 80          | 16          | 04 | 04 | AL | AH | 02/<br>04 | A5 | —  |         | CKL         | СКН         | ACK         |

| Mass erase                 | 80          | 18          | 04 | 04 | хх | хх | хх        | хх | _  |         | CKL         | СКН         | ACK         |

| Erase check                | 80          | 1C          | 04 | 04 | AL | AH | LL        | LH | —  |         | CKL         | СКН         | ACK         |

| Change baud rate           | 80          | 20          | 04 | 04 | D1 | D2 | D3        | хх | —  |         | CKL         | СКН         | ACK         |

| Load PC                    | 80          | 1A          | 04 | 04 | AL | AH | хх        | хх | —  |         | CKL         | СКН         | ACK         |

| TX data block              | 80          | 14          | 04 | 04 | AL | AH | n         | 0  | —  |         | CKL         | СКН         | —           |

| BSL responds               | 80          | xx          | n  | n  | D1 | D2 |           |    |    | Dn      | CKL         | СКН         | —           |

| TX BSL version             | 80          | 1E          | 04 | 04 | ХХ | ХХ | хх        | ХХ | —  |         | CKL         | СКН         |             |

| BSL responds               | 80          | хх          | 10 | 10 | D1 | D2 |           |    |    | D10     | CKL         | СКН         | —           |

Table 1.Data Frame of BSL Commands

Notes: All numbers are bytes in hexadecimal notation.

ACK is sent back by the BSL.

The synchronization sequence is not part of the data frame.

The erase check and TX BSL version commands are not members of the standard command set (V1.50 or higher).

The change baud rate command is not a member of the standard command set (V1.60 or higher or in loadable BL\_150S\_14x.txt).

#### Abbreviations:

**HDR** DATA\_FRAME = 80h means *data frame expected* in accordance with TI MSP430 serial standard protocol (SSP).

**CMD** Command identification

**L1, L2** Number of bytes consisting of AL through Dn Restrictions: L1 = L2, L1 < 255, L1 even.

AL, AH Block start address or erase (check) address or jump address LO/HI byte

**LL, LH** Number of pure data bytes (max. 250) or erase information LO/HI byte or block length of erase check (max. FFFFh)

- D1 ... Dn Data bytes

- **CKL, CKH** 16-bit checksum LO/HI byte

- **xx** Can be any data

- -- No character (data byte) received/transmitted

ACKThe acknowledge character returned by the BSL, can be eitherDATA\_ACK = 90h:Frame was received correctly, command was executed successfully, orDATA\_NAK = A0h:Frame not valid (e.g., wrong checksum, L1  $\neq$  L2),command is not defined, is not allowed, or was executed unsuccessfully.

**n** Number of bytes consisting of AL through Dn

#### 7.3 Commands - Detailed Description

See Table 1.

#### 7.3.1 General

Besides the header byte HDR (80h) and the command identification CMD, the frame length bytes L1 and L2 (which must be equal) hold the number of bytes following L2, excluding the checksum bytes CKL and CKH.

Bytes AL, AH, LL, LH, D1...Dn are command-specific. However, the checksum bytes CKL (low byte) and CKH (high byte) are mandatory.

If the data frame has been received correctly and the command execution was successful, an acknowledge character DATA\_ACK = 90h is sent back by the BSL. Incorrectly received data frames, unsuccessful operations, commands which are locked or not defined are confirmed with a DATA\_NAK = A0h.

**NOTE:** BSL versions lower than V1.30 support only byte access operations. The peripheral module addresses at 0100h–01FFh thus cannot be accessed correctly because they are word-oriented. From version V1.30 on addresses 0000h–00FFh are accessed in byte mode; all others are accessed in word mode.

#### 7.3.2 RX Data Block

The receive data block command is used for any write access to the flash memory/RAM or peripheral module control registers at 0000h–01FFh. It is password protected.

The 16-bit even-numbered block start address is defined in AL (low byte) and AH (high byte). The 16-bit even-numbered block length is defined in LL (low byte) and LH (high byte). Because pure data bytes are limited to a maximum of 250, LH is always 0.

The following data bytes are succeeded by the checksum bytes CKL (low byte) and CKH (high byte). If the receipt and programming of the appropriate data block was successful, an acknowledge character DATA\_ACK is sent back by the BSL. Otherwise, the BSL confirms with a DATA\_NAK.

**NOTE:** BSL versions V1.40 and higher support online verification inside the MSP430 for addresses 0200h–FFFFh which reduces programming/verification time to 50 percent. In case of an error the loadable bootstrap loader BL\_150S\_14x.txt additionally store the first incorrectly written location address+3 into the error address buffer in the RAM at address 0200h (021Eh for F14x devices).

#### 7.3.3 RX Password

The receive password command is used to unlock the password-protected commands, which perform reading, writing, or segment-erasing memory access. It is not password protected.

Neither start address nor block length information is necessary because the 32-byte password is always located at addresses FFE0h–FFFFh. Data bytes D1 to D20h hold the password information starting with D1 at address FFE0h.

If the receipt and verification of the password is correct a positive acknowledge DATA\_ACK is sent back by the BSL and the password-protected commands become unlocked. Otherwise the BSL confirms with a DATA\_NAK.

Once the protected commands become unlocked they remain unlocked until another BSL entry is initiated.

#### 7.3.4 Mass Erase

The mass erase command erases the entire flash memory area (main memory plus information memory, see corresponding data sheet). It is not password protected.

All parameters shown in Table 1 are mandatory. After erasing, an acknowledge character DATA\_ACK is sent back by the BSL.

Mass erase initializes the password area to 32 times 0FFh.

#### 7.3.5 Erase Segment

The erase segment command erases specific flash memory segments. It is password protected.

The address bytes AL (low byte) and AH (high byte) select the appropriate segment. Any evennumbered address within the segment to be erased is valid. After segment erasing, an acknowledge character DATA\_ACK is sent back by the BSL (V1.40 or lower).

BSL versions V1.60 or higher perform a subsequent erase check of the corresponding segment and respond with a DATA\_NAK if the erasure was not successful. In this case the first not erased location address+1 is stored in the error address buffer in the RAM at address 0200h (021Eh for F14x devices).

Erase segment 0 clears the password area, and therefore the remaining password is 32 times 0FFh.

When applying LL = 0x04 and LH = 0xA5 a mass erasure of only the main memory is performed. Indeed this command has to be executed min. 12 times to achieve a total erasure time of >200ms. No subsequent erase check of the entire main memory is done. Use the erase check command additionally.

The MSP430Fxxxx device segmentation is configured as follows:

| 0FE00h-0FFFFh :<br>0FC00h-0FDFFh :<br>0FA00h-0FBFFh :<br>0F800h-0F9FFh : | Segment 0<br>Segment 1<br>Segment 2<br>Segment 3 | Main memory        |

|--------------------------------------------------------------------------|--------------------------------------------------|--------------------|

|                                                                          |                                                  |                    |

| 01200h–013FFh :<br>01100h–011FFh :                                       | Segment n-1<br>Segment n                         |                    |

| 01080h–010FFh :<br>01000h–0107Fh :                                       | Segment A<br>Segment B                           | Information memory |

#### 7.3.6 Erase Check

The erase check command verifies the erasure of flash memory within a certain address range. It is password protected.

The 16-bit block start address is defined in AL (low byte) and AH (high byte). The 16-bit block length is defined in LL (low byte) and LH (high byte). Both can be either even or odd numbered to allow odd boundary checking.

If the erase check of the appropriate data block was successful (all bytes contain 0FFh), an acknowledge character DATA\_ACK is sent back by the BSL. Otherwise the BSL confirms with a DATA\_NAK and the first not erased location address+1 is stored in the error address buffer at address 0200h (021Eh for F14x devices).

**NOTE:** This command is not a member of the standard command set. It is implemented from BSL version V1.60 on or in the loadable bootstrap loader BL\_150S\_14x.txt.

#### 7.3.7 Change Baud Rate

The change baud rate command offers the capability of transmissions at higher baud rates than the default 9600 baud. With faster data transition shorter programming cycles can be achieved which is especially important with large flash memory devices. This command is not password protected.

Three control bytes D1 to D3 determine the selected baud rate. D1 and D2 set the processor frequency (f  $\geq$  fmin), D3 indirectly sets the flash timing generator frequency (fFTGmin  $\leq$  fFTG  $\leq$ fFTGmax). In detail:

- D1: F1xx: Basic clock module control register DCOCTL (DCO.2 ... DCO.0) F4xx: FLL+ system clock control register SCFI0 (D, FN 8 ... FN 2)

- D2: F1xx: basic clock module control register BCSCTL1 (XT2Off, Rsel.2 ... Rsel.0) F4xx: FLL+ system clock control register SCFI1 ( $N_{DCO}$ )

- D3: 0: 9600 Baud 1: 19200 Baud 2: 38400 Baud

After receiving the data frame an acknowledge character DATA ACK is sent back and the BSL becomes prepared for the selected baud rate. It is recommended for the BSL communication program to wait a little while (approximately 10 ms) between baud rate alternation and succeeding data transmission to give the BSL clock system time for stabilization.

**NOTE:** The highest achievable baud rate depends on various system and environment parameters like supply voltage, temperature range, and minimum/maximum processor frequency. See the corresponding device specification / data sheet.

**NOTE:** This command is implemented on BSL versions V1.60 or higher or available in the loadable bootstrap loader BL 150S 14x.txt.

#### Table 2. Recommendations for MSP430F149 [F449] ( $T_A = 25^{\circ}C$ , $V_{CC} = 3.0 \text{ V}$ , $f_{max} = 6.7 \text{ MHz}$ ) (see Note 2)

| Baud Rate<br>(Baud) | Proc. Freq.<br>f <sub>min</sub> (MHz)<br>(see Note 4) | D1<br>DCOCTL<br>[SCFI0]<br>(see Note 1) | D2<br>BCSCTL1<br>[SCFI1]<br>(see Note 1) | D3<br>(see Note 1) | Progr. / Verify<br>60 Kbytes<br>(sec)<br>(see Note 3) |

|---------------------|-------------------------------------------------------|-----------------------------------------|------------------------------------------|--------------------|-------------------------------------------------------|

| 9600 (init)         | 1.05                                                  | 80 [00]                                 | 85 [98]                                  | 00 [00]            | 78 + 3.7 [0.0]                                        |

| 19200               | 2.1                                                   | E0 [00]                                 | 86 [B0]                                  | 01 [01]            | 39 + 3.7 [2.4]                                        |

| 38400               | 4.2                                                   | E0 [00]                                 | 87 [C8]                                  | 02 [02]            | 20 + 3.7 [2.4]                                        |

Notes:

1. D1 to D3 are bytes in hexadecimal notation. 2.

Values in brackets [] are related to MSP430F449.

3. Additional 3.7 [2.4] seconds result from loading, verifying, and launching the loadable BSL.

The minimum processor frequency is lower than in the standard ROM BSL (see Initialization Status, Section 12.3).

#### 7.3.8 Load PC

The load program counter command directs the program counter (register R0) to any location within the entire address range. It is password protected.

After receiving the data frame an acknowledge character DATA\_ACK is sent back by the BSL. Then the selected address is moved into the program counter. The program flow continues operation there, and the BSL session is terminated.

Be aware that the password protection is not active at this time.

#### 7.3.9 TX Data Block

The transmit data block command is used for any read access to the flash memory/RAM or peripheral module control registers at 0000h–01FFh. It is password protected.

The 16-bit block start address is defined in AL (low byte) and AH (high byte). The 16-bit block length is defined in LL (low byte) and LH (high byte). Because pure data bytes are limited to a maximum of 250, LH is always 0. The checksum bytes CKL (low byte) and CKH (high byte) immediately follow this information.

Now the BSL responds with the requested data block. After transmitting HDR, dummy CMD, L1 and L2, The BSL sends data bytes D1 through Dn, followed by the checksum bytes CKL (low byte) and CKH (high byte). No acknowledge character is necessary.

#### 7.3.10 TX BSL Version

The transmit BSL version command gives the user information about chip identification and bootstrap loader software version. It is not password protected.

The values for AL, AH, LL, and LH can be any data, but must be transmitted to meet the protocol requirements. The checksum bytes CKL (low byte) and CKH (high byte) immediately follow this information.

After that, the BSL responds with a 16-byte data block. After transmitting HDR, dummy CMD, L1 and L2, the BSL sends data bytes D1 through D16 (decimal), followed by the checksum bytes CKL (low byte) and CKH (high byte). No acknowledge character is necessary.

D1, D2 and D11, D12 (decimal) hold the specific information:

- D1: Device family type (high byte)

- D2: Device family type (low byte)

- D11: BSL version (high byte)

- D12: BSL version (low byte)

The remaining 12 bytes are for internal use only.

### 8 Loadable BSL

For upgrading the BSL functionality, sometimes it is suitable to load a higher version of BSL into the RAM of a device and apply the latest innovations. To do so, use the following BSL commands:

- RX password (unlock password protection for following commands)

- RX data block (code of loadable BSL, code section address  $\geq$  220h)

- TX data block (for verification)

- RX data block (get start address from first code section address)

- Load program counter PC (with start address of loadable BSL)

- RX password (unlock password protection for loaded BSL)

- Perform any command (with loaded BSL)

The following loadable BSLs are available:

- BL\_150S\_14x.txt is a complete BSL for the F14x/F13x family with BSL version 1.10. All features of BSL version V1.60 are supported. Since its code size is bigger than 1kByte it only can be used in F1x8 and F1x9 devices. The error address buffer address for "RX Block", "Erase Segment", and "Erase Check" commands is 021Eh. BL\_150S\_14x.txt could also be used as a replacement for PATCH.txt.

- **BS\_150S\_14x**.txt is a small BSL with reduced command set for the F14x/F13x family with BSL version 1.10. Since its code size is smaller than 512B it can be used in F1x4 upto F1x9 devices.

The following commands of BSL version V1.60 are supported: Change Baudrate, RX Block (with online verification), Erase Check and Load PC. If a TX Block command (redirected to ROM BSL) is needed (e.g. for TXing error address, standalone Verify), the RAM BSL must be invoked again via the Load PC command. The error address buffer address for "RX Block" and "Erase Check" commands is 021Eh.

BS\_150S\_14x.txt could also be used as a partial replacement for PATCH.txt. Note: No password required, RX Password command is stripped!

For more information on downloading a different bootstrap loader, see *Application of Bootstrap Loader in MSP430 With Flash Hardware and Software Proposal* (SLAA096).

Third party software normally uses loadable BSLs to perform most functions, like online verification, and to improve speed for appropriate devices.

## 9 Exiting the BSL

To exit the BSL mode two possibilities are provided:

- The microcontroller continues operation at a defined program address invoked by the load program counter command. Be aware of that the password protection is not active at this time.

- Applying the standard RESET sequence (see Figure 1) forces the MSP430 to start with the user reset vector at address 0FFFEh.

### **10** Password Protection

The password protection prohibits every command that potentially allows direct or indirect data access. Only the unprotected commands like mass erase and RX password (optionally TX BSL version, change baud rate) can be performed without prior receipt of the correct password after BSL entry.

Applying the RX password command for receiving the correct password unlocks the remaining commands.

Once it is unlocked it remains unlocked until initiating another BSL entry. A reset condition (-RST/NMI =  $0 \rightarrow 1$ , V<sub>cc</sub> =  $0 \rightarrow 1$ ) has no influence on the protection behavior.

The password itself consists of the 16 interrupt vectors located at addresses FFE0h to FFFFh (256 bits) starting with the first byte at address FFE0h. After mass erase and with unprogrammed devices, all password bits are logical high (1).

**NOTE:** The user has to take care of password update after modifying the interrupt vectors and initiating another BSL session. It is also strongly recommended to initialize unused interrupt vectors to increase data safety.

## **11 Code Protection Fuse**

Once the JTAG fuse (code protection fuse) is blown, no further access to the JTAG/test feature is possible. The only way to get any memory read/write access is via the bootstrap loader by applying the correct password.

However, it is not possible for the BSL to blow the JTAG fuse. If fuse blowing is needed, use JTAG programming techniques.

### 12 BSL Internal Settings and Resources

The following paragraphs describe BSL internal settings and resources. Because the same device may have implemented different BSL versions, it is very important for the BSL communication program to know the settings and resources. Resources could be either device dependent (e.g., RX/TX pins) or BSL-version dependent (e.g., byte/word access). The following paragraphs, therefore, distinguish among the possible variations.

#### 12.1 Chip Identification and BSL Version

The upper 16 bytes of the boot-ROM (0FF0h–0FFFh) hold information about the device and BSL version number in BCD representation. This is common for all devices and BSL versions:

- 0FF0h–0FF1h: Chip identification (e.g., F413h for an F41x device).

- 0FFAh–0FFBh: BSL version number (e.g. 0130h for BSL version V1.30).

Please see the MSP430 device / BSL version assignment in Appendix A.

The entry part of the boot ROM holds the calling vectors for BSL access by program:

TEXAS

INSTRUMENTS

- 0C00h: Vector for cold-start (mnemonic: *BR* &0C00h)

- 0C02h: Vector for warm-start (mnemonic: BR &0C02h). V1.30 or higher.

- 0C04h: Vector(s) for future use. This table is expandable.

#### **12.3** Initialization Status

When activating the BSL, the following settings come into effect:

- Stop Watchdog Timer

- Disable all interrupts (GIE=0)

- V1.10:

The stack pointer is not modified except when it points to an excluded memory area. If so, it is initialized to 021Ah.

V1.30 or higher:

The stack pointer is not modified if the BSL is called by program via the warm-start vector. It is initialized to 0220h if the BSL starts via the BSL RESET sequence or is called by program via the cold-start vector.

• F1xx:

Determine basic clock module so that minimum frequency is 1.5 MHz: BCSCTL1 = 85h (RSEL = 5, XT2Off = 1) DCOCTL = 80h (DCO = 4, MOD = 0) BCSCTL2 = 00h only at cold-start SR: SCG1 = 00h (SMCLK on) only at cold-start

F4xx:

Determine FLL oscillator/system clock so that minimum frequency is 1.5 MHz: SCFI0 = 00h (D = 0, FN\_x = 0) SCFI1 = 98h (N\_DCO) SCFQCTL: (M = 0) SR: SCG0 = 1 (FLL loop control off) FLL\_CTL1 = 00h only at cold-start

- SW-UART: Timer\_A operates in continuous mode with MCLK source (Div = 1) CCR0 used for compare CCTL0 used for polling of CCIFG0

- TX pin is set to output HI for RS232 idle state

- RX pin is set to input

- Password protected commands are locked (only at cold-start)

After system initialization, the BSL is ready for operation and waits for the first synchronization sequence (SS) followed by a data frame containing the first BSL command.

#### 12.4 Memory Allocation and Resources

- The BSL program code is located in the boot-ROM area 0C00h–0FEFh.

- Addresses 0FF0h–0FFFh hold the device identification

- The BSL variables occupy the RAM area 0200h–0213h (V1.10) 0200h–0219h (V1.30 or higher).

- The BSL stack occupies the RAM area 0214h–0219h (V1.10) 021Ah–021Fh (V1.30 or higher, only at cold-start).

- The working registers used are R5–R9 (V1.30 or lower) or R5–R10 (V1.40) or R5–R11 (V1.60). Their contents are not buffered.

- F1xx: The basic clock module registers used are: DCOCTL at address 056h BCSCTL1 at address 057h

F4xx: The FLL oscillator/system clock registers used are: SCFI0 at address 050h SCFI1 at address 051h SCFQCTL at address 052h

The Timer\_A control registers used are: TACTL at address 0160h CCTL0 at address 0162h TAR at address 0170h CCR0 at address 0172h

• No interrupt service is affected.

## 13 Special Consideration for BSL Version 1.10

The first official version V1.10 of the BSL requires a small loadable patch sequence, PATCH.TXT, to execute the RX block command reliably. For that, after the BSL has been started, proceed in the following manner:

- RX password (unlock password protection for the following command)

- Load program counter (PC) with 0C22h (initialize stack pointer to a safe address)

- RX password again (unlock password protection for subsequent commands)

- RX data block (code of loadable patch, code section address is 0220h)

- TX data block (code of loadable patch for verification)

From now on, the RX block and TX block commands can be used with one restriction: Prior to their invocation the program counter must be set to the start address of the patch.

- Load program counter (PC) with start address 0220h of loadable patch

- RX data block (code to be programmed at any location) -or-

- TX data block (from any location)

For more information on downloading a patch or different bootstrap loader, see *Application of Bootstrap Loader in MSP430 With Flash Hardware and Software Proposal* (SLAA096).

### 14 References

- 1. MSP430x1xx Family User's Guide (SLAU049)

- 2. MSP430x4xx Family User's Guide (SLAU056)

- 3. Application of Bootstrap Loader in MSP430 With Flash Hardware and Software Proposal (SLAA096)

For a list of third parties that offer BSL hardware and software solutions, please see the MSP430 web site at <a href="http://www.ti.com/sc/msp430">http://www.ti.com/sc/msp430</a> (> Design Resources > Third Party > Tools).

# Appendix A. Differences Between Devices and BSL Versions

As a summary the tables in this chapter show the key information of MSP430 device/BSL version assignment related to their hard/software resources.

|                                                                                    | Dev     | vice                                                         | F13x<br>F14x(1)                                                                                                                 | F11x (obsolete)<br>F11x1 (obsolete) |  |  |

|------------------------------------------------------------------------------------|---------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|

|                                                                                    | BSL V   | ersion                                                       | 1.10                                                                                                                            |                                     |  |  |

| BSL vector                                                                         |         | Cold start                                                   | 0C00h                                                                                                                           |                                     |  |  |

| address                                                                            |         | Warm start                                                   | —                                                                                                                               |                                     |  |  |

| Chip ID addres                                                                     | SS      |                                                              | 0FF0h                                                                                                                           |                                     |  |  |

| Chip ID data                                                                       |         |                                                              | F149h                                                                                                                           | F112h                               |  |  |

| BSL version ad                                                                     | ddress  | i                                                            | 0FFAh                                                                                                                           |                                     |  |  |

| BSL version da                                                                     | ata     |                                                              | 0110h                                                                                                                           |                                     |  |  |

| Mass erase tin                                                                     | ne, noi | minal (ms)                                                   | 17.2                                                                                                                            |                                     |  |  |

| Read/write acc                                                                     | cess at | 0000h-FFFFh                                                  | Byte                                                                                                                            |                                     |  |  |

| Verification du                                                                    | ring wi | rite (online)                                                | No                                                                                                                              |                                     |  |  |

| Stack pointer                                                                      |         | SP critical                                                  | 021Ah                                                                                                                           |                                     |  |  |

| initialization                                                                     |         | SP not critical                                              | Unchanged                                                                                                                       |                                     |  |  |

|                                                                                    |         | Resources                                                    | s used by BSL                                                                                                                   |                                     |  |  |

| Transmit pin (1                                                                    | ΓX) / R | eceive pin (RX)                                              | P 1.1 / P2.2                                                                                                                    |                                     |  |  |

| RAM/stack use                                                                      | ed      |                                                              | 0200h-0219h                                                                                                                     |                                     |  |  |

| Working regist                                                                     | ers     |                                                              | R5–R9                                                                                                                           |                                     |  |  |

| System clock,                                                                      | affecte | ed controls                                                  | BCSCTL1, DCOCTL                                                                                                                 |                                     |  |  |

| Timer_A, affect                                                                    | ted co  | ntrols                                                       | TACTL, TAR, CCTL0, CCR0                                                                                                         |                                     |  |  |

| Preparation for                                                                    | r SW c  | all                                                          | mov #00h, &CCTL0   bic.b #02h, &P1SEL   bic.b #04h, &P2SEL   bic.b #32h, &IE1   mov.b #00h, &BCSCTL2   mov #00h, SR   br &0C00h |                                     |  |  |

| Comment 1                                                                          | Worl    | karound mandatory:                                           | Load PATCH.TXT to eliminate ROM bug.<br>See chapters "Special Considerations for<br>BSL Version 1.10" and "Loadable BSL".       |                                     |  |  |

| Comment 2 Optional for F148, F149<br>only: Use loadable BSL<br>(>1KB RAM required) |         |                                                              | Load BL_150S_14x.txt to get all features of V1.60 plus valid erase segment command: See chapter "Loadable BSL".                 |                                     |  |  |

| Comment 3                                                                          | Use     | onal for F1x4F1x9:<br>small loadable BSL<br>2B RAM required) | Load BS_150S_14x.txt to get some features<br>of V1.60: See chapter "Loadable BSL".                                              |                                     |  |  |

Table 3.BSL Version 1.10 on F13x, F14x(1), F11x, and F11x1

| De                    | vice          |                                       | F41x                                     | F                         | I1x (obsolete)<br>F11x1A                             |  |  |

|-----------------------|---------------|---------------------------------------|------------------------------------------|---------------------------|------------------------------------------------------|--|--|

| BSL \                 | /ersion       | 1.30                                  |                                          |                           |                                                      |  |  |

| BSL vector            | Cold start    | 0C00h                                 |                                          |                           |                                                      |  |  |

| address               | Warm start    | 0C02h                                 |                                          |                           |                                                      |  |  |

| Chip ID address       |               | 0FF0h                                 |                                          |                           |                                                      |  |  |

| Chip ID data          |               | F413h                                 |                                          | F112h                     |                                                      |  |  |

| BSL version addres    | S             | 0FFAh                                 |                                          |                           |                                                      |  |  |

| BSL version data      |               | 0130h                                 |                                          |                           |                                                      |  |  |

| Mass erase time, no   | ominal (ms)   | 206.4                                 |                                          |                           |                                                      |  |  |

| Read/write access     | 0000h-00FFh   | Byte                                  |                                          |                           |                                                      |  |  |

| at                    | 0100h-FFFEh   | Word                                  |                                          |                           |                                                      |  |  |

| Verification during w | rite (online) | No                                    |                                          |                           |                                                      |  |  |

| Stack pointer         | Cold start    | 0220h                                 |                                          |                           |                                                      |  |  |

| initialization        | Warm start    | Unchar                                | nged                                     |                           |                                                      |  |  |

|                       | Reso          | ources used by BSL                    |                                          |                           |                                                      |  |  |

| Transmit pin (TX)     |               | P1.0 P1.1                             |                                          |                           |                                                      |  |  |

| Receive pin (RX)      |               | P 1.1 P 2.2                           |                                          |                           |                                                      |  |  |

| RAM/stack used        |               | 0200h-021Fh                           |                                          |                           |                                                      |  |  |

| Working registers     |               | R5-R9                                 |                                          |                           |                                                      |  |  |

| System clock, affect  | ed controls   | SCFI0, SCFI1, SCFQCTL BCSCTL1, DCOCTL |                                          |                           |                                                      |  |  |

| Timer_A, affected co  | ontrols       | TACTL, TAR, CCTL0, CCR0               |                                          |                           |                                                      |  |  |

| Preparation for SW    | call          | mov<br>mov.b<br>br                    | #00h, &CCTL0<br>#00h, &FLLCTL1<br>&0C00h | mov<br>mov.b<br>mov<br>br | #00h, &CCTL0<br>#00h, &BCSCTL2<br>#00h, SR<br>&0C00h |  |  |

|                       |               |                                       |                                          |                           |                                                      |  |  |

# Table 4.BSL Version 1.30 on F41x, F11x, and F11x1

| De                    | vice           | F122, F123x                                       |  |  |

|-----------------------|----------------|---------------------------------------------------|--|--|

| BSL                   | /ersion        | 1.40                                              |  |  |

| BSL vector            | Cold start     | 0C00h                                             |  |  |

| address               | Warm start     | 0C02h                                             |  |  |

| Chip ID address       |                | 0FF0h                                             |  |  |

| Chip ID data          |                | F123h                                             |  |  |

| BSL version addres    | S              | 0FFAh                                             |  |  |

| BSL version data      |                | 0140h                                             |  |  |

| Mass erase time, no   | ominal (ms)    | 206.4                                             |  |  |

| Read/Write            | 0000h-00FFh    | Byte                                              |  |  |

| access at             | 0100h-FFFEh    | Word                                              |  |  |

| Verification during V | Vrite (online) | For addresses 0200h-FFFEh                         |  |  |

| Stack pointer         | Cold start     | 0220h                                             |  |  |

| initialization        | Warm start     | Unchanged                                         |  |  |

|                       | Resource       | s used by BSL                                     |  |  |

| Transmit pin (TX)     |                | P 1.1                                             |  |  |

| Receive pin (RX)      |                | P 2.2                                             |  |  |

| RAM/stack used        |                | 0200h-021Fh                                       |  |  |

| Working registers     |                | R5–R10                                            |  |  |

| System clock, affect  | ed controls    | BCSCTL1, DCOCTL                                   |  |  |

| Timer_A, affected c   | ontrols        | TACTL, TAR, CCTL0, CCR0                           |  |  |

| Preparation for SW    | call           | mov.b #00h, &BCSCTL2<br>mov #00h, SR<br>br &0C00h |  |  |

#### Table 5. BSL Version 1.40 on F12x

| Table 6.                                                          |

|-------------------------------------------------------------------|

| BSL Version 1.60 on F11x2, F12x2, F43x, F44x, FE42x, FW42x, FG43x |

|                    | Devi                                                                                    | се              | F1122,<br>F1132                                                                                 | ,       | F1222,<br>F1232         | F43x,<br>F44x | FE42x,<br>FW42x | FG43x |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------|---------|-------------------------|---------------|-----------------|-------|--|--|--|

| BS                 | 1.60                                                                                    |                 |                                                                                                 |         |                         |               |                 |       |  |  |  |

| BSL vector         |                                                                                         |                 |                                                                                                 |         | 0C00h                   |               |                 |       |  |  |  |

| address Warm start |                                                                                         |                 | 0C02h                                                                                           |         |                         |               |                 |       |  |  |  |

| Chip ID address    |                                                                                         |                 | 0FF0h                                                                                           |         |                         |               |                 |       |  |  |  |

| Chip ID data       |                                                                                         |                 | 1132h                                                                                           | 12      | 232h                    | F449h         | F427h           | F439h |  |  |  |

| BSL version add    | ress                                                                                    |                 | 0FFAh                                                                                           |         |                         |               |                 |       |  |  |  |

| BSL version data   | l                                                                                       |                 | 0160h                                                                                           |         |                         |               |                 |       |  |  |  |

| Mass erase time    | nom.                                                                                    | (ms)            | 206.4                                                                                           |         |                         |               |                 |       |  |  |  |

| Read/write acces   | ss O                                                                                    | 0000h-00FFh     | Byte                                                                                            |         |                         |               |                 |       |  |  |  |

| at                 | 0                                                                                       | 100h-FFFEh      | Word                                                                                            |         |                         |               |                 |       |  |  |  |

| Verification durin | g Wri                                                                                   | te (online)     | For addre                                                                                       | esses ( | 200h-FF                 | FEh           |                 |       |  |  |  |

| Erase check com    | nmano                                                                                   | b               | Yes (error addr 0200h)                                                                          |         |                         |               |                 |       |  |  |  |

| Erase segment c    | omma                                                                                    | and             | With eras                                                                                       | sure ve | rification (            | error addr 02 | 00h)            |       |  |  |  |

| TX identification  | comm                                                                                    | and             | Yes                                                                                             |         |                         |               |                 |       |  |  |  |

| Change baud rat    | e con                                                                                   | nmand           | Yes                                                                                             |         |                         |               |                 |       |  |  |  |

| Stack pointer      | 0                                                                                       | Cold start      | 0220h                                                                                           |         |                         |               |                 |       |  |  |  |

| initialization     | ٧                                                                                       | Varm start      | Unchanged                                                                                       |         |                         |               |                 |       |  |  |  |

|                    |                                                                                         | F               | Resources                                                                                       | s used  | by BSL                  |               |                 |       |  |  |  |

| Transmit pin (TX)  | )                                                                                       |                 | P 1.1                                                                                           |         |                         | P1.0          |                 |       |  |  |  |

| Receive pin (RX)   | )                                                                                       |                 | P 2.2                                                                                           |         |                         | P1.1          |                 |       |  |  |  |

| RAM/stack used     |                                                                                         |                 | 0200h-021Fh                                                                                     |         |                         |               |                 |       |  |  |  |

| Working registers  | S                                                                                       |                 | R5–R12                                                                                          |         |                         |               |                 |       |  |  |  |

| System clock, aff  | ected                                                                                   | l controls      | BCSCTL1, DCOCTL SCFI0, SCFI1, SCFQCTL                                                           |         |                         |               |                 |       |  |  |  |

| Timer_A, affected  | Timer_A, affected controls                                                              |                 |                                                                                                 |         | TACTL, TAR, CCTL0, CCR0 |               |                 |       |  |  |  |

| Preparation for S  | mov.b #00h,&BCSCTL2 mov.b #00h, &FLLCTL1   mov #00h, SR br &0C00h   br &0C00h br \$000h |                 |                                                                                                 |         |                         | 1             |                 |       |  |  |  |

| Comment E          | Erase                                                                                   | segment command | Addresses 1000h to 11FFh are verified coherently (3 segments).<br>Also use erase check command. |         |                         |               |                 |       |  |  |  |

| Device                             |                      | F15x, F16x                                                                                      | Preliminary<br>F1610, F1611, F1612 |  |

|------------------------------------|----------------------|-------------------------------------------------------------------------------------------------|------------------------------------|--|

| BSL Version                        |                      | 1.61                                                                                            |                                    |  |

| BSL vector                         | Cold start           | 0C00h                                                                                           |                                    |  |

| address                            | Warm start           | 0C02h                                                                                           |                                    |  |

| Chip ID address                    |                      | 0FF0h                                                                                           |                                    |  |

| Chip ID data                       |                      | F169h F16Ch                                                                                     |                                    |  |

| BSL version address                |                      | 0FFAh                                                                                           |                                    |  |

| BSL version data                   |                      | 0161h                                                                                           |                                    |  |

| Mass erase time nom. (ms)          |                      | 206.4                                                                                           |                                    |  |

| Read/write acces                   | s 0000h-00FFh        | Byte                                                                                            |                                    |  |

| at                                 | 0100h-FFFEh          | Word                                                                                            |                                    |  |

| Verification during Write (online) |                      | For addresses 0200h-FFFEh                                                                       |                                    |  |

| Erase check command                |                      | Yes (error addr 0200h)                                                                          |                                    |  |

| Erase segment command              |                      | With erasure verification (error addr 0200h)                                                    |                                    |  |

| TX identification command          |                      | Yes                                                                                             |                                    |  |

| Change baud rate command           |                      | Yes                                                                                             |                                    |  |

| Stack pointer                      | Cold start           | 0220h                                                                                           |                                    |  |

| initialization                     | Warm start           | Unchanged                                                                                       |                                    |  |

|                                    |                      | Resources used by BSL                                                                           |                                    |  |

| Transmit pin (TX)                  |                      | P 1.1                                                                                           |                                    |  |

| Receive pin (RX)                   |                      | P 2.2                                                                                           |                                    |  |

| RAM/stack used                     |                      | 0200h-021Fh                                                                                     |                                    |  |

| Working registers                  |                      | R5-R12                                                                                          |                                    |  |

| System clock, affected controls    |                      | BCSCTL1, DCOCTL                                                                                 |                                    |  |

| Timer_A, affected controls         |                      | TACTL, TAR, CCTL0, CCR0                                                                         |                                    |  |

| Preparation for SW call            |                      | mov.b #00h, &BCSCTL2<br>mov #00h, SR<br>br &0C00h                                               |                                    |  |

| Comment E                          | rase segment command | Addresses 1000h to 11FFh are verified coherently (3 segments).<br>Also use erase check command. |                                    |  |

Table 7.BSL Version 1.61 on F15x, F16x, F161x

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated