# **MIPS® PDtrace™ Specification**

Document Number: MD00439 Revision 6.16 November 23, 2010

MIPS Technologies, Inc. 955 East Arques Avenue Sunnyvale, CA 94085-4521

Copyright © 2001-2010 MIPS Technologies Inc. All rights reserved.

Copyright © 2001-2010 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS73, MIPS32, MIPS64, microMIPS32, microMIPS64, MIPS-3D, MIPS16, MIPS16e, MIPS-Based, MIPSsim, MIPSpro, MIPS Technologies logo, MIPS-VERIFIED, MIPS-VERIFIED logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, M14K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24KEf, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004Kc, 1004Kc, 1004Kc, 1074Kc, 1080Kc, 1080Kc,

All other trademarks referred to herein are the property of their respective owners.

Template: nB1.03, Built with tags: 2B MIPS32

## **Table of Contents**

| Chapter 1: About This Book                                           |    |

|----------------------------------------------------------------------|----|

| 1.1: Typographical Conventions                                       |    |

| 1.1.1: Italic Text                                                   |    |

| 1.1.2: Bold Text                                                     |    |

| 1.1.3: Courier Text                                                  |    |

| 1.2: UNPREDICTABLE and UNDEFINED                                     |    |

| 1.2.1: UNPREDICTABLE                                                 |    |

| 1.2.2: UNDEFINED                                                     |    |

| 1.3: Special Symbols in Pseudocode Notation                          |    |

| 1.4: For More Information                                            |    |

| Chapter 2: Overview of the MIPS® PDtrace™ Architecture               | 15 |

| 2.1: Introduction                                                    |    |

| 2.2: Processor Modes                                                 |    |

| 2.3: Subsetting                                                      |    |

| 2.3. Outsetting                                                      |    |

|                                                                      |    |

| Chapter 3: PDtrace™ Description                                      |    |

| 3.1: Instruction Completion Indicator (InsComp)                      |    |

| 3.2: Trace Type and an Example Code Fragment                         |    |

| 3.3: Trace Mode                                                      |    |

| 3.4: Start of Tracing                                                |    |

| 3.5: Trace Synchronization                                           |    |

| 3.6: Trace Overflow and Restart                                      |    |

| 3.7: Data Order Signal                                               |    |

| 3.8: Tracing During Processor Mode Changes                           |    |

| 3.9: Tracing Store Conditionals                                      |    |

| 3.10: Tracing MIPS16e <sup>™</sup> Macro Instructions                |    |

| 3.11: Tracing MIPS16e <sup>™</sup> Extend Instructions               |    |

| 3.12: Tracing Instruction Cache and Data Cache Misses                |    |

| 3.13: Tracing Potential Function Call/Return Instructions            |    |

| 3.14: Tracing with MIPS® MT ASE                                      |    |

| 3.15: Tracing in WAIT State                                          |    |

| 3.16: Trace Trigger from EJTAG Hardware Instruction/Data Breakpoints |    |

| 3.17: Tracing Performance Counter Values                             |    |

| 3.18: Filtered Data Trace Mode                                       |    |

| 3.19: Trace Enabling/Disabling Condition                             |    |

| Chapter 4: PDtrace™ Output Trace Formats                             |    |

| 4.1: Single-Pipe Tracing Formats                                     |    |

| 4.1.1: Trace Format 1 (TF1)                                          |    |

| 4.1.2: Trace Format 2 (TF2)                                          |    |

| 4.1.3: Trace Format 3 (TF3)                                          |    |

| 4.1.4: Trace Format 4 (TF4)                                          |    |

| 4.1.5: Trace Format 5 (TF5)                                          |    |

| 4.1.6: Trace Format 6 (TF6)                                          |    |

| 4.2: Format Enhancements for the MT ASE                                           |     |

|-----------------------------------------------------------------------------------|-----|

| 4.2.1: Trace Format 7 (TF7)                                                       |     |

| 4.2.2: TF2TF4 Augmented for MT ASE                                                |     |

| 4.3: Multi-Pipe Tracing Formats                                                   |     |

| 4.3.1: Multi-Pipe Trace Format 2-4 (TF2, TF3, TF4)                                | 45  |

| 4.3.2: Trace Format Extensions for Coherent Systems                               |     |

| Chapter 5: TCB Trace Word                                                         |     |

| 5.1: Trace Word                                                                   |     |

| 5.1.1: Cycle Inaccurate Trace                                                     | 50  |

| 5.2: End of Trace Indication                                                      |     |

| 5.3: On-chip Trace Memory Format                                                  |     |

| 5.4: Probe Trace Word Transmission                                                |     |

| Chapter 6: Trace Compression                                                      |     |

| 6.1: PC Tracing                                                                   |     |

| 6.2: Load or Store Address Tracing                                                | 53  |

| 6.3: Load and Store Data Tracing                                                  |     |

| 6.4: Using Early TEnd Assertion                                                   |     |

| Chapter 7: PDtrace™ Control Using CP0 Registers                                   |     |

| 7.1: Trace Controls Overview                                                      |     |

| 7.2: Software Trace Control                                                       |     |

| 7.2.1: Coprocessor 0 Trace Registers                                              |     |

| Chapter 8: Trace Control Block (TCB) Registers                                    |     |

| 8.1: TCBCONTROLA Register                                                         |     |

| 8.2: TCBCONTROLB Register                                                         |     |

| 8.3: TCBCONTROLC Register                                                         |     |

| 8.4: TCBControlD Register                                                         |     |

| 8.5: TCBCONTROLE Register                                                         |     |

| 8.6: TCBDATA Register                                                             |     |

| 8.7: TCBCONFIG Register (Reg 0)                                                   |     |

| 8.8: TCBTW Register (Reg 4)                                                       |     |

| 8.9: TCBRDP Register (Reg 5)                                                      |     |

| 8.10: TCBWRP Register (Reg 6)                                                     |     |

| 8.11: TCBSTP Register (Reg 7)                                                     |     |

| 8.12: TCBTRIGx Register (Reg 16-23)                                               |     |

| 8.13: Reset State<br>8.14: TCB Registers in Processors Implementing the MT ASE    |     |

| 8.15: Memory-Mapped Access to PDtrace <sup>™</sup> Control and On-Chip Trace RAM  |     |

| 8.16: On-Chip Trace Buffer Usage                                                  |     |

| Chapter 9: E ITAG Traco Pogistors                                                 | 04  |

| Chapter 9: EJTAG Trace Registers           9.1: TraceIBPC and TraceDBPC Registers |     |

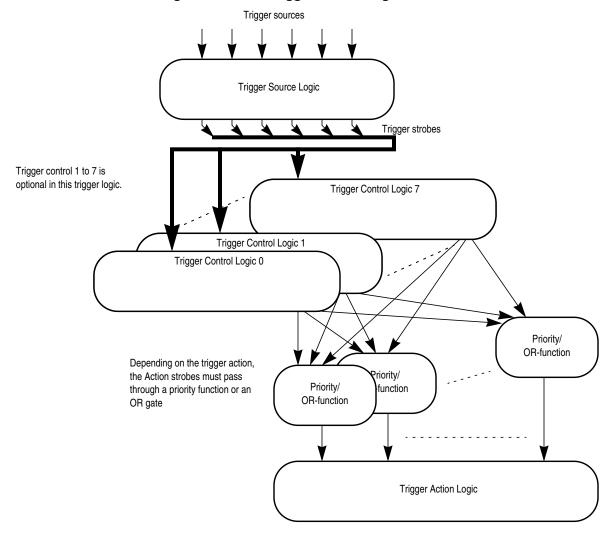

| Chapter 10: TCB Trigger Logic                                                     | 101 |

| 10.1: Trigger Logic Overview                                                      |     |

| 10.1.1: Trigger Source Logic                                                      |     |

| 10.1.2: Trigger Control Logic                                                     |     |

| 10.1.3: Trigger Action logic                                                      |     |

| 10.2: Simultaneous Triggers                                                       |     |

|                                                                                   |     |

| 10.2.1: Prioritized Trigger Actions                                                                     |       |

|---------------------------------------------------------------------------------------------------------|-------|

| 10.2.2: OR'ed Trigger Actions<br>10.3: TCB Trigger Input/Output Signals                                 |       |

| TO.S. TOB Trigger input/Output Signals                                                                  | 104   |

| Appendix A: Implementation-Specific PDtrace <sup>™</sup> Enhancements for MIPS32® 74K <sup>™</sup> Core | es106 |

| A.1: Tracing the 74K to Show Pipeline Details and Execution Inefficiencies                              | 106   |

| A.1.1: Updated Trace Format 2 (TF2) for 74K-specific Information                                        | 107   |

| A.1.2: Trace Format 3 (TF3)                                                                             |       |

| A.2: Updated TF4 to Handle 74K <sup>™</sup> Core-Specific DataOrder and Inefficiency Information        |       |

| A.3: Tracing 74K <sup>™</sup> Core in Cycle Accurate Mode                                               | 110   |

| A.4: Compressing Addresses in TF3 and TF4                                                               | 110   |

| A.5: Enhancements for Coherent Cores                                                                    | 110   |

| A.5.1: Extending Trace Formats                                                                          | 110   |

| A.5.2: T8 - New Trace Format                                                                            | 111   |

|                                                                                                         |       |

| Appendix B: PDtrace <sup>™</sup> Enhancements for Chip-Multiprocessing Systems                          | 112   |

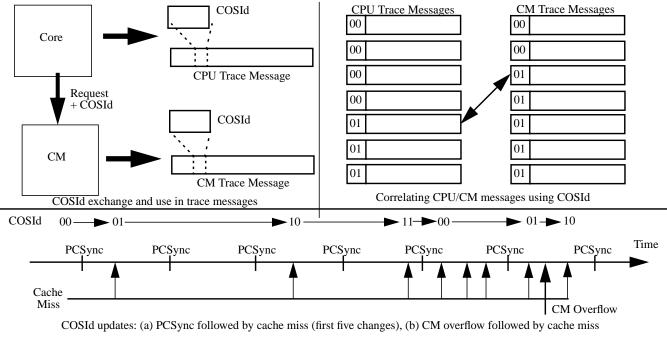

| B.1: Tracing a Coherent Subsystem                                                                       | 112   |

| B.1.1: Trace Requirements                                                                               | 112   |

| B.2: CM Trace Formats                                                                                   | 114   |

| B.2.1: CM Trace Format 1                                                                                | 114   |

| B.2.2: CM Trace Format 2                                                                                | 115   |

| B.2.3: CM Trace Format 3 (CM_TF3)                                                                       | 115   |

| B.2.4: CM Trace Format 4 (CM_TF4)                                                                       | 116   |

| B.3: Consolidating Trace Information                                                                    | 116   |

| B.4: On-Chip Trace Memory                                                                               | 116   |

| B.4.1: CM PDTrace TCB ControlB Register                                                                 | 117   |

| B.4.2: CM PDTrace TCB ControlE Register                                                                 | 121   |

| B.5: Software Control of Coherence Manager Trace                                                        | 121   |

| B.6: Trace-Master TAP Instruction Register                                                              | 123   |

|                                                                                                         |       |

| Appendix C: Implementation-Specific PDtrace™ Enhancements for MIPS32® 1004K™ R                          |       |

| 1.2.0 and Older Cores                                                                                   |       |

| C.1: On-Chip Trace Memory                                                                               |       |

| C.1.1: CM PDTrace TCB ControlB Register                                                                 |       |

| C.1.2: CM PDTrace TCB ControlE Register                                                                 |       |

| C.2: Software Control of Coherence Manager Trace                                                        | 128   |

|                                                                                                         |       |

# Appendix D: Implementation-Specific PDtrace<sup>™</sup> Enhancements for the MIPS32® 1074K<sup>™</sup> Cores 130

| Appendix E: Tracing Multi-Issue and High Performance Processors        |  |

|------------------------------------------------------------------------|--|

| E.1: Background on High Performance Processors                         |  |

| E.2: Basic Tracing Methodology                                         |  |

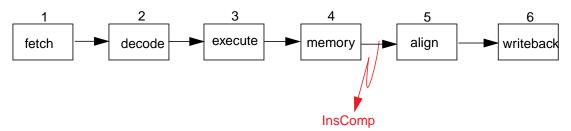

| E.3: Coordinating Instruction Completion Trace with Address/Data Trace |  |

| E.4: Out-of-Order Loads and Stores in the Multi-Pipe Core              |  |

| E.5: Tagging Instructions that Issue Together                          |  |

| E.6: Miscellaneous                                                     |  |

|                                                                        |  |

| Appendix F: PDtrace™ Interface Signals (The Interface is now Deprecated as Architecture a | nd    |

|-------------------------------------------------------------------------------------------|-------|

| this Chapter is here Solely for Historical Reasons)                                       | . 137 |

| F.1: PDtrace™ Core Interface Signal List                                                  | 138   |

| Appendix G: Revision Histor | y | ) |

|-----------------------------|---|---|

|-----------------------------|---|---|

## **List of Figures**

| Figure 2.1: Illustration of a PC and Data Trace Flow                                                     | 16 |

|----------------------------------------------------------------------------------------------------------|----|

| Figure 2.2: Config3 Register Format                                                                      |    |

| Figure 2.3: TCB and Optional PIB Overview                                                                | 18 |

| Figure 2.4: Illustration of the Core and TCB with External Trace Memory                                  | 18 |

| Figure 2.5: Illustration of the Core and TCB with Internal Trace Memory                                  | 19 |

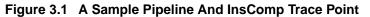

| Figure 3.1: A Sample Pipeline And InsComp Trace Point                                                    | 21 |

| Figure 3.2: Illustration of a Pipeline and Trace Tap Points                                              |    |

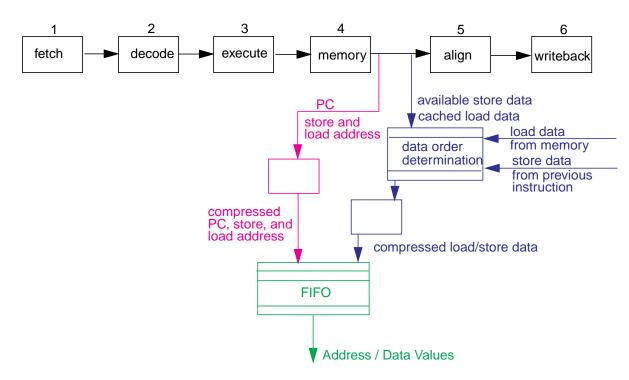

| Figure 3.3: A TMOAS Trace Record                                                                         | 26 |

| Figure 3.4: An Example of Load Data Bypassing an Earlier Store                                           |    |

| Figure 4.1: TF1 (Trace Format 1)                                                                         |    |

| Figure 4.2: TF2 (Trace Format 2 Single-Pipe)                                                             |    |

| Figure 4.3: TF2 with Optional Bits (Trace Format 2 Single-Pipe)                                          |    |

| Figure 4.4: TF3 (Trace Format 3 Single-Pipe)                                                             |    |

| Figure 4.5: TF3 with Optional Bits (Trace Format 3 Single-Pipe)                                          |    |

| Figure 4.6: TF3 with Optional Performance Counter and other bits (Trace Format 3 Single-Pipe)            |    |

| Figure 4.7: TF4 (Trace Format 4 Single-Pipe)                                                             |    |

| Figure 4.8: TF4 with Optional Bits (Trace Format 4 Single-Pipe)                                          |    |

| Figure 4.9: TF5 (Trace Format 5)                                                                         |    |

| Figure 4.10: TF6 (Trace Format 6)                                                                        |    |

| Figure 4.11: TF7 (Trace Format 7)                                                                        |    |

| Figure 4.12: TF2 with Optional Bits and TCid Bits (Trace Format 2 Single-Pipe)                           |    |

| Figure 4.13: TF2 (Trace Format 2 Multi-Pipe)                                                             |    |

| Figure 4.14: TF3 (Trace Format 3 Multi-Pipe)                                                             |    |

| Figure 4.15: TF4 (Trace Format 4 Multi-Pipe)                                                             |    |

| Figure 5.1: Trace Word with Zero Source Bits                                                             |    |

| Figure 5.2: Trace Word with Two Source Bits                                                              | 47 |

| Figure 5.3: Trace Word with Four Source Bits                                                             |    |

| Figure 5.4: Trace Word from Example Trace in Table 5.2                                                   |    |

| Figure 5.5: Trace Word from Example Trace in Table 5.2 (No TF1 trace)                                    |    |

| Figure 5.6: Cycle-by-cycle Trace Word from Example Trace in Table 5.2                                    |    |

| Figure 5.7: Cycle-by-Cycle TR_DATA (8-bit) of Example Trace in Table 5.2                                 |    |

| Figure 7.1: TraceControl Register Format                                                                 |    |

| Figure 7.2: TraceControl2 Register Format                                                                |    |

| Figure 7.3: TraceControl3 Register Format                                                                |    |

| Figure 7.4: UserTraceData1 and UserTraceData2 Register Format<br>Figure 8.1: TCBCONTROLA Register Format |    |

| Figure 8.2: TCBCONTROLA Register Format                                                                  |    |

| Figure 8.3: TCBCONTROLD Register Format                                                                  |    |

| Figure 8.4: TCBCONTROLD Register Format                                                                  |    |

| Figure 8.5: PDtrace Control Configuration Register Format                                                |    |

| Figure 8.6: TCBCONTROLE Register Format                                                                  |    |

| Figure 8.7: TCBDATA Register Format                                                                      |    |

| Figure 8.8: TCBCONFIG Register Format                                                                    |    |

| Figure 8.9: TCBTW Register Format                                                                        |    |

| Figure 8.10: TCBRDP Register Format                                                                      |    |

| Figure 8.11: TCBWRP Register Format                                                                      |    |

| Figure 8.12: TCBSTP Register Format                                                                      |    |

| riguro 0.12. TODOTT Register Format                                                                      |    |

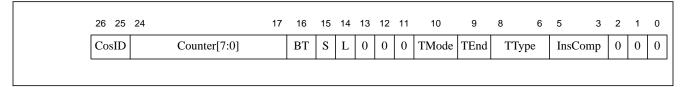

| Figure 8.13: TCBTRIGx Register Format                                                                  | 87  |

|--------------------------------------------------------------------------------------------------------|-----|

| Figure 9.1: TraceIBPC Register Format                                                                  |     |

| Figure 9.2: TraceDBPC Register Format                                                                  | 96  |

| Figure 9.3: TraceIBPC2 Register Format                                                                 | 97  |

| Figure 9.4: TraceDBPC2 Register Format                                                                 | 98  |

| Figure 10.1: TCB Trigger Processing Overview                                                           | 102 |

| Figure A.1: Expanded TF2 (Trace Format 2 Single-Pipe)                                                  | 107 |

| Figure A.2: Expanded TF2 with Optional Bits (Trace Format 2 Single-Pipe)                               | 107 |

| Figure A.3: TF3 (Trace Format 3 Single-Pipe)                                                           | 108 |

| Figure A.4: TF3 with Optional Bits (Trace Format 3 Single-Pipe)                                        | 108 |

| Figure A.5: Expanded TF3 with Optional Performance Counter and other bits (Trace Format 3 Single-Pipe) |     |

| Figure A.6: TF4 (Trace Format 4 Single-Pipe)                                                           | 109 |

| Figure A.7: Expanded TF4 (Trace Format 4 Single-Pipe)                                                  | 109 |

| Figure A.8: TF4 with Optional Bits (Trace Format 4 Single-Pipe)                                        | 109 |

| Figure A.9: Expanded TF4 with Optional Bits (Trace Format 4 Single-Pipe)                               | 110 |

| Figure A.10: TF8 (Trace Format 8)                                                                      | 111 |

| Figure B-1: COSId - Creation, Correlation, and Updates                                                 | 114 |

| Figure B-2: CM Trace Format 1 (CM_TF1) - Trace Level 0                                                 | 114 |

| Figure B-3: CM Trace Format 1 (CM_TF1) - Trace Level 1                                                 | 115 |

| Figure B-4: CM Trace Format 2 (CM_TF2) - Trace Level 0                                                 | 115 |

| Figure B-5: CM Trace Format 2 (CM_TF2) - Trace Level 1                                                 | 115 |

| Figure B-6: CM Trace Format 3 (CM_TF3) with Trace Level 0                                              | 115 |

| Figure B-7: CM Trace Format 3 (CM_TF3) with Trace Level 1                                              | 115 |

| Figure B-8: CM TF_4 - Overflow Format                                                                  |     |

| Figure B.9: TCBControlD Register Format                                                                | 121 |

| Figure C-1: CMTraceControl Register Format                                                             |     |

| Figure E.1: An Example Showing the Coordination of Instructions and Their Data                         | 134 |

## **List of Tables**

| Table 1.1: Symbols Used in Instruction Operation Statements                            | 12  |

|----------------------------------------------------------------------------------------|-----|

| Table 2.1: Config3 Register Field Descriptions                                         | 16  |

| Table 3.1: Instruction Type Completion Indicator (InsComp)                             | 20  |

| Table 3.2: Trace Data Type Indicator (TType)                                           | 23  |

| Table 3.3: Example Code Fragment With Some PDtrace™ Trace Values                       | 24  |

| Table 3.4: A TMOAS Trace Record Field Descriptions                                     | 26  |

| Table 3.5: Trace Mode Bits                                                             |     |

| Table 3.6: Load Order Example                                                          | 29  |

| Table 3.7: Data Order with Four Bits                                                   | 30  |

| Table 3.8: Data (Load/Store) Order Example                                             | 31  |

| Table 3.9: Possible Instructions for Function Call/Returns                             | 34  |

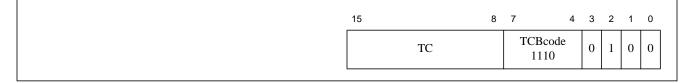

| Table 4.1: TCBcode and TCBinfo fields of Trace Format 6 (TF6)                          | 43  |

| Table 5.1: Trace Word Type Field Descriptions                                          | 48  |

| Table 5.2: Example Trace Sequence                                                      | 49  |

| Table 7.1: A List of Coprocessor 0 Trace Registers                                     | 57  |

| Table 7.2: TraceControl Register Field Descriptions                                    | 58  |

| Table 7.3: TraceControl2 Register Field Descriptions                                   | 61  |

| Table 7.4: TraceControl3 Register Field Descriptions                                   | 64  |

| Table 7.5: UserTraceData1 Register Field Descriptions                                  | 65  |

| Table 7.6: UserTraceData2 Register Field Descriptions                                  | 65  |

| Table 8.1: Trace Control Block Registers                                               |     |

| Table 8.2: Registers Selected by TCBCONTROLB <sub>REG</sub> (accessed through TCBDATA) | 67  |

| Table 8.3: TCBCONTROLA Register Field Descriptions                                     |     |

| Table 8.4: TCBCONTROLB Register Field Descriptions                                     | 72  |

| Table 8.5: Clock Ratio encoding of the CR field                                        |     |

| Table 8.6: TCBCONTROLC Register Field Descriptions                                     | 77  |

| Table 8.7: TCBCONTROLD Register Field Descriptions                                     | 79  |

| Table 8.8: PDtrace Control Configuration Register                                      | 80  |

| Table 8.9: TCBCONTROLE Register Field Descriptions                                     | 81  |

| Table 8.10: TCBDATA Register Field Descriptions                                        |     |

| Table 8.11: TCBCONFIG Register Field Descriptions                                      | 83  |

| Table 8.12: TCBTW Register Field Descriptions                                          |     |

| Table 8.13: TCBRDP Register Field Descriptions                                         | 85  |

| Table 8.14: TCBWRP Register Field Descriptions                                         |     |

| Table 8.15: TCBSTP Register Field Descriptions                                         |     |

| Table 8.16: TCBTRIGx Register Field Descriptions                                       | 87  |

| Table 8.17: Mapping TCB Registers in drseg                                             | 91  |

| Table 9.1: Mapping Trace Breakpoint Registers in CP0 Space or in drseg                 | 94  |

| Table 9.2: TraceIBPC Register Field Descriptions                                       |     |

| Table 9.3: TraceDBPC Register Field Descriptions                                       |     |

| Table 9.4: TraceIBPC2 Register Field Descriptions                                      |     |

| Table 9.5: TraceDBPC2 Register Field Descriptions                                      | 98  |

| Table 9.6: BreakPoint Control Modes: IBPC and DBPC                                     |     |

| Table 10.1: TCB Trigger input and output                                               |     |

| Table A.1: Expanded Instruction Type Completion Indicator (InsComp)                    |     |

| Table B.1: Coherent Trace Subset Options                                               | 113 |

| Table B.2: PDTrace TCBCONTROLB Register (GCR_DB_TCBControlB Offset 0x0008)             | 117 |

| 121 |

|-----|

| 121 |

| 123 |

| 124 |

| 125 |

| 128 |

| 128 |

| 133 |

| 138 |

| 147 |

| 147 |

| 148 |

| 148 |

| 148 |

|     |

## **About This Book**

## **1.1 Typographical Conventions**

This section describes the use of *italic*, **bold** and courier fonts in this book.

#### 1.1.1 Italic Text

- is used for *emphasis*

- is used for *bits*, *fields*, *registers*, that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S*, *D*, and *PS*

- is used for the memory access types, such as *cached* and *uncached*

#### 1.1.2 Bold Text

- represents a term that is being **defined**

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through 1

- is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.

#### 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

## **1.2 UNPREDICTABLE and UNDEFINED**

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CP0 usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

#### **1.2.1 UNPREDICTABLE**

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

**UNPREDICTABLE** results or operations have several implementation restrictions:

- Implementations of operations generating **UNPREDICTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which

is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user

mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in

another process

- UNPREDICTABLE operations must not halt or hang the processor

#### **1.2.2 UNDEFINED**

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

UNDEFINED operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

### **1.3 Special Symbols in Pseudocode Notation**

In this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1.1.

| Symbol          | Meaning                                                                                                                                                                                                                                                           |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\leftarrow$    | Assignment                                                                                                                                                                                                                                                        |

| =,≠             | Tests for equality and inequality                                                                                                                                                                                                                                 |

| I               | Bit string concatenation                                                                                                                                                                                                                                          |

| x <sup>y</sup>  | A <i>y</i> -bit string formed by <i>y</i> copies of the single-bit value <i>x</i>                                                                                                                                                                                 |

| b#n             | A constant value $n$ in base $b$ . For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. |

| x <sub>yz</sub> | Selection of bits y through z of bit string x. Little-endian bit notation (rightmost bit is 0) is used. If y is less than z, this expression is an empty (zero length) bit string.                                                                                |

#### Table 1.1 Symbols Used in Instruction Operation Statements

| Symbol        | Meaning                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +, -          | 2's complement or floating point arithmetic: addition, subtraction                                                                                                                                                                                                                                                                                                                |

| *,×           | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                                                                                                                                            |

| div           | 2's complement integer division                                                                                                                                                                                                                                                                                                                                                   |

| mod           | 2's complement modulo                                                                                                                                                                                                                                                                                                                                                             |

| /             | Floating point division                                                                                                                                                                                                                                                                                                                                                           |

| <             | 2's complement less-than comparison                                                                                                                                                                                                                                                                                                                                               |

| >             | 2's complement greater-than comparison                                                                                                                                                                                                                                                                                                                                            |

| ≤             | 2's complement less-than or equal comparison                                                                                                                                                                                                                                                                                                                                      |

| 2             | 2's complement greater-than or equal comparison                                                                                                                                                                                                                                                                                                                                   |

| nor           | Bitwise logical NOR                                                                                                                                                                                                                                                                                                                                                               |

| xor           | Bitwise logical XOR                                                                                                                                                                                                                                                                                                                                                               |

| and           | Bitwise logical AND                                                                                                                                                                                                                                                                                                                                                               |

| or            | Bitwise logical OR                                                                                                                                                                                                                                                                                                                                                                |

| GPRLEN        | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                                                                                                                                                |

| GPR[x]        | CPU general-purpose register x. The content of <i>GPR[0]</i> is always zero.                                                                                                                                                                                                                                                                                                      |

| FPR[x]        | Floating Point operand register x                                                                                                                                                                                                                                                                                                                                                 |

| FCC[CC]       | Floating Point condition code CC. FCC[0] has the same value as COC[1].                                                                                                                                                                                                                                                                                                            |

| FPR[x]        | Floating Point (Coprocessor unit 1), general register x                                                                                                                                                                                                                                                                                                                           |

| CPR[z,x,s]    | Coprocessor unit <i>z</i> , general register <i>x</i> , select <i>s</i>                                                                                                                                                                                                                                                                                                           |

| CCR[z,x]      | Coprocessor unit <i>z</i> , control register <i>x</i>                                                                                                                                                                                                                                                                                                                             |

| COC[z]        | Coprocessor unit <i>z</i> condition signal                                                                                                                                                                                                                                                                                                                                        |

| Xlat[x]       | Translation of the MIPS16 GPR number <i>x</i> into the corresponding 32-bit GPR number                                                                                                                                                                                                                                                                                            |

| BigEndianMem  | Endian mode as configured at chip reset (0 $\rightarrow$ Little-Endian, 1 $\rightarrow$ Big-Endian). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions), and the endianness of Kernel and Supervisor mode execution.                                                                                              |

| BigEndianCPU  | The endianness for load and store instructions ( $0 \rightarrow$ Little-Endian, $1 \rightarrow$ Big-Endian). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian).                                                                                    |

| ReverseEndian | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only, and is implemented by setting the <i>RE</i> bit of the <i>Status</i> register. Thus, ReverseEndian may be computed as ( $SR_{RE}$ and User mode).                                                                                                                   |

| LLbit         | Bit of <b>virtual</b> state used to specify operation for instructions that provide atomic read-modify-write. <i>LLbit</i> is set when a linked load occurs; it is tested and cleared by the conditional store. It is cleared, during other CPU operation, when a store to the location would no longer be atomic. In particular, it is cleared by exception return instructions. |

Table 1.1 Symbols Used in Instruction Operation Statements (Continued)

| Symbol                                         | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I:,<br>I+n:,<br>I-n:                           | This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the current instruction appear to occur during the instruction time of the current instruction. No label is equivalent to a time label of <b>I</b> . Sometimes effects of an instruction appear to occur either earlier or later — that is, during the instruction time of another instruction. When this happens, the instruction operation is written in sections labeled with the instruction time, relative to the current instruction <b>I</b> , in which the effect of that pseudocode appears to occur. For example, an instruction operation description that writes the result register in a section labeled <b>I+1</b> . The effect of pseudocode statements for the current instruction labelled <b>I+1</b> appears to occur "at the same time" as the effect of the statements take place in order. However, between sequences of statements for different instructions that occur "at the same time," there is no defined order. Programs must not depend on a particular order of evaluation between such sections. |

| PC                                             | The <i>Program Counter</i> value. During the instruction time of an instruction, this is the address of the instruction word. The address of the instruction that occurs during the next instruction time is determined by assigning a value to <i>PC</i> during an instruction time. If no value is assigned to <i>PC</i> during an instruction time by any pseudocode statement, it is automatically incremented by either 2 (in the case of a 16-bit MIPS16 instruction) or 4 before the next instruction time. A taken branch assigns the target address to the <i>PC</i> during the instruction time of the instruction in the branch delay slot.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PABITS                                         | The number of physical address bits implemented is represented by the symbol PABITS. As such, if 36 physical address bits were implemented, the size of the physical address space would be $2^{\text{PABITS}} = 2^{36}$ bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FP32RegistersMode                              | Indicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs). In MIPS32, the FPU has 32 32-bit FPRs in which 64-bit data types are stored in even-odd pairs of FPRs. In MIPS64, the FPU has 32 64-bit FPRs in which 64-bit data types are stored in any FPR.<br>In MIPS32 implementations, <b>FP32RegistersMode</b> is always a 0. MIPS64 implementations have a compatibility mode in which the processor references the FPRs as if it were a MIPS32 implementation. In such a case <b>FP32RegisterMode</b> is computed from the FR bit in the <i>Status</i> register. If this bit is a 0, the processor operates as if it had 32 32-bit FPRs. If this bit is a 1, the processor operates with 32 64-bit FPRs. The value of <b>FP32RegistersMode</b> is computed from the FR bit in the <i>Status</i> register.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| InstructionInBranchDe-<br>laySlot              | Indicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the <i>dynamic</i> state of the instruction, not the <i>static</i> state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SignalExcep-<br>tion(exception, argu-<br>ment) | Causes an exception to be signaled, using the exception parameter as the type of exception and the argument parameter as an exception-specific argument). Control does not return from this pseudocode function - the exception is signaled at the point of the call.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 1.1 Symbols Used in Instruction Operation Statements (Continued)

### **1.4 For More Information**

Various MIPS RISC processor manuals and additional information about MIPS products can be found at the MIPS URL: http://www.mips.com

For comments or questions on the MIPS32® Architecture or this document, send Email to support@mips.com.

## Overview of the MIPS® PDtrace<sup>™</sup> Architecture

This document contains the MIPS® PDtrace<sup>™</sup> specification, which defines the controls and formats for tracing program execution on a MIPS® processor core or on a System on a Chip (SoC) that includes multiple MIPS processor cores. The specification also defines tracing of additional SoC system elements, including system buses and other IP (Intellectual Property) customer-defined blocks.

This document serves three functions. It provides a specification of the trace interface for the core designer, it provides sufficient detail for an architecture licensee to build a trace control block that works with existing probes from third parties, and it provides sufficient details to design and code a post-processing software module for trace reconstruction.

#### 2.1 Introduction

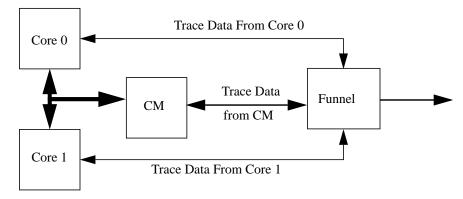

The PDtrace specification provides trace control and formats for both the processor-specific information captured from each pipeline within the processor and for the non-processor specific blocks, such as the CM (Coherence Manager) block in the CMP system, including the details of how the trace from multiple on-chip blocks are combined to provide a single trace stream on the chip interface pins. Note that processor-specific trace information and formats are included in the Appendices of this document, because these can be modified per implementation and do not necessarily constitute architecture.

The type of information that is captured in the trace stream and put into memory is controlled by CP0 control registers defined in the MIPS32® architecture and by TCB (Trace Control Block) control registers defined in the PDtrace architecture. CP0 control registers can be programmed by user applications so long as the needed hardware components and trace memory are present. The TCB control registers can be programmed by an external probe using the EJTAG TAP controller hardware or via software through the debug memory segment (this feature is only available in cores that implement PDtrace revision 6.00 and higher). The TCB registers allow users to control tracing at the execution time of applications, using an external agent like the debugger that communicates with these control registers using a debugger probe.

In most implementations, the trace information from the pipeline-tracing logic in the core is captured by a block called the Trace Control Block (TCB). This block contains registers used to control the trace information captured from the core, and is also used to format the trace information into the architecturally-specified trace formats, readying the information for writing into trace memory. The trace memory may be either on-chip or off-chip, based on user requirements. The trace information written to memory is compressed and assumes that post-processing software has access to the static program image to reconstruct the dynamic program flow. Compression reduces the number of signals (hence pins) required to gather this information and also reduces the trace size.

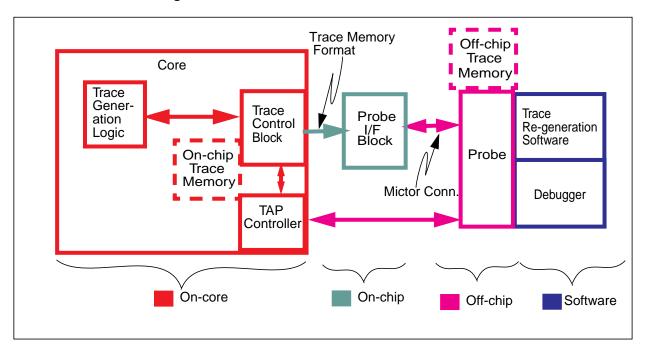

Figure 2.1 illustrates one possible configuration for trace capture and post-analysis using software. The figure shows a core with trace generation logic and a TAP controller. This core is connected to a trace control block (TCB) via the TAP controller (the TCB implements and uses TAP registers). The trace memory associated with the trace control block can be located on-chip or off-chip. An on-chip trace buffer will be smaller and will be writable by the TCB at higher speeds, while an off-chip trace memory can be much larger and is written via the potentially slower pin interface out of the core. Probe hardware and software connects to the TCB and the TAP controller via the chip's pin interface and allows debugger software to start, stop, and examine program execution traces.

Figure 2.1 Illustration of a PC and Data Trace Flow

Implementation of PDtrace is optional for a given MIPS-compatible processor. Whether a core or processor implements PDtrace is indicated by a bit in the Coprocessor 0 *Config3* register as shown in Figure 2.2 and Table 2.1.

Note that if a core or processor does not implement EJTAG, PDtrace tracing logic can still be implemented.

#### Figure 2.2 Config3 Register Format

| 31 | 1 | 0  |

|----|---|----|

|    |   | TL |

Table 2.1 Config3 Register Field Descriptions

| Fie  | lds  |                                                                                                                                                      | Read / | Reset  |            |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|

| Name | Bits | Description                                                                                                                                          | Write  | State  | Compliance |

|      | 31:1 | As per the MIPS32 and MIPS64 Architecture specifica-<br>tions                                                                                        |        |        |            |

| TL   | 0    | This bit is used to indicate the presence of tracing logic<br>in the processor.<br>0 : No tracing logic implemented<br>1 : Tracing logic implemented | R      | Preset | Required   |

#### 2.2 Processor Modes

The PDtrace specification allows tracing to be enabled or disabled based on various processor modes. This section precisely describes these modes, and the terminology is then used later in the document.

$\texttt{DebugMode} \leftarrow (\texttt{Debug}_{\texttt{DM}} = 1)$

#### 2.3 Subsetting

The PDtrace specification allows four levels of subsetting. Within each level, all features required to support the level must be implemented. The allowable subsets are:

- 1. No PDtrace implemented

- 2. PDtrace with PC tracing only

- 3. PDtrace with PC and load and store address tracing only

- 4. PDtrace with PC, load and store address, and load and store data tracing

The specific subset implemented by a processor or core can be determined by reading the *TL* bit (0) of the *Config3* register (see Table 2.1) and the *ImpSubset* bits (6:5) in the *TraceControl2* register (see Table 7.3 on page 61).

In addition, Trace Trigger from EJTAG Hardware breakpoints (Section 3.16 "Trace Trigger from EJTAG Hardware Instruction/Data Breakpoints") is optional. This feature depends on the EJTAG optional feature for hardware instruction and data breakpoints. The exact nature of this subsetting is described in later chapters.

#### 2.4 Overview of the Trace Control Block

The tracing logic within the processor core (shown in Figure 2.1) outputs all trace information to the on-core trace control block (TCB) unit. The TCB is responsible for collecting the trace data and storing this trace data in an on-chip trace memory or to an off-chip trace memory using the Probe Interface Block (PIB). The TCB's control registers accept user requests for program tracing and determine what is traced and what is output.

The description of the TCB in this document includes:

- Details on the TCB's internal architecture, i.e., registers, and how these registers are used to control tracing

- Trace formats used by the TCB to write trace information to memory

- Interface between the TCB and the TAP controller

This document does not include:

- TCtrace Interface that connects the TCB to the Probe Interface Block, which is off-core but on-chip

- The PIB

- External Probe interface including its electrical characteristics

This information is available in core-specific documents.

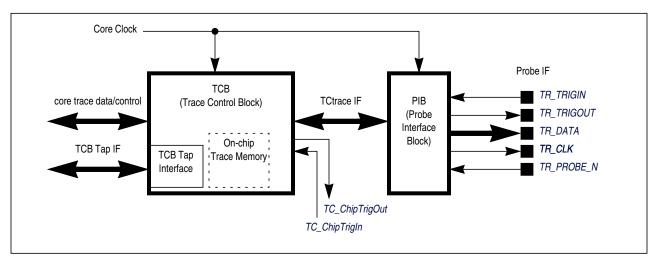

Figure 2.3 shows the TCB, the PIB, and the trace data path from the TCB to the Probe IF. It is optional whether the TCB implements on-chip trace memory and/or the TCtrace IF with a PIB and off-chip trace memory.

Figure 2.3 TCB and Optional PIB Overview

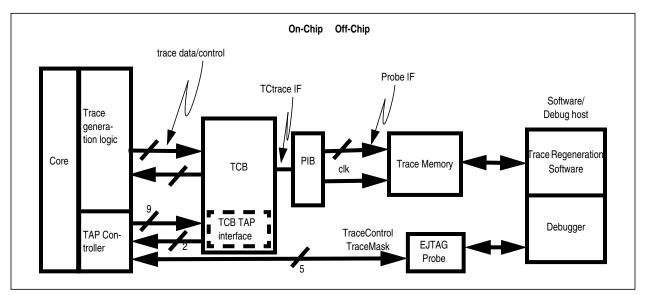

Figure 2.4 Illustration of the Core and TCB with External Trace Memory

Figure 2.4 shows the full system configuration when the TCB is streaming data to off-chip trace memory through the PIB. The number of pins needed for trace data on the Probe IF is configurable to 4, 8, or 16. Note that the TCtraceIF is at the core interface boundary. The PIB is outside the core. Although cores from MIPS Technologies may include a sample PIB implementation, its design can be modified to suit the SOC vendor and the probe vendor. For example, whether or not a DDR memory interface is used on the ProbeIF is a decision made by the SOC vendor.

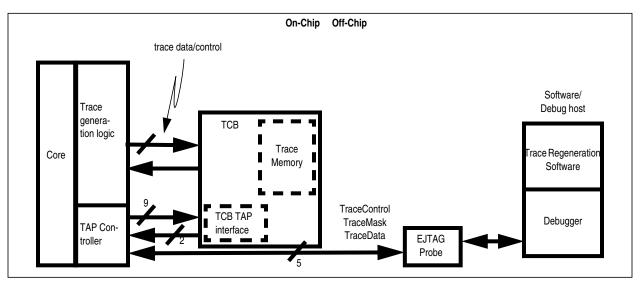

Figure 2.5 shows the configuration in which the TCB is streaming data to an on-chip trace memory. The size of the on-chip trace memory is configurable. After trace capture has stopped, the trace data in the on-chip memory is accessed through the EJTAG probe by the Trace Regeneration Software.

Figure 2.5 Illustration of the Core and TCB with Internal Trace Memory

The TCB includes two primary interfaces:

- The TCB TAP interface, which connects the EJTAG TAP controller resident within the processor core to the TAP functionality present within the TCB.

- An optional TCtrace interface to the PIB. This interface is described along with the Probe IF in the core-specific document. If the TCB is configured with only on-chip trace memory, the TCtrace IF and the PIB are not needed.

## **PDtrace™ Description**

A program executes sequentially through instructions within a basic block, then jumps (or branches) to the head (first instruction) of the next basic block. To reconstruct the dynamic execution path of the program, it is sufficient to provide the post-analyzer with the PC address of the head of each basic block. Even this is not always necessary, because it may be possible in some instances to statically predict the value of the branch target, provided there is a separate indication for the taken branch. Thus, PC addresses need be traced only when it is not possible to statically predict the PC of the branch target. For the MIPS32 and MIPS64 instruction sets, the statically unpredictable instructions are JR and JALR (for branch target address), and BEQ, BNE, BGEZ, etc. (for branch on condition). Other statically unpredictable PC changes occur with taken exceptions and return from exceptions (ERET and DERET). To enable the post-analyzer to re-synchronize itself with program execution, the PC value is also output at predictable intervals and synchronization periods.

The next sections of this chapter describe the various bits used in the output trace formats generated by the TCB. This information indicates how tracing information is output and therefore is needed by the trace reconstruction software to rebuild the program execution.

## 3.1 Instruction Completion Indicator (InsComp)

Three bits are used as an indicator of completed instructions and their type in the processor's pipeline. Once tracing is initiated, a valid InsComp value is required in every cycle<sup>1</sup>, except when the TCB has requested that the trace be stalled.

| Value | Mnemonic | Description                                                                                                                                                                                                                                              |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000   | NI       | No instruction completed this cycle. A "No Instruction"<br>can happen due to a pipeline stall or when the instruction<br>was killed (due to an exception).                                                                                               |

| 001   | I        | Instruction completed this cycle                                                                                                                                                                                                                         |

| 010   | IL       | Instruction completed this cycle was a load                                                                                                                                                                                                              |

| 011   | IS       | Instruction completed this cycle was a store                                                                                                                                                                                                             |

| 100   | IPC      | Instruction completed this cycle was a PC sync. The IPC value is used for the periodic output of the full PC value for synchronization. The tracing hardware should ensure that this is not done on an unpredictable branch, load, or store instruction. |

<sup>&</sup>lt;sup>1</sup> Implementations are allowed to disable PC tracing. If PC tracing is disabled, it is allowed that InsComp values are not generated for instruction completion.

| Value | Mnemonic | Description                                                                                                                                                                                                                                                                      |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101   | IB       | Instruction branched this cycle. The three encodings (101, 110, 111) for branched instructions indicate a discontinuity in the PC value for the associated instruction. Note that it is only when the new PC cannot be predicted from the static program flow that it is traced. |

| 110   | ILB      | Instruction branched this cycle was a load                                                                                                                                                                                                                                       |

| 111   | ISB      | Instruction branched this cycle was a store                                                                                                                                                                                                                                      |

Table 3.1 Instruction Type Completion Indicator (InsComp) (Continued)

NI (No Instruction complete) is used when the internal pipe is stalled for some reason, and no instruction completes in that cycle. It is also used when tracing has been turned off, but the internal FIFO is still emptying trace data out to the TCB that is data-related and not instruction-related, for example, data address or data values.

Instructions within a basic block are indicated with an I, IL, or IS value. The I is used to indicate a simple instruction that is neither a load nor a store. The IL is used to indicate a load instruction and the IS is used to indicate a store instruction.

Unpredictable (and predictable) changes in the PC value are indicated as a branch-type instruction, i.e., IB, ILB, or ISB. Note that the first instruction in the basic block is always indicated as a branch instruction. When this first instruction is a load or a store, then InsComp[2:0] takes values ILB or ISB respectively, to indicate the combined condition of the branch and load or store.

**Implementation Notes:** Figure 3.1 shows an example of when the InsComp value might be output by the processor tracing logic, with respect to the processor pipeline implementation. This example pipeline has six stages. They are: "fetch", "decode", "execute", "memory", "align", and "write back". In this example, the InsComp value is finalized after the memory stage. That is, the instruction goes through the pipeline and is captured after the last stage when the instruction **must** complete and can no longer be killed. In the example shown, this is after stage 4. This will differ, of course, with each pipeline implementation.

Some instructions might have to provide more information for a complete picture of program execution. For instance, a branch indicator might have to transmit the PC value if the unpredictability lies in the branch target address. If the unpredictability was in the branch condition (i.e., determining if the branch is taken or not), then the branch target PC value need not be transmitted; it suffices to indicate that it was a "taken" branch using the appropriate InsComp value.

The list below summarizes the three possible branching options, and the corresponding InsComp and PC tracing action:

• When the branch is unconditional and the branch target is predictable, IB, ILB, or ISB is used for the InsComp value, and the PC is not traced out.

- When the branch is conditional, and the branch target is predictable, IB, ILB, or ISB is used only when the branch is taken. The PC is not traced out.

- When the branch is conditional or unconditional, and the branch target is unpredictable, IB, ILB, or ISB is used and the PC is traced (using TPC for TType, to be discussed in section 3.2 "Trace Type and an Example Code Fragment").

There are four possible circumstances that cause the value of the PC to be traced:

- 1. After a JR or JALR instruction

- 2. After a control transfer to an exception handler

- 3. After a return from exception (ERET or DERET instruction)

- 4. The PC is traced out periodically for software synchronization of trace with the static program image

When the InsComp value indicates a store in the completing instruction with an IS, then the store address and data might have to be transmitted if the user requires them to be traced. With an ISB, the PC value might also need to be traced out. In this situation, the PC value is sent first, followed by the store address, and finally the store data if it is immediately available.

An ILB is similar, and might require the tracing of the PC value as well as the load address and the load data. The PC value is sent first. If the load hits in the cache, then the PC value is sent first, followed by the load address, and finally the load data if it is immediately available.