# **EJTAG Trace Control Block Specification**

Document Number: MD00148 Revision 1.04 March 21, 2002

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 2001-2002 MIPS Technologies Inc. All right reserved.

Copyright © 2001-2002 MIPS Technologies, Inc. All rights reserved.

Unpublished rights reserved under the Copyright Laws of the United States of America.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying, or use of this information (in whole or in part) which is not expressly permitted in writing by MIPS Technologies or a contractually-authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

MIPS Technologies or any contractually-authorized third party reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error of omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Any license under patent rights or any other intellectual property rights owned by MIPS Technologies or third parties shall be conveyed by MIPS Technologies or any contractually-authorized third party in a separate license agreement between the parties.

The information contained in this document shall not be exported or transferred for the purpose of reexporting in violation of any U.S. or non-U.S. regulation, treaty, Executive Order, law, statute, amendment or supplement thereto.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or any contractually-authorized third party.

MIPS<sup>®</sup>, R3000<sup>®</sup>, R4000<sup>®</sup>, R5000<sup>®</sup> and R10000<sup>®</sup> are among the registered trademarks of MIPS Technologies, Inc. in the United States and certain other countries, and MIPS16<sup>TM</sup>, MIPS16e<sup>TM</sup>, MIPS32<sup>TM</sup>, MIPS64<sup>TM</sup>, MIPS-3D<sup>TM</sup>, MIPS-based<sup>TM</sup>, MIPS II<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS IV<sup>TM</sup>, MIPS V<sup>TM</sup>, MDMX<sup>TM</sup>, SmartMIPS<sup>TM</sup>, 4K<sup>TM</sup>, 4Kc<sup>TM</sup>, 4Km<sup>TM</sup>, 4KE<sup>TM</sup>, 4KE<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KSc<sup>TM</sup>, 5K<sup>TM</sup>, 5Kc<sup>TM</sup>, 5Kf<sup>TM</sup>, 20K<sup>TM</sup>, 20Kc<sup>TM</sup>, R20K<sup>TM</sup>, R4300<sup>TM</sup>, ATLAS<sup>TM</sup>, CoreLV<sup>TM</sup>, EC<sup>TM</sup>, JALGO<sup>TM</sup>, MALTA<sup>TM</sup>, MGB<sup>TM</sup>, SEAD<sup>TM</sup>, SEAD-2<sup>TM</sup>, SOC-it<sup>TM</sup> and YAMON<sup>TM</sup> are among the trademarks of MIPS Technologies, Inc.

All other trademarks referred to herein are the property of their respective owners.

## Table of Contents

| Chapter 1 EJTAG Trace Control Block Specification                                           | 1  |

|---------------------------------------------------------------------------------------------|----|

| 1.1 Overview: The On-Chip Trace Control Block                                               |    |

| Chapter 2 Trace Message Format                                                              | 3  |

| 2.1 Single-Pipe Tracing Formats                                                             |    |

| 2.1.1 Trace Format 1 (TF1)                                                                  |    |

| 2.1.2 Trace Format 2 (TF2)                                                                  |    |

| 2.1.2 Trace Format 2 (112)                                                                  |    |

| 2.1.5 Trace Format 5 (115)                                                                  |    |

| 2.1.4 Trace Format 4 (114)                                                                  |    |

| 2.1.5 Trace Format 5 (TF5)                                                                  |    |

| 2.2 Multi-Pipe Tracing Formats                                                              |    |

| 2.2.1 Multi-Pipe Trace Format 2-4 (TF2, TF3, TF4)                                           |    |

| Chapter 3 Trace Word Format                                                                 |    |

| 3.1 Trace Word                                                                              |    |

| 3.1.1 Cycle Inaccurate Trace                                                                |    |

| 3.2 End of Trace indication.                                                                |    |

|                                                                                             |    |

| <ul><li>3.3 On-chip Trace Memory Format</li><li>3.4 Probe Trace Word transmission</li></ul> |    |

| 5.4 Probe Trace word transmission                                                           | 15 |

| Chapter 4 Trace Control Block Registers                                                     | 15 |

| 4.1 TCBCONTROLA Register                                                                    |    |

| 4.2 TCBCONTROLB Register                                                                    |    |

| 4.3 TCBDATA Register                                                                        |    |

| 4.4 TCBCONFIG Register (Reg 0)                                                              |    |

| 4.5 TCBTW Register (Reg 4)                                                                  |    |

| 4.6 TCBRDP Register (Reg 5)                                                                 |    |

| 4.7 TCBWRP Register (Reg 6)                                                                 |    |

| 4.8 TCBSTP Register (Reg 7)                                                                 |    |

| 4.9 TCBTRIGx Register (Reg 16-23)                                                           |    |

| 4.10 Reset State                                                                            |    |

| Chapter 5 Trigger Logic                                                                     |    |

| 5.1 Trigger Logic Overview                                                                  |    |

| 5.1.1 Trigger Source Logic                                                                  |    |

| 5.1.2 Trigger Control Logic                                                                 |    |

| 5.1.3 Trigger Action logic                                                                  |    |

| 5.2 Simultaneous Triggers                                                                   |    |

| 5.2.1 Prioritized Trigger Actions                                                           |    |

| 5.2.2 OR'ed Trigger Actions                                                                 |    |

| 5.3 TCB Trigger Input/Output Signals                                                        |    |

| Chapter 6 PDtrace <sup>TM</sup> Interface                                                   |    |

| Chapter 7 Trace Control Block TAP Interface                                                 |    |

| 7.1 Signal list                                                                             |    |

| 7.2 Interface description                                                                   |    |

| Chapter 8 TCtrace IF                                                                        |    |

| 8.1 Signal description                                                                      |    |

| 8.2 <i>TC_Valid</i> and <i>TC_Stall</i> timing                                              |    |

| Chapter 9 Probe IF                                | 47 |

|---------------------------------------------------|----|

| 9.1 Interface definition                          | 47 |

| 9.2 Probe Interface Block                         | 47 |

| 9.2.1 Simple Probe Interface Block                | 48 |

| 9.2.2 Probe Interface Block with Clock-Multiplier | 48 |

| 9.2.3 Probe Interface Block with Clock-Divider    | 50 |

| 9.3 DC Specifications                             | 51 |

| 9.4 AC Specifications                             | 51 |

| 9.4.1 Required target AC timing specs             |    |

| 9.4.2 Required Probe AC timing specs              |    |

| 9.4.3 Probe - Target Calibration                  |    |

| 9.5 Connector                                     | 52 |

| 9.6 Logic analyzer probing                        | 53 |

| Chapter 10 On-Chip Trace Memory                   | 55 |

| 10.1 On-Chip Trace Memory size                    |    |

| 10.2 Trace-From Mode                              |    |

| 10.3 Trace-To Mode                                |    |

| Appendix A References                             | 57 |

| Appendix B Revision History                       | 59 |

# List of Figures

| Figure 1-1: TCB and optional PIB overview                                | 1  |

|--------------------------------------------------------------------------|----|

| Figure 1-2: Illustration of the core and TCB with external trace memory  | 2  |

| Figure 1-3: Illustration of the core and TCB with internal trace memory  | 2  |

| Figure 2-1: TF1 (Trace Format 1)                                         | 3  |

| Figure 2-2: TF2 (Trace Format 2 Single-Pipe)                             | 4  |

| Figure 2-3: TF3 (Trace Format 3 Single-Pipe)                             | 4  |

| Figure 2-4: TF4 (Trace Format 4 Single-Pipe)                             | 4  |

| Figure 2-5: TF5 (Trace Format 5)                                         | 5  |

| Figure 2-6: TF6 (Trace Format 6)                                         | 5  |

| Figure 2-7: TF2 (Trace Format 2 Multi-Pipe)                              | 6  |

| Figure 2-8: TF3 (Trace Format 3 Multi-Pipe)                              | 6  |

| Figure 2-9: TF4 (Trace Format 4 Multi-Pipe)                              | 7  |

| Figure 3-1: TW (Trace Word)                                              |    |

| Figure 3-2: Trace Word from Example Trace in Table 3-2                   | 11 |

| Figure 3-3: Trace Word from Example Trace in Table 3-2 (No TF1 trace)    | 11 |

| Figure 3-4: Cycle by cycle Trace Word from Example Trace in Table 3-2    | 12 |

| Figure 3-5: Cycle by cycle TR_DATA (8-bit) of Example Trace in Table 3-2 | 13 |

| Figure 5-1: TCB Trigger processing overview                              |    |

| Figure 7-1: TCB TAP register access timing diagram                       | 40 |

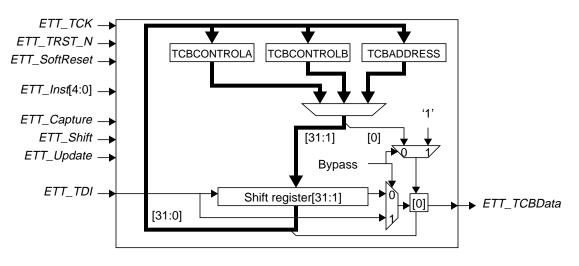

| Figure 7-2: TCB TAP data-path                                            | 41 |

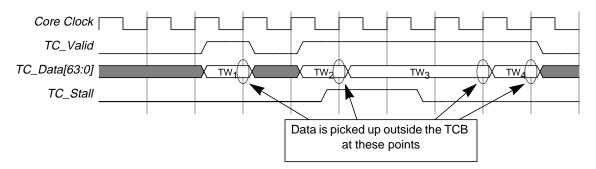

| Figure 8-1: TC_Valid and TC_Stall timing                                 | 45 |

| Figure 9-1: Simple Probe Interface Block                                 |    |

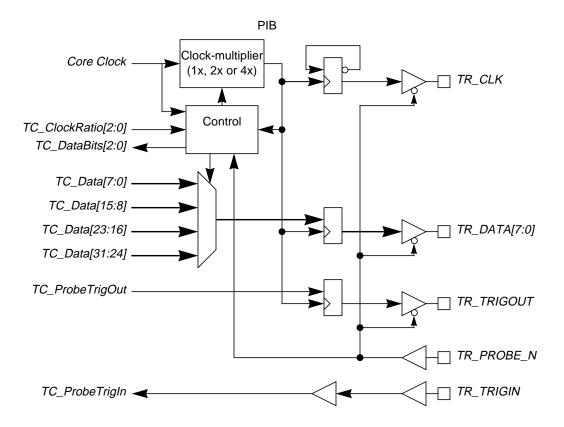

| Figure 9-2: Probe Interface Block with Clock-multiplier                  | 49 |

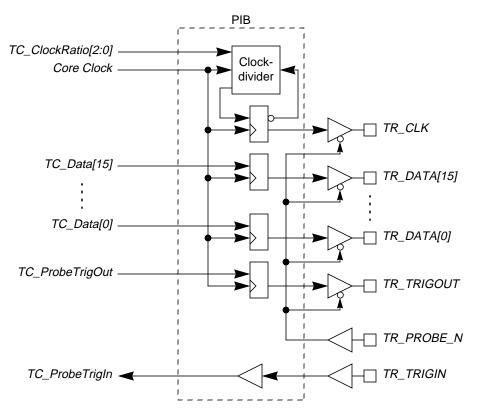

| Figure 9-3: Probe Interface Block with Clock-divider                     | 50 |

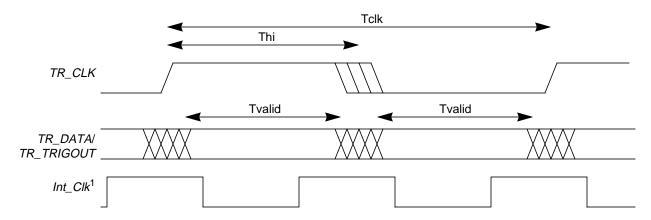

| Figure 9-4: Probe interface signal timing diagram                        | 51 |

## List of Tables

| Table 2-1: TCBcode and TCBinfo fields of Trace Format 6 (TF6)                                | 5  |

|----------------------------------------------------------------------------------------------|----|

| Table 3-1: Trace Word Type field description                                                 |    |

| Table 3-2: Example Trace sequence                                                            |    |

| Table 4-1: Registers in the Trace Control Block                                              |    |

| Table 4-2: Registers selected by <i>TCBCONTROLB</i> <sub>REG</sub> (acessed through TCBDATA) | 15 |

| Table 4-3: TCBCONTROLA Register Field Descriptions                                           | 16 |

| Table 4-4: TCBCONTROLB Register Field Descriptions                                           | 19 |

| Table 4-5: Clock Ratio encoding of the CR field                                              | 23 |

| Table 4-6: TCBDATA Register Field Descriptions                                               | 24 |

| Table 4-7: TCBCONFIG Register Field Descriptions                                             | 24 |

| Table 4-8: TCBTW Register Field Descriptions                                                 |    |

| Table 4-9: TCBRDP Register Field Descriptions                                                |    |

| Table 4-10: TCBWRP Register Field Descriptions                                               | 27 |

| Table 4-11: TCBSTP Register Field Descriptions                                               | 27 |

| Table 4-12: TCBTRIGx Register Field Descriptions                                             |    |

| Table 5-1: TCB Trigger input and output                                                      |    |

| Table 6-1: PDtrace <sup>™</sup> IF core input controls from TCB                              |    |

| Table 7-1: Trace Control Block TAP Interface signals                                         |    |

| Table 8-1: TCB TCtrace IF signals                                                            | 43 |

| Table 9-1: External Probe Interface signals                                                  | 47 |

| Table 9-2: TCB Static Inputs for Simple PIB                                                  |    |

| Table 9-3: TCB Static Inputs for Clock-multiplier PIB                                        | 49 |

| Table 9-4: TCB Static Inputs for Simple PIB                                                  | 50 |

| Table 9-5: Mictor Connector Pin Out                                                          |    |

| Table B-1: Revision History                                                                  | 59 |

## EJTAG Trace Control Block Specification

## 1.1 Overview: The On-Chip Trace Control Block

The tracing logic within the processor core (not shown in Figure 1-1) outputs all trace information on the PDtrace<sup>TM</sup> interface (shown in Figure 1-1). This PDtrace<sup>TM</sup> interface connects to the on-chip trace control block (TCB) unit. The TCB is responsible for collecting the trace data sent every cycle on the PDtrace<sup>TM</sup> interface by the core's tracing logic. The TCB captures and stores this trace data in an on-chip trace memory or an off-chip trace memory using the Probe Interface Block (PIB). A separate document, the *PDtrace<sup>TM</sup> Interface Specification* Ref [2], describes the tracing control and mechanism on the processor core, and the PDtrace<sup>TM</sup> interface signals in detail. This document describes all trace-related blocks and interfaces that are external to the processor core and the PDtrace<sup>TM</sup> interface. This includes:

- the TCB, with details on the internal architecture, i.e., registers, and how these registers are used to control tracing,

- the formats used by the TCB to write the trace information to memory,

- the interface between the TCB and the TAP controller,

- the TCtrace IF,

- the PIB, and

- the external Probe interface including its electrical characteristics.

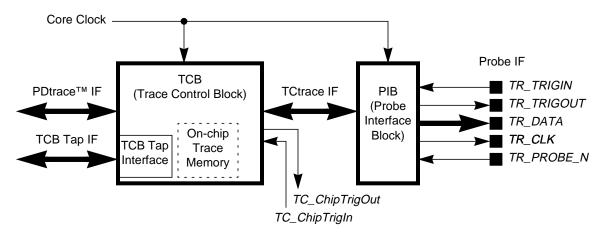

Figure 1-1 shows the TCB, the PIB, and the trace data path from the PDtrace<sup>TM</sup> IF to the Probe IF. It is optional whether the TCB implements on-chip trace memory and/or the TCtrace IF with a PIB and off-chip trace memory.

Figure 1-1 TCB and optional PIB overview

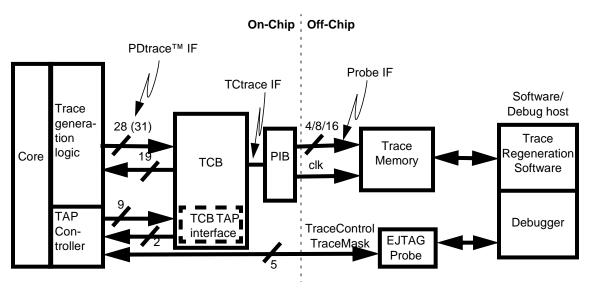

Figure 1-2 shows the full system configuration when the TCB is streaming data to off-chip trace memory through the PIB. The number of pins needed for trace data on the Probe IF is configurable to 4, 8, or 16.

Figure 1-2 Illustration of the core and TCB with external trace memory

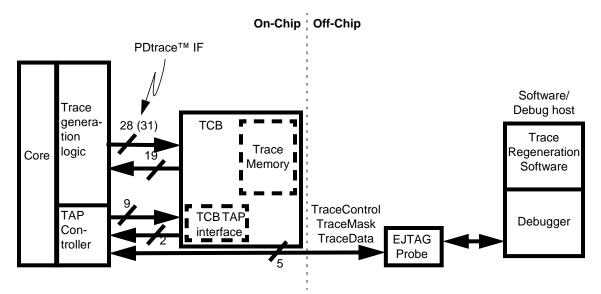

Figure 1-3 shows the configuration where the TCB is streaming data to an on-chip trace memory. The size of the on-chip trace memory is configurable. After trace capture has stoppe, the trace data in the on-chip memory is accessed through the EJTAG probe by the Trace Regeneration Software.

Figure 1-3 Illustration of the core and TCB with internal trace memory

The TCB includes these primary interfaces:

- The PDtrace<sup>TM</sup> interface to the processor core. A detailed description about the PDtrace<sup>TM</sup> signal interface is described in the *PDtrace<sup>TM</sup> Interface Specification* Ref [2].

- The TCB TAP interface, which connects the EJTAG TAP controller resident within the processor core to the TAP functionality present within the TCB. This interface is described in Chapter 7, "Trace Control Block TAP Interface," on page 39.

- An optional TCtrace interface to the PIB. This interface is described along with the Probe IF in Chapter 8, "TCtrace IF," on page 43 and Chapter 9, "Probe IF," on page 47. If the TCB is configured with only on-chip trace memory, then the TCtrace IF and the PIB are not needed.

## Trace Message Format

One main function of the TCB is to capture trace information from the PDtrace<sup>™</sup> interface and store it to trace memory. This trace information is then analyzed by the trace reconstruction software in the debugger. Since tracing the entire run of a program can require a lot of storage, compression of trace information is a desirable goal. While the trace information undergoes one level of compression in the core, further compression is possible before the trace information is stored to trace memory by the TCB. The TCB achieves this compression using a number of trace formats which eliminate the storage of unnecessary trace bits in each cycle. This section describes these formats.

Note that the description of the trace formats refers to PDtrace<sup>TM</sup> interface signals. Hence, to fully understand the intent of some of these trace formats, the reader must have a basic understanding of these signals or have access to the PDtrace<sup>TM</sup> specification document.

## 2.1 Single-Pipe Tracing Formats

The formats discussed in this section are relevant only when the core or processor being traced is a single-issue, i.e., single pipeline implementation. The multi-pipeline case is discussed in Section 2.2, "Multi-Pipe Tracing Formats".

Recall that when the signal *PDO\_IamTracing* is asserted by the processor, there is valid trace data on the other PDtrace<sup>TM</sup> interface signals, and these values must be captured and stored by the TCB. When *PDO\_IamTracing* is de-asserted, no useful trace information is on the other PDtrace<sup>TM</sup> interface signals, and no trace records need to be stored to trace memory. Hence, whenever the processor has de-asserted the *PDO\_IamTracing* signal, the TCB ignores the PDtrace<sup>TM</sup> interface signal values, and does not store anything to trace memory. In all the cases discussed below, the *PDO\_IamTracing* signal is being asserted by the processor tracing logic.

## 2.1.1 Trace Format 1 (TF1)

A processor stall is identified when  $PDO\_InsComp[2:0]$  is 000,  $PDO\_TType[2:0]$  is 000, and  $PDO\_Overflow$  is not asserted. When the processor is stalled, no execution trace information needs to be recorded except that this was a stall cycle. This can be done efficiently using a single bit "1" for this format. This is Trace Format 1 (TF1) as show in Figure 2-1. Note that this stall information is needed only when tracing is used to account for all execution cycles, i.e., cycle-accurate tracing (*TCBCONTROLB*<sub>CA</sub> = 1, see Section 4.2, "TCBCONTROLB Register").

Note that when parsing a trace format sequence, if the first bit of the trace format is a one, then this is TF1 and the next bit is the first bit of the next trace format.

Figure 2-1 TF1 (Trace Format 1)

EJTAG Trace Control Block Specification, Revision 1.04

**0** 1

## 2.1.2 Trace Format 2 (TF2)

A study of program traces shows that with only PC tracing enabled, nothing of significance needs to be captured a large percentage of the time. For instance, when PDO\_TType[2:0] is NT (000), i.e., No Transmission, the address/data bits (PDO\_AD) is don't-cares and therefore do not need to be saved. So, when PDO\_TType[2:0] is NT and PDO\_Overflow is 0, the only significant trace signal is PDO\_InsComp[2:0], which describes the completed instruction. Having used a single bit value of "1" for TF1, we indicate the combination of non-zero PDO\_InsComp[2:0], zero PDO\_TType[2:0], and zero PDO\_Overflow in two bits (10<sub>2</sub>). The next three bits of the format are the value of PDO\_InsComp[2:0]. This trace format with five bits is called Trace Format 2 (TF2), as shown in Figure 2-2.

## Figure 2-2 TF2 (Trace Format 2 Single-Pipe)

## 2.1.3 Trace Format 3 (TF3)

When *PDO\_TType[2:0]* is not **NT** (000) and *PDO\_Overflow* is set to 0, all trace information needs to be captured. This is the TF3 format shown in Figure 2-3. The *PDO\_LoadOrder[2:0]* signal is an exception in that it only needs to be captured on the last cycle of a **D**ata Transmission transaction (**DT** on the *PDO\_TType[2:0]* signal). Hence, a slight distinction is made between this format TF3 (which excludes the *PDO\_LoadOrder[2:0]* value, see Figure 2-3), and the format TF4 (which includes the *PDO\_LoadOrder[2:0]* value, see Figure 2-4).

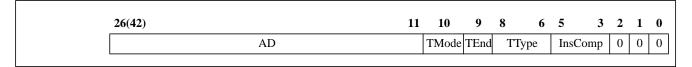

TF3 is distinguished from TF2 by having  $000_2$  on the first three bits. TF3 may be either 27 or 43 bits wide, depending on whether 16 or 32 bits of the *PDO\_AD* bus are included in the AD field. The AD field width is determined by the *TCBCONTROLA*<sub>ADW</sub> field. (See Section 4.1, "TCBCONTROLA Register").

#### Figure 2-3 TF3 (Trace Format 3 Single-Pipe)

## 2.1.4 Trace Format 4 (TF4)

The TF4 format is shown in Figure 2-4. TF4 covers the case when  $PDO_TType[2:0]$  is set to **DT** and  $PDO_TEnd$  is set to 1, that is, the last cycle of the current data transmission. This is shown in Figure 2-4, where the pattern on bits [9:6] distinguishes TF4 from TF3. Bits [8:6] are equal to  $001_2$  for a  $PDO_TType[2:0]$  value of **DT** and bit 9 has a value of 1 for  $PDO_TEnd$ .

When capturing the cycle by cycle values on the PDtrace<sup>TM</sup> IF, the last cycle of a Load Data transmission cannot be distinguished from the last cycle of a Store Data transmission (without saving information from a previous cycle, i.e., the *PDO\_InsComp* value from the first cycle of the data transaction). This means that the TF4 format will be used for the last cycle of both Load and Store Data transmission, a small inefficiency.

| 29(45) | 14 | 13 11     | 10    | 9 | 8 | 7 | 6 | 5 3     | 2 | 1 | 0 |

|--------|----|-----------|-------|---|---|---|---|---------|---|---|---|

| AD     |    | LoadOrder | TMode | 1 | 1 | 0 | 0 | InsComp | 0 | 0 | 0 |

#### Figure 2-4 TF4 (Trace Format 4 Single-Pipe)

## 2.1.5 Trace Format 5 (TF5)

When *PDO\_Overflow* is asserted, all other PDtrace<sup>TM</sup> IF trace values are undefined and hence all current cycle trace values can be discarded. (When an overflow does occur, the PDtrace<sup>TM</sup> IF always sends a full PC value in the next cycle. This is used for resynchronizing to the execution path.) The Trace Format 5 (TF5) shown in Figure 2-5 indicates this overflow.

#### Figure 2-5 TF5 (Trace Format 5)

## 2.1.6 Trace Format 6 (TF6)

Trace Format 6 (TF6) shown in Figure 2-6 is provided to the TCB to transmit information that does not directly originate from the cycle by cycle trace data on the PDtrace<sup>TM</sup> interface. That is TF6 can be used by the TCB to store any information it wants in the trace memory, within the contraints of the specified format. This information can then be used by software for any purpose. For example, TF6 can be used to indicate a special condition, trigger, semaphore, breakpoint, or break in tracing that is encountered by the TCB.

| TCBinfo TCBcode 0 1 0 0 | 15 8 7 4 3 2        | 15 |

|-------------------------|---------------------|----|

|                         | TCBinfo TCBcode 0 1 |    |

#### Figure 2-6 TF6 (Trace Format 6)

The definition of TCBcode and TCBinfo is shown in Table 2-1.

#### Table 2-1 TCBcode and TCBinfo fields of Trace Format 6 (TF6)

| TCBcode           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TCBinfo                                                                                                           |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| 0000              | Trigger Start: Identifies start-point of trace. TCBinfo identifies what caused the trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                   |  |  |

| 0100              | Trigger End: Identifies end-point of trace. TCBinfo identifies what caused the trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Cause of trigger.<br>Taken from the<br>Trigger control                                                            |  |  |

| 1000              | Trigger Center: Identifies center-point of trace. TCBinfo identifies what caused the trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | register generating<br>this trigger.                                                                              |  |  |

| 1100              | 1100 <b>Trigger Info:</b> Information-point in trace. TCBinfo identifies what caused the trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                   |  |  |

| 0001 <sup>a</sup> | No trace cycles: Number of cycles where the processor is not sending trace data ( <i>PDO_IamTracing</i> is deasserted), but a stall is not requested by the TCB ( <i>PDI_StallSending</i> is not asserted). This can happen when the processor, during its execution, switches modes internally that take it from a trace output required region to one where trace output was not requested. For example, if it was required to trace in User-mode but not in Kernel-mode, then when the processor jumps to Kernel-mode from User-mode, the internal PDtrace <sup>™</sup> FIFO is emptied, then the processor deasserts <i>PDO_IamTracing</i> and stops sending trace informaton. In order to maintain an accurate account of total execution cycles, the number of such no-trace cycles have to be tracked and counted. This TCBcode achieves this goal. | Number of cycles (All<br>zeros is equal to 256).<br>If more than 256 is<br>needed, the TF6<br>format is repeated. |  |  |

| 0101 <sup>a</sup> | <b>Back stall cycles:</b> Number of cycles when <i>PDI_StallSending</i> was asserted, preventing the PDtrace <sup>TM</sup> interface from transmitting any trace information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                   |  |  |

| 1x01              | Reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Undefined                                                                                                         |  |  |

| xx10              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Undefined                                                                                                         |  |  |

| TCBcode          | Description                  | TCBinfo                  |

|------------------|------------------------------|--------------------------|

| xx11             | TCB implementation dependent | Implementation dependent |

| [a]: TF6 formats |                              |                          |

#### Table 2-1 TCBcode and TCBinfo fields of Trace Format 6 (TF6) (Continued)

## 2.2 Multi-Pipe Tracing Formats

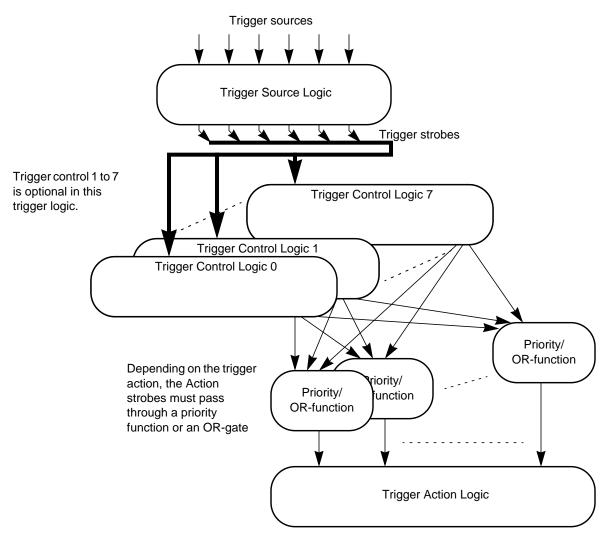

A processor with multiple pipelines requires additional support for sending trace information to trace memory. The TCB can perform some combining and the kind of format crunching as shown in the single-pipe case to reduce the number of bits that are sent out each cycle. If there are k pipelines within the core, 1, 2,... k, then for each cycle, the TCB generates a trace format from each pipeline, in that respective order. The external software programmer must refer to the User's Guide for that core to determine the order of the pipelines as hooked up to the PDtrace<sup>TM</sup> interface.

The trace format TF1 is usable by the TCB without change for multi-pipe tracing. The TF1 format indicates that the specific pipe did not complete an instruction and had no data to send.

TF5 is a common format. That is, all the pipes have to flush the trace buffer when just one of them has overflowed. Hence, a single instance of TF5 will suffice to cover all the 1..k pipeline stages. The trace reconstruction software must take this into account as it parses the trace formats in trace memory.

The TF6 format is also usable by the TCB without change, and as a common format. For example, the *PDO\_IamTracing* and *PDO\_StallSending* are common for all pipelines in a multi-pipeline processor. A TF6 format can be used after all the formats for the respective pipelines have been sent. Note that if needed, pipeline-specific information can be encoded within the TF6 format bits.

## 2.2.1 Multi-Pipe Trace Format 2-4 (TF2, TF3, TF4)

The TF2, TF3, and TF4 formats need the additional *PDO\_PgmOrder[2:0]* value for multi-pipeline tracing. The **PgmOrder** field is added to all of them, right after the **InsComp** field, as shown in Figure 2-7, Figure 2-8, and Figure 2-9. The **PgmOrder** field is 3 bits wide to allow up to 8 pipelines. The number of processor pipelines is specified in the *TCBCONFIG*<sub>PiN</sub> field. See Section 4.4, "TCBCONFIG Register (Reg 0)" on page 24.

| PgmOrder InsComp 1 |

|--------------------|

#### Figure 2-7 TF2 (Trace Format 2 Multi-Pipe)

| 29(45) | 14 | 13    | 12   | 11 9     | 8 6   | 5 3     | 2 | 1 | 0 |

|--------|----|-------|------|----------|-------|---------|---|---|---|

| AD     |    | TMode | TEnd | PgmOrder | ТТуре | InsComp | 0 | 0 | 0 |

#### Figure 2-8 TF3 (Trace Format 3 Multi-Pipe)

TF4 for multi-pipe trace is defined as was the case for single-pipe trace. In the example in Figure 2-9, the TEnd bit (bit 12) is set, and the TType field (bits 8:6) is set to **DT** ( $100_2$ ).

6

| 32(48) | 17 | 16    | 14    | 13    | 12 | 11 9     | 8 | 7 | 6 | 5 3     | 2 | 1 | 0 |

|--------|----|-------|-------|-------|----|----------|---|---|---|---------|---|---|---|

| AD     |    | LoadC | Order | TMode | 1  | PgmOrder | 1 | 0 | 0 | InsComp | 0 | 0 | 0 |

|        |    |       |       |       |    |          |   |   |   |         |   |   |   |

Figure 2-9 TF4 (Trace Format 4 Multi-Pipe)

## Trace Word Format

After compression of data into the Trace Formats, the trace information must be streamed to either on-chip or off-chip dedicated trace memory. As seen in the previous chapter, each of the major Trace Formats are of different size. This complicates the efficient storage of this information into a fixed-width on-chip memory. It also complicates the transmission of this data through a fixed width interface to off-chip memory. To simplify the memory overhead and pin bandwidth issues, the Trace Formats are first gathered into Trace Words of regular width. This section describes these Trace Words.

## 3.1 Trace Word

A Trace Word (TW) is defined to be 64 bits wide. A TW has a 4 bit type indicator on bits [3:0], and regular TF's stacked up in the remaining 60 bits of the word. Figure 3-1 shows the 64-bit wide TW.

| 63 4  | 3    | 0 |

|-------|------|---|

| Trace | Туре |   |

|       |      |   |

#### Figure 3-1 TW (Trace Word)

The **Trace** portion of a TW consists of one or more Trace Formats, TF1 through TF6. Note that trace formats TF1, TF2, TF5, and TF6 have a fixed size, while TF3 and TF4 can vary in size. The size of formats TF3 and TF4 is based on the number of *PDO\_AD* bits on the PDtrace<sup>TM</sup> interface. A further optimization is possible with an address on *PDO\_AD*. That is, the redundant sign bits (in the upper address bits) can be optionally chopped from the formats, especially if the format straddles two TWs. This happens when *PDO\_TType* is set to **TPC**, **TLA**, or **TSA**, TEnd is set to 1, and TMode is set to 0.

The processor mode is traced as a TF3 with *PDO\_TType* set to **TMOAS**. A **TMOAS** always uses 16 bits of AD, regardless of the PDO\_AD bus width. Therefore, when *PDO\_TType* is set to **TMOAS**, the TF3 format in a TW is defined to always have exactly 16 valid bits on the AD field, regardless of the *TCBCONTROLA*<sub>ADW</sub> field.

A TW is built by pushing in the TF's back to back until all 60 bits of the **Trace** field are used. If the last TF does not fit in **Trace**, it spills to the first bits of the **Trace** field in the next TW. The **Type** indicator is used to indicate where the first new TF starts in the new **Trace** field. This indirectly indicates the number of bits used to complete the TF from the previous TW.

Sometimes, when a TF cannot be completed in the remaining bits of a TW<sub>n</sub>, it is more efficient to discard those bits of the TW<sub>n</sub> and simply repeat all of them in the following TW<sub>n+1</sub>. This is indicated in TW<sub>n+1</sub> by setting **Type** to 1. When **Type** is 1, the first new TF of a TW starts at bit 0 in the **Trace** field. Since the previous TW<sub>n</sub> ended with an uncompleted TF, a Type of 1 in TW<sub>n+1</sub> instructs the decode software to discard the uncompleted TF in TW<sub>n</sub>. Table 3-1 describes the word types for the TW.

| Decimal<br>value of<br>the Type<br>field | The first new<br>TF starts at<br>this bit in the<br>Trace field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                        | N/A                                                             | This TW does not carry any trace information. The <b>Trace</b> field is set to all zeroes.<br>In the off-chip interface, the <b>Trace</b> field can be truncated to make the TW fit the bit-width of the off-chip interface.<br>For on-chip trace, this TW is not to be stored in memory.                                                                                                                                                                                                                                              |

| 1                                        | 0                                                               | This indicates a situation where a new TF is started at the beginning of this TW. This can happen when: (1) a new trace is begun, (2) the TF in the previous TW was completed, and (3) an incomplete TF at the end of the previous TW is discarded.<br>If the last trace format of the previous TW was a TF3 with: TType set to <b>TPC</b> , <b>TLA</b> or <b>TSA</b> , TEnd set to 1 and TMode set to 0, and with at least one AD bit, then that is considered a completed TF format, and no bits are discarded from the previous TW. |

| 2 - 14                                   | (Type - 1) * 4                                                  | The partial TF from the previous TW is completed in this TW in the bits available before the first new TF, i.e., bits 0((Type -1)*4)-1) in the Trace field.<br>If extra bits are available after completing the straddling TF, the rest of the bits until the first new TF start are undefined.<br>TF3 formats sending the last part of a relative address are allowed to cut the AD bits to only show the needed sign bits. This enables compression of sign-extended <i>PDO_AD</i> bits when the TF3 straddles a TW.                 |

| 15                                       | No new TF <sup>1</sup>                                          | The TF started in the previous TW could not be completed within 54 bits <sup>2</sup> . It might complete in this TW. But if it does not complete, then the next TW will have a <b>Type</b> value higher than one.                                                                                                                                                                                                                                                                                                                      |

| [2]: 54 bits is the                      | e maximum allowable                                             | rrently defined TF's, as the longest TF is only 49 bits wide.<br>Dits used to complete a TF from a previous $TW_{n-1}$ , if a new one is to start in $TW_n$ . This is so because a <b>Type</b> position (bit 54) in the <b>Trace</b> field, where a new TF will start.                                                                                                                                                                                                                                                                 |

| Table 3-1 Trace | Word Type   | e field description |

|-----------------|-------------|---------------------|

| Indic o I IIuce | , or a rype | c nera acoer iption |

As an example of how a TW is built, consider the trace sequence shown in Table 3-2. In this example, the *PDO\_AD* bus is assumed to be 16 bits wide (a zero value for *TCBCONTROLA*<sub>ADW</sub>).

| Cycle # | Trace Format                 | Cycle # | Trace Format                 |

|---------|------------------------------|---------|------------------------------|

| 1       | TF3 (16 significant AD bits) | 2       | TF3 (16 significant AD bits) |

| 3       | TF2                          | 4       | TF1                          |

| 5       | TF1                          | 6       | TF1                          |

| 7       | TF1                          | 8       | TF2                          |

| 9       | TF2                          | 10      | TF1                          |

| 12      | TF2                          | 11      | TF2                          |

| 13      | TF2                          | 14      | TF1                          |

| 15      | TF3 (5 significant AD bits)  | 16      | TF1                          |

| 17      | TF2                          | 18      | TF2                          |

| 19      | TF2                          | 20      | TF2                          |

Table 3-2 Example Trace sequence

| Cycle # | Trace Format                 | Cycle # | Trace Format         |

|---------|------------------------------|---------|----------------------|

| 21      | TF3 (11 significant AD bits) | 22      | TF1                  |

| 23      | TF3 (6 significant AD bits)  | 24      | TF6 (Stop indicator) |

Table 3-2 Example Trace sequence (Continued)

The TF sequence in Table 3-2 will create the set of TW's shown in Figure 3-2. The grayed out boxes with a "u" are unused bits. Grayed out boxes with an "s", show redundant sign-bits from a TF3 format. These sign-bits could not be compressed out, and must be included as part of the AD field. A "1" indicates the single bit of 1 in a TF1 format.

|    | Тгасе |           |         |           |         |       |         |         |         |       |       | Т   | ype      |     |     |       |   |   |

|----|-------|-----------|---------|-----------|---------|-------|---------|---------|---------|-------|-------|-----|----------|-----|-----|-------|---|---|

|    | 5     | 5         | 5       | 4         | 4       | 4     | 3       | 3       | 2       | 2     | 2     | 1   | 1        |     |     |       |   |   |

| TW | 9     | 6         | 2       | 8         | 4       | 0     | 6       | 2       | 8       | 4     | 0     | 6   | 2        | 8   | 4   | 0     | 3 | 0 |

| 1  | 1     | TF2       |         |           |         | TF3   |         |         |         |       |       |     | TF3      |     |     |       |   | 1 |

| 2  | TF2   | 2 1 s s s | s s s s | s s s s s |         |       | ГF3     |         | 1 T     | 'F2   | TF2   | TF2 | 1        | TF2 | TF2 | 1 1 1 |   | 1 |

| 3  |       | ]         | ΓF3     | 1         | s s s s | s     |         |         | TF3     |       |       | TF2 | TF       | 52  | TF2 | u TF2 |   | 2 |

| 4  | u u   | 1 u u u u | u u u u | u u u u u | u u u u | u u u | u u u u | u u u u | u u u u | u u u | u u u |     | TF6 (sto | op) |     | TF3   |   | 2 |

Figure 3-2 Trace Word from Example Trace in Table 3-2

In the example in Figure 3-2, the TF3 straddling  $TW_3/TW_4$  have had insignificant sign bits cut from the full TF3 format. It is optional for TCB hardware to do this extra compression of TF3 formats, but TW decode software must always be designed to handle this extra compression.

## 3.1.1 Cycle Inaccurate Trace

The TF1 format is needed only when a sequence of the trace must show cycle-by-cycle behavior of the processor without missing any cycles. When the trace regeneration software only needs to show the sequence of instructions executed, the TF1 format which shows processor stall cycles can be omitted. In this latter situation, an additional optimization removes bit zero on the other TF's before storing to trace memory. The example trace sequence in Table 3-2 will then produce the TW's shown in Figure 3-3. Note that, to reconstruct the trace accurately, external software must know what type of tracing was enabled at the TCB.

| 1  | Тгасе |       |          |             |         |         |       |     |           |         |           |         |         | T       | ype     |         |         |   |   |

|----|-------|-------|----------|-------------|---------|---------|-------|-----|-----------|---------|-----------|---------|---------|---------|---------|---------|---------|---|---|

|    | 5     | 5     | 5        | 4           | 4       | 4       |       | 3   | 3         | 2       | 2         | 2       | 1       | 1       |         |         |         |   |   |

| TW | 9     | 6     | 2        | 8           | 4       | 0       |       | 6   | 2         | 8       | 4         | 0       | 6       | 2       | 8       | 4       | 0       | 3 | 0 |

| 1  | TF    | 2     | TF2      |             |         | 1       | FF3   |     |           |         |           |         |         | TF3     |         |         |         |   | 1 |

| 2  | TF3   | TF2   | TI       | F2 TF2      | TF2     | s s :   | s s s | s s | s s s s   |         | TF3       |         |         | TF2     | TF2     | TF2     | TF2     |   | 1 |

| 3  |       | r.    | ΓF6 (sto | op)         | s s s s | s s s : | s s s | s   |           | TF3     |           | s       |         |         | TF3     |         |         |   | 6 |

| 4  | u u ı | u u u | u u u    | u u u u u u | u u u ı | u u u ı | u u u | uu  | u u u u u | u u u u | ı u u u u | u u u ı | 1 u u u | ı u u u | u u u u | u u u u | u u TF6 | ō | 2 |

Figure 3-3 Trace Word from Example Trace in Table 3-2 (No TF1 trace)

In the example shown in Figure 3-3, the TF3 straddling  $TW_2/TW_3$  have had insignificant sign bits cut from the full TF3 format. It is optional for TCB hardware to make this extra compression of TF3 format, but TW decode software must be able to handle this.

Additionally when not tracing for cycle accurate information, the TF6 formats TCBcode 0001 and 0101 are omitted from the Trace Words (not shown in Figure 3-2 and Figure 3-3). Cycle accurate versus cycle inaccurate tracing in controlled by the *TCBCONTROLB*<sub>CA</sub> bit.

#### 3.1.1.1 Trace Word collection.

Figure 3-4 shows how the TCB builds the Trace Words from the Trace Formats cycle by cycle, as the PDtrace interface sends trace information. Trace Words from Figure 3-2 are used.

|       |    |       |         |         |         |         |           |           | T    | race    |         |       |     |     |        |     |          |            | Туре     |

|-------|----|-------|---------|---------|---------|---------|-----------|-----------|------|---------|---------|-------|-----|-----|--------|-----|----------|------------|----------|

|       |    | 5     | 5       | 5       | 4       | 4       | 4         | 3         | 3    | 2       | 2       | 2     | 1   |     | 1      |     |          |            |          |

| Cycle | TW | 9     | 6       | 2       | 8       | 4       | 0         | 6         | 2    | 8       | 4       | 0     | 6   |     | 2 8    | 8 4 |          | 0          | 3 0      |

| 1     |    |       |         |         |         | free    |           |           |      |         |         |       |     | TF3 |        |     |          |            | 1        |

| 2     | 1  | f     | ree     |         |         |         | TF3       |           |      |         |         |       |     | TF3 |        |     |          |            | 1        |

| 3     | 1  | f     | TF2     |         |         |         | TF3       |           |      |         |         |       |     | TF3 |        |     |          |            | 1        |

| 4     |    | 1     | TF2     |         |         |         | TF3       |           |      |         |         |       |     | TF3 |        |     |          |            | 1        |

| 5     |    |       |         |         |         |         |           |           | fr   | ee      |         |       |     |     |        |     |          | 1          | 1        |

| 6     |    |       |         |         |         |         |           |           | fre  | e       |         |       |     |     |        |     |          | 1 1        | 1        |

| 7     |    |       |         |         |         |         |           |           | free |         |         |       |     |     |        |     | 1        | 1 1        | 1        |

| 8     |    |       |         |         |         |         |           | 1         | free |         |         |       |     |     |        | TF2 | 1        | 1 1        | 1        |

| 9     |    |       |         |         |         |         |           | free      |      |         |         |       |     |     | TF2    | TF2 | 1        | 1 1        | 1        |

| 10    |    |       |         |         |         |         |           | free      |      |         |         |       |     | 1   | TF2    | TF2 | 1        | 1 1        | 1        |

| 11    | 2  |       |         |         |         |         | free      |           |      |         |         |       | TF2 | 1   | TF2    | TF2 | 1        | 1 1        | <b>I</b> |

| 12    |    |       |         |         |         | f       | ree       |           |      |         |         | TF2   | TF2 | 1   | TF2    | TF2 | 1        |            |          |

| 13    |    |       |         |         |         | free    |           |           |      |         | TF2     | TF2   | TF2 | 1   | TF2    | TF2 | 1        | 1 1        | 1        |

| 14    |    |       |         |         |         | free    |           |           |      | 1       | TF2     | TF2   | TF2 | 1   | TF2    | TF2 | 1        |            |          |

| 15    |    | free  | s s s   | s s s s | s s s s |         | 1         | ГF3       |      | 1       | TF2     | TF2   | TF2 | 1   | TF2    | TF2 | 1        | 1 1        | <b>I</b> |

| 16    |    | free  |         | s s s s | s s s s |         |           | ГF3       |      |         | TF2     | TF2   | TF2 | 1   | TF2    | TF2 | 1        |            |          |

| 17    |    | TF2   | lsss    | s s s s | s s s s |         | ]         | ГF3       |      | 1       | TF2     | TF2   | TF2 | 1   | TF2    | TF2 |          | 1 1        |          |

| 10    |    |       |         |         |         |         |           |           | free |         |         |       |     |     |        |     |          | TF2        | 2        |

| 18    |    |       |         |         |         |         |           |           | ee   |         |         |       |     | _   |        | TF2 |          | TF2        | 2        |

| 19    | •  |       |         |         |         |         | 6         | free      |      |         |         |       | 750 | _   | TF2    | TF2 |          | TF2        | 2        |

| 20    | 3  |       |         | £       |         |         | free      |           |      |         |         |       | TF2 | _   | TF2    | TF2 |          | TF2        | 2        |

| 21    |    |       |         | free    | 1       |         | 5 S       |           |      | FF3     |         |       | TF2 | _   | TF2    | TF2 |          | TF2        | 2        |

| 22    |    |       |         | free    |         |         | s s       |           |      | FF3     |         |       | TF2 | _   | TF2    | TF2 |          | TF2        | 2        |

| 23    |    |       |         | rf3     |         | S S S S | 5 S       |           | free | rF3     |         |       | TF2 |     | TF2    | TF2 |          | TF2<br>TF3 | 22       |

| 24    | 4  | u u ı | ı u u u | u u u u | u u u u | u u u u | 1 u u u 1 | u u u u ı |      | 1 u u u | ı u u u | u u u |     | TF6 | (stop) |     | <u> </u> | F3<br>F3   | 2        |

Figure 3-4 Cycle by cycle Trace Word from Example Trace in Table 3-2

## **3.2 End of Trace indication.**

In the examples in the previous section, the Trigger TF6 (stop: TCBcode == 0100) was used to indicate an End Trigger and this implied an end to the tracing as well. This stop trigger deasserts  $TCBCONTROLB_{EN}$  and the TCB flushes out

the current TW. However, the  $TCBCONTROLB_{EN}$  bit can be deasserted for other reasons, and this trace end must be indicated externally using a different mechanism to distinguish this from the end-trigger case. The recommended method to accomplish this is to let the TCB fill the un-used bits in the last TW with zeroes. Note that nine bits of consecutive zeroes in the Trace field will be identified as a TF3 with no information, that is, InsComp and TType are both zero. This will never be ordinarily generated by the Trace Format generator, and can therefore be used as a end-of-trace indicator.

If less than nine bits remain in the last TW, then an incomplete TF is detected by trace software. After that no additional TW are generated by the TCB. This should not be a problem for trace re-generating software, as this is just like any other arbitrary cut in the trace stream.

## 3.3 On-chip Trace Memory Format

The on-chip trace memory is defined to be a 64-bit wide memory. The TW's defined in Section 3.1, "Trace Word", are stored in consecutive address locations. The trace memory is only written when a full TW is available, hence a new TW might not be written each cycle, since a new TW might not be created each cycle.

The memory image will exactly match the TW sequence shown in Figure 3-2 on page 11 or Figure 3-3 on page 11, depending on whether TF1 formats are included.

## 3.4 Probe Trace Word transmission

Please see Chapter 8, "TCtrace IF," on page 43 for a detailed description of the TCtrace IF and Chapter 9, "Probe IF," on page 47 for a detailed description of the PIB module.

The Probe interface can support a  $TR_DATA$  bus width of 4, 8, or 16 bits. When a TW is ready to be sent, it is put on the  $TC_Data$  pins to the PIB. The PIB will feed the TW through on the available  $TR_DATA$  pins, starting with  $TC_Data[n:0]$  on the  $TR_DATA[n:0]$  utilized pins. Depending on the value of n, this will take 16, 8, or 4 transmissions. If a clock multiplier is used in the PIB, then 2, 4, 8, or 16 transmissions can be completed in one core clock cycle.

As long as no new TW is available for transmission, the *TC\_Data* bus will show all zeros, allowing the PIB to keep transmitting this on the *TR\_DATA* bits to also show all zeros.

On an 8 pin *TR\_DATA* trace interface, running at core-clock frequency, the trace from the TW's in Figure 3-4 will look as shown in Figure 3-5 on the Probe IF. This assumes sufficient buffering to hold the TW's in the TCB when they become available for transmission, and a latency of one clock before the first part of an available TW on the *TC\_data* bus, appears on the *TR\_DATA* pins.

| Cycle | TR_DATA[7:0]            | Cycle | TR_DATA[7:0]            | Cycle | TR_DATA[7:0]            | Cycle | TR_DATA[7:0]            |

|-------|-------------------------|-------|-------------------------|-------|-------------------------|-------|-------------------------|

| 1     | zero                    | 11    | TW <sub>1</sub> [55:48] | 21    | TW <sub>2</sub> [31:24] | 31    | TW <sub>3</sub> [47:40] |

| 2     | zero                    | 12    | TW <sub>1</sub> [63:56] | 22    | TW <sub>2</sub> [39:32] | 32    | TW <sub>3</sub> [55:48] |

| 3     | zero                    | 13    | zero                    | 23    | TW <sub>2</sub> [47:40] | 33    | TW <sub>3</sub> [63:56] |

| 4     | zero                    | 14    | zero                    | 24    | TW <sub>2</sub> [55:48] | 34    | TW <sub>4</sub> [7:0]   |

| 5     | TW <sub>1</sub> [7:0]   | 15    | zero                    | 25    | TW <sub>2</sub> [63:56] | 35    | TW <sub>4</sub> [15:8]  |

| 6     | TW <sub>1</sub> [15:8]  | 16    | zero                    | 26    | TW <sub>3</sub> [7:0]   | 36    | TW <sub>4</sub> [23:16] |

| 7     | TW <sub>1</sub> [23:16] | 17    | zero                    | 27    | TW <sub>3</sub> [15:8]  | 37    | zero                    |

| 8     | TW <sub>1</sub> [31:24] | 18    | TW <sub>2</sub> [7:0]   | 28    | TW <sub>3</sub> [23:16] | 38    | zero                    |

| 9     | TW <sub>1</sub> [39:32] | 19    | TW <sub>2</sub> [15:8]  | 29    | TW <sub>3</sub> [31:24] | 39    | zero                    |

| 10    | TW <sub>1</sub> [47:40] | 20    | TW <sub>2</sub> [23:16] | 30    | TW <sub>3</sub> [39:32] | 40    | zero                    |

Figure 3-5 Cycle by cycle TR\_DATA (8-bit) of Example Trace in Table 3-2

The probe sampling the  $TR_DATA$  pins should look for a non-zero transmission. When that happens, the following bits up to a collective count of 64-bits (i.e. including the first non-zero 4/8/16-bit value) will form a TW. After 64-bits, the probe should re-start looking for a new non-zero transmission. A non zero transmission can start at any time after a full TW is received.

## Trace Control Block Registers

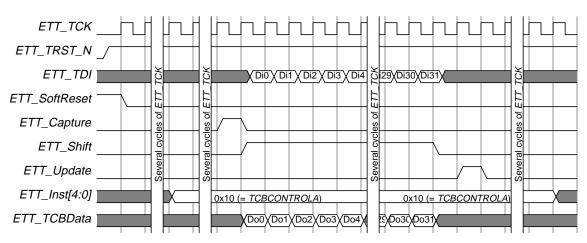

The TCB uses several registers to control its operation. These registers are accessed via the EJTAG TAP interface. This chapter describes these registers in detail. These registers are shown in Table 4-1 and Table 4-2.

| Register Name | EJTAG TAP<br>controller instruction<br>value | Description                                                                                                                                                                                                                                                                                                                    |

|---------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCBCONTROLA   | 0x10                                         | Control register in the TCB mainly used for controlling the trace input signals to the core on the PDtrace interface.                                                                                                                                                                                                          |

| TCBCONTROLB   | 0x11                                         | Control register in the TCB that is mainly used to specify what to<br>do with the trace information. The REG [25:21] field in this register<br>specifies the number of the TCB internal register accessed by the<br>TCBDATA register. A list of all the registers that can be accessed<br>by the TCBDATA register is shown in. |

| TCBDATA       | 0x12                                         | This is used to access registers specified by the REG field in the TCBCONTROLB register.                                                                                                                                                                                                                                       |

#### **Table 4-1 Registers in the Trace Control Block**

## Table 4-2 Registers selected by $TCBCONTROLB_{REG}$ (accessed through TCBDATA).

| REG[4:0] | Register<br>Selected | Register Description                                                                                                                                                                                                                                                                                                         | Compliance                               |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 0        | TCBCONFIG            | TCB Configuration registerholds information about the hardware configuration of the TCB.                                                                                                                                                                                                                                     | Required                                 |

| 1-3      | Reserved             | Reserved for future use.                                                                                                                                                                                                                                                                                                     | Reserved                                 |

| 4        | TCBTW                | Trace Word read register. This register holds the Trace Word just read from on-line trace memory.                                                                                                                                                                                                                            |                                          |

| 5        | TCBRDP               | Trace Word Read pointer. It points to the location in the on-line trace<br>memory where the next Trace Word will be read. A TW read has the<br>side-effect of post-incrementing this register value to point to the next<br>TW location. (A maximum value wraps the address around to the<br>beginning of the trace memory). | Required if<br>on-chip memory<br>exists. |

| 6        | TCBWRP               | Trace Word Write pointer. It points to the location in the on-line trace memory where the next new Trace Word will be written.                                                                                                                                                                                               |                                          |

| 7        | TCBSTP               | Trace Word Start Pointer. This points to the location of the oldest TW in the on-line trace memory.                                                                                                                                                                                                                          |                                          |

| 8-15     | Reserved             | Reserved for future use.                                                                                                                                                                                                                                                                                                     | Reserved                                 |

| 16-23    | TCBTRIGx             | Trigger Control registers 0-7 are used to specify some conditions that cause the firing of triggers, and to control the resulting action.                                                                                                                                                                                    | Optional                                 |

| 24-31    | Reserved             | Reserved for future use.                                                                                                                                                                                                                                                                                                     | Reserved                                 |

## 4.1 TCBCONTROLA Register

The trace output from the processor on the PDtrace interface can be controlled by the trace input signals to the processor from the TCB. The TCB uses a control register, TCBCONTROLA, whose values are used to change the signal values on the PDtrace input interface. External software (i.e., debugger), can therefore manipulate the trace output by writing the TCBCONTROLA register.

The *TCBCONTROLA* register is written by an EJTAG TAP controller instruction, *TCBCONTROLA* (0x10). See Ref. [1] for more details regarding new TAP instructions.

Compliance: This register is required.

The format of the TCBCONTROLA register is shown below, and the fields are described in Table 4-3.

|   | TCBCONTROLA Register Format |    |    |    |      |     |     |    |    |    |    |    |    |    |    |      |   |   |    |    |    |

|---|-----------------------------|----|----|----|------|-----|-----|----|----|----|----|----|----|----|----|------|---|---|----|----|----|

| 3 | 1                           | 27 | 26 | 25 | 24   | 23  | 22  | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12   | 5 | 4 | 3  | 1  | 0  |

|   | Impl                        |    | 0  | VM | odes | ADW | SyP |    | TB | IO | D  | E  | S  | K  | U  | ASID |   | G | Mo | de | On |

| Fiel   | ds                                                                                          |                                                | Description                                                                                          |          | Read/ | Reset State | Compliance |

|--------|---------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------|----------|-------|-------------|------------|

| Name   | Bits                                                                                        |                                                |                                                                                                      |          | Write |             |            |

| Impl   | 31:27                                                                                       | This field is<br>Refer to the<br>definition of | reserved for implementation specific use<br>processor specification for the format an<br>this field. | e.<br>nd |       | Undefined   | Optional   |

| 0      | 26                                                                                          | Reserved for<br>returns zero                   | r future use. Must be written as zero;<br>on read.                                                   |          | 0     | 0           | Reserved   |

|        |                                                                                             | by the proce                                   | ecifies the type of tracing that is supporte<br>ssor, as follows:                                    | ed       |       |             |            |

|        |                                                                                             | Encoding                                       | Meaning                                                                                              |          |       |             |            |

|        |                                                                                             | 00                                             | PC tracing only                                                                                      |          |       |             |            |

| VModes | 25:24                                                                                       | 01                                             | PC and load and store address tracing only                                                           |          | R     | Preset      | Required   |

|        |                                                                                             | 10                                             | PC, load, and store address, and load and store data.                                                |          |       |             |            |

|        |                                                                                             | 11                                             | Reserved                                                                                             |          |       |             |            |

|        |                                                                                             | This field is                                  | preset to the value of <i>PDO_ValidModes</i> .                                                       |          |       |             |            |

|        |                                                                                             | PDO_AD bi                                      | is width.                                                                                            |          |       |             |            |

| ADW    | W 23 0: The <i>PDO_AD</i> bus is 16 bits wide.<br>1: The <i>PDO_AD</i> bus is 32 bits wide. |                                                |                                                                                                      |          |       | Preset      | Required   |

#### Table 4-3 TCBCONTROLA Register Field Descriptions

| Fields |       |                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      | on                                                                                              |             | Read/ | Reset State | Compliance |  |

|--------|-------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------|-------|-------------|------------|--|

| Name   | Bits  |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                 |             | Write |             |            |  |

|        |       | The period<br>synchroniza<br>shown in th<br>on-chip or o                                     | icate the synchroniz<br>(in cycles) between<br>ation information is<br>e table below, when to<br>off-chip (as determin<br><i>ROLB</i> <sub>OfC</sub> bit).                                                                                                                                                                                                                                                                                       | which the periodic<br>to be sent is defined<br>he trace buffer is eit                           | 1 as        |       |             |            |  |