# MIPS32® 4Kc® Processor Core Datasheet

The MIPS32® 4Kc® core from MIPS® Technologies is a member of the MIPS32 4K® processor core family. It is a highperformance, low-power, 32-bit MIPS RISC core designed for custom system-on-silicon applications. The core is designed for semiconductor manufacturing companies, ASIC developers, and system OEMs who want to rapidly integrate their own custom logic and peripherals with a high-performance RISC processor. It is highly portable across processes, and can be easily integrated into full system-on-silicon designs, allowing developers to focus their attention on end-user products. The 4Kc core is ideally positioned to support new products for emerging segments of the digital consumer, network, systems, and information management markets, enabling new tailored solutions for embedded applications.

The 4Kc core implements the MIPS32 Architecture and contains all MIPS II<sup>TM</sup> instructions; special multiply-accumulate (MAC), conditional move, prefetch, wait, and leading zero/one detect instructions; and the 32-bit privileged resource architecture. The R4000®-style Memory Management Unit contains 3-entry instruction and data TLBs (ITLB/DTLB) and a 16 dual-entry joint TLB (JTLB) with variable page sizes.

The synthesizable 4Kc core implements single cycle MAC instructions, which enable DSP algorithms to be performed efficiently. The Multiply/Divide Unit (MDU) allows 32-bit x 16-bit MAC instructions to be issued every cycle. A 32-bit x 32-bit MAC instruction can be issued every 2 cycles.

Instruction and data caches are fully configurable from 0 - 16 Kbytes in size. In addition, each cache can be organized as direct-mapped or 2-way, 3-way, or 4-way set associative. Load and fetch cache misses only block until the critical word becomes available. The pipeline resumes execution while the remaining words are being written to the cache. Both caches are virtually indexed and physically tagged to allow them to be accessed in the same clock that the address is translated.

An optional Enhanced JTAG (EJTAG) block allows for single-stepping of the processor as well as instruction and data virtual address breakpoints.

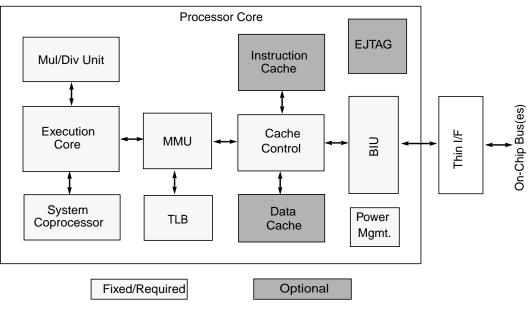

Figure 1 shows a block diagram of the 4Kc core. The core is divided into required and optional blocks as shown.

Figure 1 4Kc Core Block Diagram

## Features

- 32-bit Address and Data Paths

- MIPS32-Compatible Instruction Set

- All MIPS II Instructions

- Multiply-Accumulate and Multiply-Subtract Instructions (MADD, MADDU, MSUB, MSUBU)

- Targeted Multiply Instruction (MUL)

- Zero/One Detect Instructions (CLZ, CLO)

- Wait Instruction (WAIT)

- Conditional Move Instructions (MOVZ, MOVN)

- Prefetch Instruction (PREF)

- Programmable Cache Sizes

- Individually configurable instruction and data caches

- Sizes from 0 16KB

- Direct Mapped, 2-, 3-, or 4-Way Set Associative

- Loads block only until critical word is available

- Write-through, no write-allocate

- 16-byte cache line size, word sectored

- Virtually indexed, physically tagged

- Cache line locking support

- Non-blocking prefetches

- Scratchpad RAM Support

- Can optionally replace 1 way of the I- and/or D-cache with a fast scratchpad RAM

- 20 index address bits allow access of arrays up to 1MB

- Memory-mapped registers attached to the scratchpad port can be used as a coprocessor interface

- R4000-style Privileged Resource Architecture

- Count/Compare registers for real-time timer interrupts

- I and D watch registers for SW breakpoints

- Separate interrupt exception vector

- Programmable Memory Management Unit

- 16 dual-entry R4000-style JTLB with variable page size

- 3-entry ITLB

- 3-entry DTLB

- Simple Bus Interface Unit (BIU)

- All I/Os fully registered

- Separate unidirectional 32-bit address and data buses

- Two 16-byte collapsing write buffers

- Multiply/Divide Unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 34 clock latency (dividend (*rs*) sign extension-dependent)

- Power Control

- Minimum frequency: 0 MHz

- Power-down mode (triggered by WAIT instruction)

- Support for software-controlled clock divider

- EJTAG Debug Support with single stepping, virtual instruction and data address breakpoints

## **Architecture Overview**

The 4Kc core contains both required and optional blocks. Required blocks are the lightly shaded areas of the block diagram in Figure 1 and must be implemented to remain MIPS-compliant. Optional blocks can be added to the 4Kc core based on the needs of the implementation.

The required blocks are as follows:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Memory Management Unit (MMU)

- Transition Lookaside Buffer (TLB)

- Cache Controllers

- Bus Interface Unit (BIU)

- Power Management

Optional blocks include:

- Instruction Cache

- Data Cache

- Scratchpad RAM

- Enhanced JTAG (EJTAG) Controller

The section entitled "4Kc Core Required Logic Blocks" on page 3 discusses the required blocks. The section entitled "4Kc Core Optional Logic Blocks" on page 12 discusses the optional blocks.

# **Pipeline Flow**

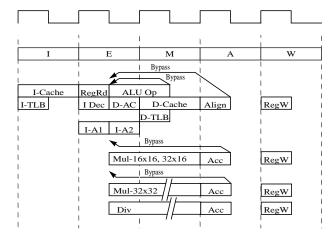

The 4Kc core implements a 5-stage pipeline with performance similar to the R3000® pipeline. The pipeline allows the processor to achieve high frequency while minimizing device complexity, reducing both cost and power consumption.

The 4Kc core pipeline consists of five stages:

- Instruction (I Stage)

- Execution (E Stage)

- Memory (M Stage)

- Align (A Stage)

- Writeback (W stage)

The 4Kc core implements a bypass mechanism that allows the result of an operation to be forwarded directly to the instruction that needs it without having to write the result to the register and then read it back.

Figure 2 shows a timing diagram of the 4Kc core pipeline.

#### I Stage: Instruction Fetch

During the Instruction fetch stage:

• An instruction is fetched from instruction cache.

#### E Stage: Execution

During the Execution stage:

- Operands are fetched from register file.

- The arithmetic logic unit (ALU) begins the arithmetic or logical operation for register-to-register instructions.

- The ALU calculates the data virtual address for load and store instructions.

- The ALU determines whether the branch condition is true and calculates the virtual branch target address for branch instructions.

- Instruction logic selects an instruction address.

- All multiply and divide operations begin in this stage.

#### **M Stage: Memory Fetch**

During the memory fetch stage:

• The arithmetic ALU operation completes.

- The data cache fetch and the data virtual-to-physical address translation are performed for load and store instructions.

- Data cache look-up is performed and a hit/miss determination is made.

- A 16x16 or 32x16 multiply calculation completes.

- A 32x32 multiply operation stalls for one clock in the M stage.

- A divide operation stalls for a maximum of 34 clocks in the M stage. Early-in sign extension detection on the dividend will skip 7, 15, or 23 stall clocks.

#### A Stage: Align

During the Align stage:

- A separate aligner aligns load data to its word boundary.

- A 16x16 or 32x16 multiply operation performs the carry-propagate-add. The actual register writeback is performed in the W stage.

- A MUL operation makes the result available for writeback. The actual register writeback is performed in the W stage.

#### W Stage: Writeback

• For register-to-register or load instructions, the instruction result is written back to the register file during the W stage.

# 4Kc Core Required Logic Blocks

The 4Kc core consists of the following required logic blocks as shown in Figure 1. These logic blocks are defined in the following subsections:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Memory Management Unit (MMU)

- Transition Lookaside Buffer (TLB)

- Cache Controller

- Bus Interface Control (BIU)

- Power Management

## **Execution Unit**

The 4Kc core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The 4Kc core contains thirty-two 32-bit general-purpose registers used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instructions streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter & Store Aligner

## Multiply/Divide Unit (MDU)

The 4Kc core contains a multiply/divide unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the integer unit (IU) pipeline and does not stall when the IU pipeline stalls. This setup allows long-running MDU operations, such as a divide, to be partially masked by system stalls and/or other integer unit instructions.

The MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The 4Kc core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If rs is 8 bits wide, 23 iterations are skipped. For a 16-bit-wide rs, 15 iterations are skipped, and for a 24-bit-wide rs, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the 4Kc core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks. For a more detailed discussion of latencies and repeat rates, refer to Chapter 2 of the *MIPS32 4K*® *Processor Core Family Software User's Manual*.

Table 1 4Kc Core Integer Multiply/Divide Unit Latencies

and Repeat Rates

| Opcode                    | Operand<br>Size<br>(mul <i>rt</i> )<br>(div <i>rs</i> ) | Latency | Repeat<br>Rate |

|---------------------------|---------------------------------------------------------|---------|----------------|

| MULT/MULTU,               | 16 bits                                                 | 1       | 1              |

| MADD/MADDU,<br>MSUB/MSUBU | 32 bits                                                 | 2       | 2              |

| MUL                       | 16 bits                                                 | 2       | 1              |

|                           | 32 bits                                                 | 3       | 2              |

| DIV/DIVU                  | 8 bits                                                  | 12      | 11             |

|                           | 16 bits                                                 | 19      | 18             |

|                           | 24 bits                                                 | 26      | 25             |

|                           | 32 bits                                                 | 33      | 32             |

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the general-purpose register file.

As an enhancement to the MIPS II ISA, the 4Kc core implements an additional multiply instruction, MUL, which specifies that multiply results be placed in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction, required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, multiply-add (MADD) and multiply-subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

## System Control Coprocessor (CP0)

In the MIPS architecture, CP0 is responsible for the virtualto-physical address translation and cache protocols, the exception control system, the processor's diagnostics capability, the operating modes (kernel, user, and debug), and interrupts enabled or disabled. Configuration information such as cache size and set associativity is available by accessing the CP0 registers, listed in Table 2.

| Table 2 | Coprocessor | 0 Registers | in Numerical Order |

|---------|-------------|-------------|--------------------|

|---------|-------------|-------------|--------------------|

| Register<br>Number | Register<br>Name      | Function                                                                 |

|--------------------|-----------------------|--------------------------------------------------------------------------|

| 0                  | Index <sup>1</sup>    | Index into the TLB array.                                                |

| 1                  | Random <sup>1</sup>   | Randomly generated index into the TLB array.                             |

| 2                  | EntryLo0 <sup>1</sup> | Randomly generated index into the TLB array.                             |

| 3                  | EntryLo1 <sup>1</sup> | Low-order portion of the TLB<br>entry for odd-numbered virtual<br>pages. |

| 4                  | Context <sup>2</sup>  | Pointer to page table entry in memory.                                   |

| 5                  | PageMask <sup>1</sup> | Control for variable page sizes in TLB entries.                          |

| 6                  | Wired <sup>1</sup>    | Controls the number of fixed ("wired") TLB entries.                      |

| 7                  | Reserved              | Reserved.                                                                |

| Register<br>Number                                                                                                                              | Register<br>Name      | Function                                                           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------|--|

| 8                                                                                                                                               | BadVAddr <sup>2</sup> | Reports the address for the most recent address-related exception. |  |

| 9                                                                                                                                               | Count <sup>2</sup>    | Processor cycle count.                                             |  |

| 10                                                                                                                                              | EntryHi <sup>1</sup>  | High-order portion of the TLB entry.                               |  |

| 11                                                                                                                                              | Compare <sup>2</sup>  | Timer interrupt control.                                           |  |

| 12                                                                                                                                              | Status <sup>2</sup>   | Processor status and control.                                      |  |

| 13                                                                                                                                              | Cause <sup>2</sup>    | Cause of last general exception.                                   |  |

| 14                                                                                                                                              | EPC <sup>2</sup>      | Program counter at last exception.                                 |  |

| 15                                                                                                                                              | PRId                  | Processor identification and revision.                             |  |

| 16                                                                                                                                              | Config                | Configuration register.                                            |  |

| 16                                                                                                                                              | Config1               | Configuration register 1.                                          |  |

| 17                                                                                                                                              | LLAddr                | Load linked address.                                               |  |

| 18                                                                                                                                              | WatchLo <sup>2</sup>  | Low-order watchpoint address.                                      |  |

| 19                                                                                                                                              | WatchHi <sup>2</sup>  | High-order watchpoint address.                                     |  |

| 20 - 22                                                                                                                                         | Reserved              | Reserved.                                                          |  |

| 23                                                                                                                                              | Debug <sup>3</sup>    | Debug control and exception status.                                |  |

| 24                                                                                                                                              | DEPC <sup>3</sup>     | Program counter at last debug exception.                           |  |

| 25 - 27                                                                                                                                         | Reserved              | Reserved.                                                          |  |

| 28                                                                                                                                              | TagLo/<br>DataLo      | Low-order portion of cache tag interface.                          |  |

| 29                                                                                                                                              | Reserved              | Reserved.                                                          |  |

| 30                                                                                                                                              | ErrorEPC <sup>2</sup> | Program counter at last error.                                     |  |

| 31                                                                                                                                              | DeSave <sup>3</sup>   | Debug handler scratchpad register.                                 |  |

| <ol> <li>Registers used in memory management.</li> <li>Registers used in exception processing.</li> <li>Registers used during debug.</li> </ol> |                       |                                                                    |  |

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including boundary cases in data, external events, or program errors. Table 3 shows the exception types in order of priority.

| Exception      | Description                                                                                                                              |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Reset          | Assertion of SI_ColdReset signal.                                                                                                        |

| Soft Reset     | Assertion of SI_Reset signal.                                                                                                            |

| DSS            | EJTAG Debug Single Step.                                                                                                                 |

| DINT           | EJTAG Debug Interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input, or by setting the EjtagBrk bit in the ECR register. |

| NMI            | Assertion of <i>EB_NMI</i> signal.                                                                                                       |

| Machine Check  | TLB write that conflicts with an existing entry.                                                                                         |

| Interrupt      | Assertion of unmasked hardware or software interrupt signal.                                                                             |

| Deferred Watch | Deferred Watch (unmasked by K DM->!(K DM) transition).                                                                                   |

| DIB            | EJTAG debug hardware instruction break matched.                                                                                          |

| WATCH          | A reference to an address in one of the watch registers (fetch).                                                                         |

| AdEL           | Fetch address alignment error.<br>Fetch reference to protected address.                                                                  |

| TLBL           | Fetch TLB miss.                                                                                                                          |

| TLBL           | Fetch TLB hit to page with V=0.                                                                                                          |

| IBE            | Instruction fetch bus error.                                                                                                             |

| DBp            | EJTAG Breakpoint (execution of SDBBP instruction).                                                                                       |

| Sys            | Execution of SYSCALL instruction.                                                                                                        |

| Вр             | Execution of BREAK instruction.                                                                                                          |

| RI             | Execution of a Reserved Instruction.                                                                                                     |

| CpU            | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                            |

| Ov             | Execution of an arithmetic instruction that overflowed.                                                                                  |

| Tr             | Execution of a trap (when trap condition is true).                                                                                       |

| DDBL / DDBS    | EJTAG Data Address Break (address<br>only) or EJTAG Data Value Break on<br>Store (address+value).                                        |

| Table 3 | 4Kc Core Exception Types |

|---------|--------------------------|

|---------|--------------------------|

#### Table 3 4Kc Core Exception Types (Continued)

| Exception | Description                                                           |

|-----------|-----------------------------------------------------------------------|

| WATCH     | A reference to an address in one of the watch registers (data).       |

| AdEL      | Load address alignment error.<br>Load reference to protected address. |

| AdES      | Store address alignment error.<br>Store to protected address.         |

| TLBL      | Load TLB miss.                                                        |

| TLBL      | Load TLB hit to page with V=0.                                        |

| TLBS      | Store TLB miss.                                                       |

| TLBS      | Store TLB hit to page with V=0.                                       |

| TLB Mod   | Store to TLB page with D=0.                                           |

| DBE       | Load or store bus error.                                              |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.          |

### **Modes of Operation**

The 4Kc core supports three modes of operation: user mode, kernel mode, and debug mode. User mode is most often used for applications programs. Kernel mode is typically used for handling exceptions and operating system kernel functions, including CP0 management and I/ O device accesses. An additional Debug mode is used during system bring-up and software development. Refer to the EJTAG section for more information on debug mode.

| 0xFFFFFFF                                                 | [                                                            | n     |

|-----------------------------------------------------------|--------------------------------------------------------------|-------|

|                                                           | Memory Mapped                                                |       |

| 0xFF400000<br>0xFF3FFFFF<br>0xFF200000                    | Memory/EJTAG1                                                | kseg3 |

| 0xF1FFFFFF<br>0xE0000000                                  | Memory Mapped                                                |       |

| 0xDFFFFFFF                                                | Kernel virtual address space                                 | kseg2 |

| 0xC0000000                                                | Mapped, 512 MB                                               |       |

| 0xBFFFFFFF                                                | Kernel virtual address space<br>Unmapped, 512 MB<br>Uncached | kseg1 |

| 0x9FFFFFFF                                                | Kernel virtual address space<br>Unmapped, 512 MB             | kseg0 |

| 0x8000000<br>0x7FFFFFF                                    | User virtual address space<br>Mapped, 2048 MB                | kuseg |

| 0x00000000                                                |                                                              |       |

| 1. This space is mapped to memory in user of kernel mode. |                                                              |       |

1. This space is mapped to memory in user of kernel mode, and by the EJTAG module in debug mode.

Figure 3 4Kc Core Virtual Address Map

## Memory Management Unit (MMU)

The 4Kc core contains a fully functional MMU that interfaces between the execution unit and the cache controller. Although the 4Kc core implements a 32-bit architecture, the MMU is modeled after that found in the 64-bit R4000 family.

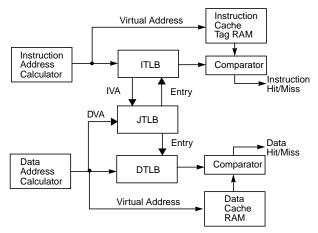

The TLB consists of two address translation buffers: a 16dual-entry, fully associative Joint TLB (JTLB) and two 3entry, fully associative Instruction/Data TLBs (ITLB/ DTLB).

When an instruction address is calculated, the virtual address is compared to the contents of the 3-entry ITLB. If the address is not found in the ITLB, the JTLB is accessed. If the entry is found in the JTLB, that entry is then written into the ITLB. If the address is not found in the JTLB, a TLB refill exception is taken.

When a data address is calculated, the virtual address is compared to both the 3-entry DTLB and the JTLB. If the address is not found in the DTLB, but is found in the JTLB, that address is immediately written to the DTLB. If the address is not found in the JTLB, a TLB refill exception is taken.

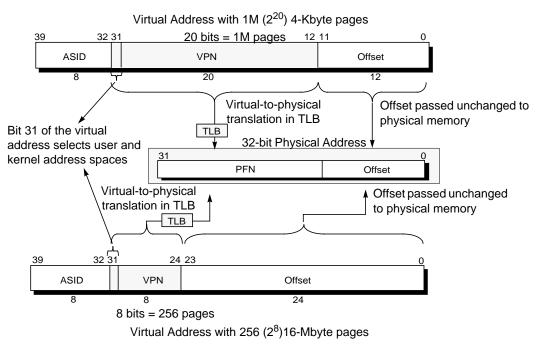

Figure 4 shows how the ITLB, DTLB, and JTLB are implemented in the 4Kc core.

Figure 4 Address Translation During a Cache Access

## Translation Lookaside Buffer (TLB)

The TLB consists of three address translation buffers:

- 16 dual-entry fully associative Joint TLB (JTLB)

- 3-entry fully associative Instruction TLB (ITLB)

- 3-entry fully associative Data TLB (DTLB)

### Joint TLB (JTLB)

The 4Kc core implements a 16-dual-entry, fully associative JTLB that maps 32 virtual pages to their corresponding physical addresses. The JTLB is organized as 16 pairs of even and odd entries containing pages that range in size from 4 Kbytes to 16 Mbytes into the 4-Gbyte physical address space. The purpose of the TLB is to translate virtual addresses and their corresponding ASIDs into a physical memory address. The translation is performed by comparing the upper bits of the virtual address (along with the ASID) against each of the entries in the *tag* portion of the joint TLB structure.

The JTLB is organized in page pairs to minimize the overall size. Each *tag* entry corresponds to 2 data entries: an even page entry and an odd page entry. The highest order virtual address bit not participating in the tag comparison is

used to determine which of the data entries is used. Since page size can vary on a page-pair basis, the determination of which address bits participate in the comparison and which bit is used to make the even-odd determination is decided dynamically during the TLB look-up.

#### **Instruction TLB (ITLB)**

The ITLB is a small 3-entry, fully associative TLB dedicated to performing translations for the instruction stream. The ITLB only maps 4-Kbyte pages/subpages.

The ITLB is managed by hardware and is transparent to software. The larger JTLB is used as a backing store for the ITLB. If a fetch address cannot be translated by the ITLB, the JTLB is used to attempt to translate it in the following clock cycle. If successful, the translation information is copied into the ITLB for future use. There is a two cycle ITLB miss penalty.

## Data TLB (DTLB)

The DTLB is a small 3-entry, fully associative TLB dedicated to performing translations for loads and stores. The DTLB also only maps 4-Kbyte pages/subpages.

The DTLB is managed by hardware and is transparent to software. The larger JTLB is used as a backing store for the DTLB. The JTLB is looked up in parallel with the DTLB to minimize the DTLB miss penalty. If the JTLB translation is successful, the translation information is copied into the DTLB for future use. There is a one cycle DTLB miss penalty.

#### Virtual-to-Physical Address Translation

Converting a virtual address to a physical address begins by comparing the virtual address from the processor with the virtual addresses in the TLB; there is a match when the virtual page number (VPN) of the address is the same as the VPN field of the entry, and either:

- The Global (G) bit of the TLB entry is set, or

- The ASID field of the virtual address is the same as the ASID field of the TLB entry.

This match is referred to as a TLB *hit*. If there is no match, a TLB *miss* exception is taken by the processor and software is allowed to refill the TLB from a page table of virtual/physical addresses in memory.

Figure 5 shows a flow diagram of the address translation process.

Figure 5 32-bit Virtual Address Translation

The top portion of Figure 5 shows a virtual address for a 4-Kbyte page size. The width of the *Offset* in Figure 5 is defined by the page size. The remaining 20 bits of the address represent the virtual page number (VPN), and index the 1M-entry page table.

The bottom portion of Figure 5 shows the virtual address for a 16-Mbyte page size. The remaining 8 bits of the address represent the VPN, and index the 256-entry page table.

In this figure, the virtual address is extended with an 8-bit address space identifier (ASID), which reduces the frequency of TLB flushing during a context switch. This 8bit ASID contains the number assigned to that process and is stored in the CP0 *EntryHi* register.

#### Hits, Misses, and Multiple Matches

Each JTLB entry contains a tag portion and a data portion. If a match is found, the upper bits of the virtual address are replaced with the page frame number (PFN) stored in the corresponding entry in the data array of the joint TLB (JTLB). The granularity of JTLB mappings is defined in terms of TLB *pages*. The 4Kc core's JTLB supports pages of different sizes ranging from 4 KB to 16 MB in powers of 4.

If no match occurs (TLB miss), an exception is taken and software refills the TLB from the page table resident in memory. Software can write over a selected TLB entry or use a hardware mechanism to write into a random entry.

The 4Kc core implements a TLB write compare mechanism to ensure that multiple TLB matches do not occur. On the TLB write operation, the write value is compared with all other entries in the TLB. If a match occurs, the 4Kc core takes a machine check exception, sets the TS bit in the CP0 *Status* register, and aborts the write operation.

Table 4 shows the address bits used for even/odd bank selection depending on page size and the relationship between the legal values in the mask register and the selected page size.

| Pagemask[24:13] | Page Size | Even/Odd Bank<br>Select Bit |

|-----------------|-----------|-----------------------------|

| 00000000000     | 4KB       | VAddr[12]                   |

| 00000000011     | 16KB      | VAddr[14]                   |

| 00000001111     | 64KB      | VAddr[16]                   |

| Pagemask[24:13] | Page Size | Even/Odd Bank<br>Select Bit |  |

|-----------------|-----------|-----------------------------|--|

| 000000111111    | 256KB     | VAddr[18]                   |  |

| 000011111111    | 1MB       | VAddr[20]                   |  |

| 001111111111    | 4MB       | VAddr[22]                   |  |

Table 4

Mask and Page Size Values (Continued)

#### **TLB Tag and Data Formats**

11111111111111

Figure 6 shows the format of a TLB *tag* entry. The entry is divided into the follow fields:

16MB

VAddr[24]

- Global process indicator

- Address space identifier

- Virtual page number

- Compressed page mask

Setting the global process indicator (G bit) indicates that the entry is global to all processes and/or threads in the system. In this case, the 8-bit ASID value is ignored since the entry is not relative to a specific thread or process.

The address space identifier (ASID) helps to reduce the frequency of TLB flushing on a context switch. The existence of the ASID allows multiple processes to exist in both the TLB and instruction caches. The current ASID value is stored in the *EntryHi* register and is compared to the ASID value of each entry. Figure 6 and Table 5 show the TLB tag entry format.

| G | ASID[7:0] | VPN2[31:25] | VPN2[24:13] | CMASK[5:0] |

|---|-----------|-------------|-------------|------------|

| 1 | 8         | 7           | 12          | 6          |

Figure 6 TLB Tag Entry Format

Table 5TLB Tag Entry Fields

| Field Name | Description                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G          | Global Bit. When set, indicates that this<br>entry is global to all processes and/or threads<br>and thus disables inclusion of the ASID in<br>the comparison. |

| ASID[7:0]  | Address Space Identifier. Identifies with which process or thread this TLB entry is associated.                                                               |

Table 5TLB Tag Entry Fields (Continued)

| Field Name                  | Description                                                                                                                                                                                                                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPN2[31:25],<br>VPN2[24:13] | Virtual Page Number divided by 2. This field<br>contains the upper bits of the virtual page<br>number. Because it represents a pair of TLB<br>pages, it is divided by 2. Bits 31:25 are<br>always included in the TLB lookup<br>comparison. Bits 24:13 are included<br>depending on the page size. |

| CMASK[5:0]                  | Compressed page mask value. This field is a<br>compressed version of the page mask. It<br>defines the page size by masking the<br>appropriate VPN2 bits from being involved<br>comparison. It is also used to determine<br>which address bit is used to make the even-<br>odd page determination.  |

Figure 7 and Table 6 show the TLB data array entry format.

| PFN[31:12] | C[2:0] | D | V |

|------------|--------|---|---|

| 20         | 3      | 1 | 1 |

Figure 7 TLB Data Array Entry Format

Table 6 TLB Data Array Entry Fields

| Field Name |                                                                                                                                                                                           | Description                                                                                                                                                  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PFN[31:12] | Physical Frame Number. Defines the upper<br>bits of the physical address. For page sizes<br>larger than 4KB, only a subset of these bits<br>is actually used.                             |                                                                                                                                                              |  |

| C[2:0]     | Cacheability. Contains an encoded value<br>of the cacheability attributes and<br>determines whether the page should be<br>placed in the cache or not. The field is<br>encoded as follows: |                                                                                                                                                              |  |

|            | CS[2:0] Coherency Attribute                                                                                                                                                               |                                                                                                                                                              |  |

|            | 000*                                                                                                                                                                                      | Maps to entry 011b.                                                                                                                                          |  |

|            | 001*                                                                                                                                                                                      | Maps to entry 011b.                                                                                                                                          |  |

|            | 010                                                                                                                                                                                       | Uncached                                                                                                                                                     |  |

|            | 011                                                                                                                                                                                       | Cacheable, noncoherent,<br>write through, no write<br>allocate                                                                                               |  |

|            | 100*                                                                                                                                                                                      | Maps to entry 011b.                                                                                                                                          |  |

|            | 101*                                                                                                                                                                                      | Maps to entry 011.b                                                                                                                                          |  |

|            | 110*                                                                                                                                                                                      | Maps to entry 011b.                                                                                                                                          |  |

|            | *Values 2<br>mappings<br>reference                                                                                                                                                        | Maps to entry 010b<br>2 and 3 are the required MIPS32<br>s for uncached and cacheable<br>s; other values may have different<br>s in other MIPS32 processors. |  |

#### Table 6 TLB Data Array Entry Fields (Continued)

| Field Name | Description                                                                                                                                                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D          | "Dirty" or write-enable bit. Indicates that<br>the page has been written and/or is<br>writable. If this bit is set, stores to the page<br>are permitted. If the bit is cleared, stores to<br>the page cause a TLB Modified exception. |

| V          | Valid bit. Indicates that the TLB entry, and<br>thus the virtual page mapping, are valid. If<br>this bit is set, accesses to the page are<br>permitted. If the bit is cleared, accesses to<br>the page cause a TLB Invalid exception. |

#### Page Sizes and Replacement Algorithm

To assist in controlling both the amount of mapped space and the replacement characteristics of various memory regions, the 4Kc core provides two mechanisms. First, the page size can be configured, on a per-entry basis, to map a page size of 4 Kbytes to 16 Mbytes (in multiples of 4). The CPO *PageMask* register is loaded with the mapping page size, which is then entered into the TLB when a new entry is written. Thus, operating systems can provide special purpose maps. For example, a typical frame buffer can be memory mapped with only one TLB entry.

The second mechanism controls the replacement algorithm when a TLB miss occurs. To select a TLB entry to be written with a new mapping, the 4Kc core provides a random replacement algorithm. However, the processor also provides a mechanism where a programmable number of mappings can be locked into the TLB via the *Wired* register, thus avoiding random replacement.

## **Cache Controllers**

The 4Kc core instruction and data cache controllers support caches of various sizes, organizations, and set-associativity. For example, the data cache can be 2 Kbytes in size and 2-way set associative, while the instruction cache can be 8 Kbytes in size and 4-way set associative. Each cache can each be accessed in a single processor cycle. In addition, each cache has its own 32-bit data path and both caches can be accessed in the same pipeline clock cycle. Refer to the section entitled "4Kc Core Optional Logic Blocks" on page 12 for more information on instruction and data cache organization.

The cache controllers also have built-in support for replacing one way of the cache with a scratchpad RAM.

See the section entitled "4Kc Core Optional Logic Blocks" on page 12 for more information on scratchpad RAMs.

#### **Bus Interface (BIU)**

The Bus Interface Unit (BIU) controls the external interface signals. Additionally, it contains the implementation of the 32-byte collapsing write buffer. The purpose of this buffer is to store and combine write transactions before issuing them at the external interface. Since the 4Kc core caches follow a write-through cache policy, the write buffer significantly reduces the number of writes transactions on the external interface and reduces the amount of stalling in the core due to issuance of multiple writes in a short period of time.

The write buffer is organized as two 16-byte buffers. Each buffer contains data from a single 16-byte aligned block of memory. One buffer contains the data currently being transferred on the external interface, while the other buffer contains accumulating data from the core. Data from the accumulation buffer is transferred to the external interface buffer under one of these conditions:

- When a store is attempted from the core to a different 16-byte block than is currently being accumulated

- SYNC Instruction

- Store to an invalid merge pattern

- Any load or store to uncached memory

- A load to the line being merged

Note that if the data in the external interface buffer has not been written out to memory, the core is stalled until the memory write completes. After completion of the memory write, accumulated buffer data can be written to the external interface buffer.

#### **Merge Pattern Control**

The 4Kc core implements two 16-byte collapsing write buffers that allow byte, halfword, tri-byte, or word writes from the core to be accumulated in the buffer into a 16-byte value before bursting the data out onto the bus in word format. Note that writes to uncached areas are never merged.

The 4Kc core provides two options for merge pattern control:

- No merge

- Full merge

In *No Merge* mode, writes to a different word within the same line are accumulated in the buffer. Writes to the same word cause the previous word to be driven onto the bus.

In *Full Merge* mode, all combinations of writes to the same line are collected in the buffer. Any pattern of byte enables is possible.

#### SimpleBE Mode

To aid in attaching the 4Kc core to existing busses, there is a mode that only generates "simple" byte enables. Only byte enables representing naturally aligned byte, half, and word transactions will be generated. Legal byte enable patterns are shown in Table 7. Writes with illegal byte enable patterns will be broken into two separate write transactions. This splitting is independent of the merge pattern control in the write buffer. The only case where a read can generate illegal byte enables is on an uncached tribyte load (LWL/LWR). These reads will be converted into a word read on the bus.

Table 7 Valid SimpleBE Byte Enable Patterns

| EB_BE[3:0] |

|------------|

| 0001       |

| 0010       |

| 0100       |

| 1000       |

| 0011       |

| 1100       |

| 1111       |

### 4Kc Core Reset

The 4Kc core has two types of reset input signals: *Reset* and *ColdReset*.

The *ColdReset* signal must be asserted on either a poweron reset or a cold reset. In a typical application, a power-on reset occurs when the machine is first turned on. A cold reset (also called a hard reset) typically occurs when the machine is already on and the system is rebooted. A cold reset completely initializes the internal state machines of the 4Kc core without saving any state information. The *Reset* and *ColdReset* signals work in conjunction with one another to determine the type of reset operation (see Table 8).

| Reset | ColdReset | Action                      |

|-------|-----------|-----------------------------|

| 0     | 0         | Normal Operation, no reset. |

| 1     | 0         | Warm or Soft reset.         |

| X     | 1         | Cold or Hard reset.         |

Table 8 4Kc Reset Types

The *Reset* signal is asserted for a warm reset. A warm reset restarts the 4Kc core and preserves more of the processors internal state than a cold reset. The *Reset* signal can be asserted synchronously or asynchronously during a cold reset, or synchronously to initiate a warm reset. The assertion of *Reset* causes a soft reset exception within the 4Kc core. In debug mode, EJTAG can request that the soft reset function be masked. It is system dependent whether this functionality is supported. In normal mode, the soft reset cannot be masked.

## **Power Management**

The 4Kc core offers a number of power management features, including low-power design, active power management, and power-down modes of operation. The 4Kc core is a static design that supports slowing or halting the clocks, which reduces system power consumption during idle periods.

The 4Kc core provides two mechanisms for system-level low power support:

- Register-controlled power management

- Instruction-controlled power management

### **Register-Controlled Power Management**

The RP bit in the CPO Status register provides a software mechanism for placing the system into a low power state. The state of the RP bit is available externally via the *SI\_RP* signal. The external agent then decides whether to place the device in low power mode, such as by reducing the system clock frequency.

Three additional bits,  $Status_{EXL}$ ,  $Status_{ERL}$ , and  $Debug_{DM}$  support the power management function by allowing the user to change the power state if an exception or error occurs while the 4Kc core is in a low power state. Depending on what type of exception is taken, one of these three bits will be asserted and reflected on the *SI\_EXL*,

*SI\_ERL*, or *EJ\_DebugM* outputs. The external agent can look at these signals and determine whether to leave the low power state to service the exception.

The following 4 power-down signals are part of the system interface and change state as the corresponding bits in the CP0 registers are set or cleared:

- The *SI\_RP* signal represents the state of the RP bit (27) in the CP0 Status register.

- The *SI\_EXL* signal represents the state of the EXL bit (1) in the CPO Status register.

- The *SI\_ERL* signal represents the state of the ERL bit (2) in the CPO Status register.

- The *EJ\_DebugM* signal represents the state of the DM bit (30) in the CP0 Debug register.

### **Instruction-Controlled Power Management**

The second mechanism for invoking power-down mode is through execution of the WAIT instruction. When the WAIT instruction is executed, the internal clock is suspended. However, the internal timer and some of the input pins (*SI\_Int[5:0]*, *SI\_NMI*, *SI\_Reset*, and *SI\_ColdReset*) continue to run. Once the CPU is in instruction-controlled power management mode, any interrupt, NMI, or reset condition causes the CPU to exit this mode and resume normal operation.

The 4Kc core asserts the *SI\_SLEEP* signal, which is part of the system interface bus, whenever the WAIT instruction is executed. The assertion of *SI\_SLEEP* indicates that the clock has stopped and the 4Kc core is waiting for an interrupt.

# 4Kc Core Optional Logic Blocks

The 4Kc core consists of the following optional logic blocks as shown in the block diagram in Figure 1.

## **Instruction Cache**

The instruction cache is an optional on-chip memory block of up to 16 Kbytes. Because the instruction cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access rather than having to wait for the physical address translation. The tag holds 22 bits of physical address, 4 valid bits, a lock bit, and the fill replacement bit. The instruction cache block also contains and manages the instruction line fill buffer. Besides accumulating data to be written to the cache, instruction fetches that reference data in the line fill buffer are serviced either by a bypass of that data, or data coming from the external interface. The instruction cache control logic controls the bypass function.

The core supports instruction-cache locking. Cache locking allows critical code or data segments to be locked into the cache on a "per-line" basis, enabling the system programmer to maximize the efficiency of the system cache.

The cache-locking function is always available on all instruction-cache entries. Entries can then be marked as locked or unlocked on a per entry basis using the CACHE instruction.

## Data Cache

The data cache is an optional on-chip memory block of up to 16 Kbytes. This virtually indexed, physically tagged cache is protected. Because the data cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access. The tag holds 22 bits of physical address, 4 valid bits, a lock bit, and the fill replacement bit.

In addition to instruction-cache locking, the 4Kc core also supports a data-cache locking mechanism identical to the instruction cache. Critical data segments are locked into the cache on a "per-line" basis. The locked contents can be updated on a store hit, but cannot be selected for replacement on a cache miss.

The cache-locking function is always available on all data cache entries. Entries can then be marked as locked or unlocked on a per-entry basis using the CACHE instruction.

## **Cache Memory Configuration**

The 4Kc core incorporates on-chip instruction and data caches that can each be accessed in a single processor cycle. Each cache has its own 32-bit data path and can be accessed in the same pipeline clock cycle. Table 9 lists the 4Kc core instruction and data cache attributes.

| Table 9 | 4Kc Core Inst | ruction and Data | Cache Attributes |

|---------|---------------|------------------|------------------|

|---------|---------------|------------------|------------------|

| Parameter                      | Instruction                  | Data                                        |

|--------------------------------|------------------------------|---------------------------------------------|

| Size                           | 0 - 16 Kbytes                | 0 - 16 Kbytes                               |

| Organization                   | 1 - 4 way set<br>associative | 1 - 4 way set<br>associative                |

| Line Size                      | 16 bytes                     | 16 bytes                                    |

| Read Unit                      | 32 bits                      | 32 bits                                     |

| Write Policy                   | na                           | write-through<br>without write-<br>allocate |

| Miss restart after transfer of | miss word                    | miss word                                   |

| Cache Locking                  | per line                     | per line                                    |

## **Cache Protocols**

The 4Kc core supports the following cache protocols:

- Uncached: Addresses in a memory area indicated as uncached are not read from the cache. Stores to such addresses are written directly to main memory, without changing cache contents.

- Write-through: Loads and instruction fetches first search the cache, reading main memory only if the desired data does not reside in the cache. On data store operations, the cache is first searched to see if the target address is cache resident. If it is resident, the cache contents are updated, and main memory is also written. If the cache look-up misses, only main memory is written.

# Scratchpad RAM

The 4Kc core also supports replacing up to one way of each cache with a scratchpad RAM. The scratchpad RAM is user-defined and can consist of a variety of devices. The main requirement is that it must be accessible with timing similar to a regular cache RAM. This means that an index will be driven one cycle, a tag will be driven the following clock, and the scratchpad must return a hit signal and the data in the second clock. The scratchpad can thus easily contain a large RAM/ROM or memory-mapped registers.

The core's interface to a scratchpad RAM is slightly different than to a regular cache RAM. Additional index bits allow access to a larger array, 1MB of scratchpad RAM versus 4KB for a cache way. These bits come from the virtual address, so on a 4Kc core care must be taken to avoid virtual aliasing. The core does not automatically refill the scratchpad way and will not select it for replacement on cache misses. Additionally, stores that hit in the scratchpad will not generate write-throughs to main memory.

## **EJTAG Debug Support**

The 4Kc core provides for an optional Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard user mode and kernel modes of operation, the 4Kc core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a debug exception return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

Refer to the section called "4Kc Core Signal Descriptions" on page 19 for a list of signals EJTAG interface signals.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the 4Kc core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define what registers are selected and how they are used.

#### **Debug Registers**

Three debug registers (DEBUG, DEPC, and DESAVE) have been added to the MIPS Coprocessor 0 (CP0) register set. The DEBUG register shows the cause of the debug exception and is used for the setting up of single-step operations. The DEPC, or Debug Exception Program Counter, register holds the address on which the debug exception was taken. This is used to resume program execution after the debug operation finishes. Finally, the DESAVE, or Debug Exception Save, register enables the saving of general-purpose registers used during execution of the debug exception handler. To exit debug mode, a Debug Exception Return (DERET) instruction is executed. When this instruction is executed, the system exits debug mode, allowing normal execution of application and system code to resume.

#### **EJTAG Hardware Breakpoints**

There are several types of simple hardware breakpoints defined in the EJTAG specification. These stop the normal operation of the CPU and force the system into debug mode. There are two types of simple hardware breakpoints implemented in the 4Kc core: Instruction breakpoints and Data breakpoints.

The 4Kc core can be configured with the following breakpoint options:

- No data or instruction breakpoints

- One data and two instruction breakpoints

- Two data and four instruction breakpoints

Instruction breaks occur on instruction fetch operations, and the break is set on the virtual address on the bus between the CPU and the instruction cache. Instruction breaks can also be made on the ASID value used by the MMU. Finally, a mask can be applied to the virtual address to set breakpoints on a range of instructions.

Data breakpoints occur on load/store transactions. Breakpoints are set on virtual address and ASID values, similar to the Instruction breakpoint. Data breakpoints can be set on a load, a store, or both. Data breakpoints can also be set based on the value of the load/store operation. Finally, masks can be applied to both the virtual address and the load/store value.

# **4Kc Core Instructions**

The 4Kc core instruction set complies with the MIPS32 instruction set architecture. Table 10 provides a summary of instructions implemented by the 4Kc core.

| Table | 10 | 4Kc | Core | Instruction | Set |

|-------|----|-----|------|-------------|-----|

|-------|----|-----|------|-------------|-----|

| Instruction | Description                                                 | Function     |

|-------------|-------------------------------------------------------------|--------------|

| ADD         | Integer Add                                                 | Rd = Rs + Rt |

| ADDI        | Integer Add Immediate Rt = Rs + Immed                       |              |

| ADDIU       | Unsigned Integer Add Immediate Rt = Rs + <sub>U</sub> Immed |              |

| ADDU        | Unsigned Integer Add $Rd = Rs +_U Rt$                       |              |

| Instruction | Description                                                | Function                                                                                    |  |  |

|-------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| AND         | Logical AND                                                | Rd = Rs & Rt                                                                                |  |  |

| ANDI        | Logical AND Immediate                                      | Rt = Rs & $(0_{16}    \text{ Immed})$                                                       |  |  |

| BEQ         | Branch On Equal                                            | if Rs == Rt<br>PC += (int)offset                                                            |  |  |

| BEQL        | Branch On Equal Likely                                     | if Rs == Rt<br>PC += (int)offset<br>else<br>Ignore Next Instruction                         |  |  |

| BGEZ        | Branch on Greater Than or Equal To Zero                    | if !Rs[31]<br>PC += (int)offset                                                             |  |  |

| BGEZAL      | Branch on Greater Than or Equal To Zero And<br>Link        | GPR[31] = PC + 8<br>if !Rs[31]<br>PC += (int)offset                                         |  |  |

| BGEZALL     | Branch on Greater Than or Equal To Zero And<br>Link Likely | <pre>GPR[31] = PC + 8 if !Rs[31] PC += (int)offset else Ignore Next Instruction</pre>       |  |  |

| BGEZL       | Branch on Greater Than or Equal To Zero<br>Likely          | if !Rs[31]<br>PC += (int)offset<br>else<br>Ignore Next Instruction                          |  |  |

| BGTZ        | Branch on Greater Than Zero                                | if !Rs[31] && Rs != 0<br>PC += (int)offset                                                  |  |  |

| BGTZL       | Branch on Greater Than Zero Likely                         | <pre>if !Rs[31] &amp;&amp; Rs != 0   PC += (int)offset else   Ignore Next Instruction</pre> |  |  |

| BLEZ        | Branch on Less Than or Equal to Zero                       | if Rs[31]    Rs == 0<br>PC += (int)offset                                                   |  |  |

| BLEZL       | Branch on Less Than or Equal to Zero Likely                | <pre>if Rs[31]    Rs == 0 PC += (int)offset else Ignore Next Instruction</pre>              |  |  |

| BLTZ        | Branch on Less Than Zero                                   | if Rs[31]<br>PC += (int)offset                                                              |  |  |

| BLTZAL      | Branch on Less Than Zero And Link                          | <pre>GPR[31] = PC + 8 if Rs[31]     PC += (int)offset</pre>                                 |  |  |

| BLTZALL     | Branch on Less Than Zero And Link Likely                   | <pre>GPR[31] = PC + 8 if Rs[31]   PC += (int)offset else   Ignore Next Instruction</pre>    |  |  |

| BLTZL       | Branch on Less Than Zero Likely                            | if Rs[31]<br>PC += (int)offset<br>else<br>Ignore Next Instruction                           |  |  |

#### Table 104Kc Core Instruction Set (Continued)

| Instruction | Description                                                                        | Function                                                                                       |  |

|-------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| BNE         | Branch on Not Equal                                                                | if Rs != Rt<br>PC += (int)offset                                                               |  |

| BNEL        | Branch on Not Equal Likely<br>PC += (int)offset<br>else<br>Ignore Next Instruction |                                                                                                |  |

| BREAK       | Breakpoint                                                                         | Break Exception                                                                                |  |

| CACHE       | Cache Operation                                                                    | See Software User's Manual                                                                     |  |

| COP0        | Coprocessor 0 Operation                                                            | See Software User's Manual                                                                     |  |

| CLO         | Count Leading Ones                                                                 | Rd = NumLeadingOnes(Rs)                                                                        |  |

| CLZ         | Count Leading Zeroes                                                               | Rd = NumLeadingZeroes(Rs)                                                                      |  |

| DERET       | Return from Debug Exception                                                        | PC = DEPC<br>Exit Debug Mode                                                                   |  |

| DIV         | Divide                                                                             | LO = (int)Rs / (int)Rt<br>HI = (int)Rs % (int)Rt                                               |  |

| DIVU        | Unsigned Divide                                                                    | LO = (uns)Rs / (uns)Rt<br>HI = (uns)Rs % (uns)Rt                                               |  |

| ERET        | Return from Exception                                                              | <pre>if SR[2]     PC = ErrorEPC else     PC = EPC     SR[1] = 0     SR[2] = 0     LL = 0</pre> |  |

| J           | Unconditional Jump                                                                 | PC = PC[31:28]    offset<<2                                                                    |  |

| JAL         | Jump and Link                                                                      | GPR[31] = PC + 8<br>PC = PC[31:28]    offset<<2                                                |  |

| JALR        | Jump and Link Register                                                             | Rd = PC + 8<br>PC = Rs                                                                         |  |

| JR          | Jump Register                                                                      | PC = Rs                                                                                        |  |

| LB          | Load Byte                                                                          | <pre>Rt = (byte)Mem[Rs+offset]</pre>                                                           |  |

| LBU         | Unsigned Load Byte                                                                 | Rt = (ubyte))Mem[Rs+offset]                                                                    |  |

| LH          | Load Halfword                                                                      | Rt = (half)Mem[Rs+offset]                                                                      |  |

| LHU         | Unsigned Load Halfword                                                             | Rt = (uhalf)Mem[Rs+offset]                                                                     |  |

| LL          | Load Linked Word                                                                   | Rt = Mem[Rs+offset]<br>LL = 1<br>LLAdr = Rs + offset                                           |  |

| LUI         | Load Upper Immediate                                                               | Rt = immediate << 16                                                                           |  |

| LW          | Load Word                                                                          | Rt = Mem[Rs+offset]                                                                            |  |

| LWL         | Load Word Left                                                                     | See Software User's Manual                                                                     |  |

| Table | 10 | 4Kc Core | Instruction | Set | (Continued) |

|-------|----|----------|-------------|-----|-------------|

|-------|----|----------|-------------|-----|-------------|

| Instruction | Description                                | Function                                                             |  |

|-------------|--------------------------------------------|----------------------------------------------------------------------|--|

| LWR         | Load Word Right See Software User's Manual |                                                                      |  |

| MADD        | Multiply-Add                               | HI   LO += (int)Rs * (int)Rt                                         |  |

| MADDU       | Multiply-Add Unsigned                      | HI   LO += (uns)Rs * (uns)Rt                                         |  |

| MFC0        | Move From Coprocessor 0                    | Rt = CPR[0, n, sel] = Rt                                             |  |

| MFHI        | Move From HI                               | Rd = HI                                                              |  |

| MFLO        | Move From LO                               | Rd = LO                                                              |  |

| MOVN        | Move Conditional on Not Zero               | if $Rt \neq 0$ then<br>Rd = Rs                                       |  |

| MOVZ        | Move Conditional on Zero                   | if Rt = 0 then<br>Rd = Rs                                            |  |

| MSUB        | Multiply-Subtract                          | HI   LO -= (int)Rs * (int)Rt                                         |  |

| MSUBU       | Multiply-Subtract Unsigned                 | HI   LO -= (uns)Rs * (uns)Rt                                         |  |

| MTC0        | Move To Coprocessor 0                      | CPR[0, n, SEL] = Rt                                                  |  |

| MTHI        | Move To HI                                 | HI = Rs                                                              |  |

| MTLO        | Move To LO                                 | LO = Rs                                                              |  |

| MUL         | Multiply with register write               | HI   LO =Unpredictable<br>Rd = ((int)Rs *<br>(int)Rt) <sub>310</sub> |  |

| MULT        | Integer Multiply                           | HI   LO = (int)Rs * (int)Rd                                          |  |

| MULTU       | Unsigned Multiply                          | HI   LO = (uns)Rs * (uns)Rd                                          |  |

| NOR         | Logical NOR                                | Rd = ~(Rs   Rt)                                                      |  |

| OR          | Logical OR                                 | Rd = Rs   Rt                                                         |  |

| ORI         | Logical OR Immediate                       | Rt = Rs   Immed                                                      |  |

| PREF        | Prefetch                                   | Load Specified Line into Cache                                       |  |

| SB          | Store Byte                                 | (byte)Mem[Rs+offset] = Rt                                            |  |

| SC          | Store Conditional Word                     | <pre>if LL = 1     mem[Rs+offset] = Rt Rt = LL</pre>                 |  |

| SDBBP       | Software Debug Break Point                 | Trap to SW Debug Handler                                             |  |

| SH          | Store Half                                 | (half)Mem[Rs+offset] = Rt                                            |  |

| SLL         | Shift Left Logical                         | Rd = Rt << sa                                                        |  |

| SLLV        | Shift Left Logical Variable                | Rd = Rt << Rs[4:0]                                                   |  |

| SLT         | Set on Less Than                           | <pre>if (int)Rs &lt; (int)Rt    Rd = 1 else    Rd = 0</pre>          |  |

Table 104Kc Core Instruction Set (Continued)

| Instruction | Description                                         | Function                                                         |  |

|-------------|-----------------------------------------------------|------------------------------------------------------------------|--|

| SLTI        | Set on Less Than Immediate                          | <pre>if (int)Rs &lt; (int)Immed     Rt = 1 else     Rt = 0</pre> |  |

| SLTIU       | Set on Less Than Immediate Unsigned                 | <pre>if (uns)Rs &lt; (uns)Immed     Rt = 1 else     Rt = 0</pre> |  |

| SLTU        | Set on Less Than Unsigned                           | <pre>if (uns)Rs &lt; (uns)Immed   Rd = 1 else   Rd = 0</pre>     |  |

| SRA         | Shift Right Arithmetic                              | Rd = (int)Rt >> sa                                               |  |

| SRAV        | Shift Right Arithmetic Variable                     | Rd = (int)Rt >> Rs[4:0]                                          |  |

| SRL         | Shift Right Logical                                 | Rd = (uns)Rt >> sa                                               |  |

| SRLV        | Shift Right Logical Variable                        | Rd = (uns)Rt >> Rs[4:0]                                          |  |

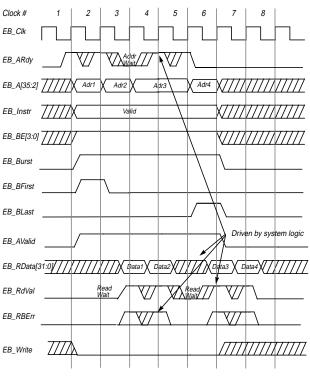

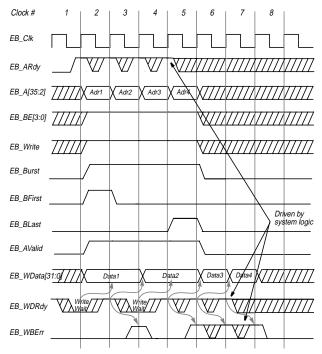

| SSNOP       | Superscalar Inhibit No Operation                    | NOP                                                              |  |