# Fx<sup>™</sup>100100S-5, Fx10050S-5 Chipsets

For Customer Premises Equipment

# **Target Markets**

- Multi-tenant and Multi-dwelling units (MxU)

- Fiber to the Basement/Building (FTTB)

- Fiber to the Node (FTTN)

- Fiber to the Curb (FTTC)

- Fiber to the Premise (FTTP)

- Fiber to the Home (FTTH)

### **Applications**

- Fiber-fast Broadband, Peer to Peer

- Networking, Online Gaming/Hosting

- Triple play services

- IPTV (HDTV and SDTV)

- Voice over IP

- High-resolution Video Conferencing

## Solutions for High-Performance Modems, Routers, and Gateways

- Single-port data pump DSP Engine

- Single-port IFE

- Single-port LD

- iPOS firmware and API

#### **Development Tools**

- Evaluation Systems

- Reference Designs

- Application Notes

- Complete Software Suite

- Bill of Materials (BOM)

The Fx<sup>™</sup>100100S-5 and Fx10050S-5 chipsets are the industry's first IPTV-optimized VDSL2 and VDSL products for CPE modems and other subscriber located equipment. Both chipsets support all 8, 12 and 17 MHz profiles. The Fx100100S-5 chipset additionally supports the 30 MHz profile. The chipsets also support the VDSL standard.

The Fx100100S-5 and Fx10050S-5 chipsets have a rich feature set for IPTV and triple play. These include: on-chip classification, queuing and scheduling for enhanced Quality of service (QoS) in IPv4 and IPv6 networks, enhanced impulse noise protection, and dual latency and dual interleaving over all network interfaces.

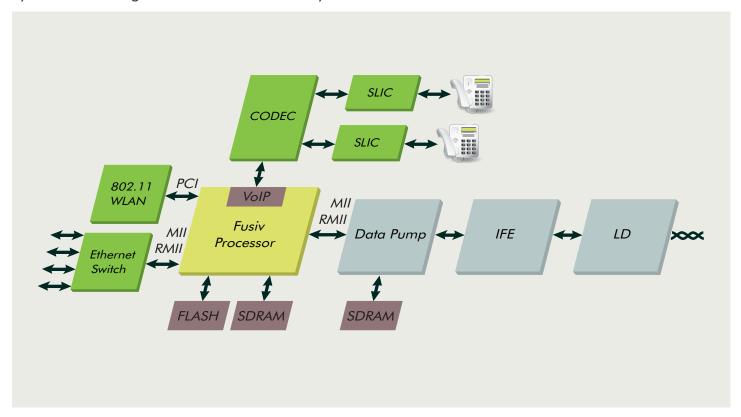

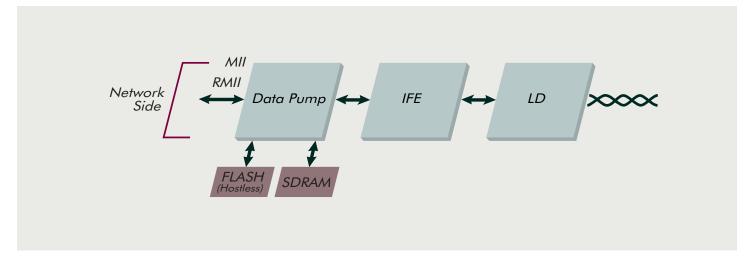

Common attributes of both chipsets include: the industry's highest performance, plugand-play multi-mode operation, VDSL long range (VLR) capability with programmable U0, full band plan configurability for worldwide applications and interoperability with deployed central office (CO) equipment.The industry-standard xMII interfaces enable the chipsets to be used directly with external PHY chips for costeffective, standalone, host-less operation. In gateway and router applications, a communication processor can connect to the chipsets via the xMII or Utopia interfaces. Both chipsets are 100% pin compatible, which allows system vendors to develop a single CPE platform for worldwide deployment and reduces their development costs and time to market.

Both chipsets consist of a single-chip data pump (DSP engine) with the modem functionality and network interfaces, an Integrated Front End (IFE) with converters, amplifiers and filters, a line driver with programmable 8.5 - 14.5 dBm drive and the Ikanos Programmable Operating System™ (iPOS).

The iPOS consists of firmware and an OS-independent application programming interface (API) that enables easy integration into existing management software.

The Fx100100S-5 and Fx10050S-5 chipsets enable equipment vendors to develop a single system to deliver a full suite of revenue-generating interactive broadband services. The highly integrated architecture enables the design of smaller, simpler systems with fewer components and higher port density. Carriers can now achieve their goal of delivering universal service at 100 Mbps while simultaneously future-proofing their networks.

# New York System Block Diagram – Residential Gateway

# Nostem Block Diagram – Hostless Modem

### **Key Features**

- Supports VDSL2 profiles

- Fx100100S-5 supports 8a/8b/8c/8d, 12a/12b, 17a and 30a

- Fx10050S-5 supports 8a/8b/8c/8d, 12a/12b and 17a

- Plug and play VDSL2 and VDSL operation

- · Feature set optimized for triple play and

- IPTV including:

- Available on-chip classification, queuing and scheduling for enhanced Quality of Service (QoS) for IPv4 and IPv6 networks

- Support for Dual Latency, Dual Interleaving over xMII and Utopia interfaces for interworking with low cost 10/100 Ethernet PHY and highperformance communication processors

- Maximum interleaver and de-interleaver memory for Impulse Noise Protection (INP)

- Eraser detection and decoding for enhanced Impulse Noise Protection

- Universal CPE design for IP or ATM networks

- Available integrated AAL5 SAR for ATM termination

- Single worldwide platform for both short and long range applications

- Interoperable with deployed CO equipment

- Highly-integrated chipset consists of the following:

- Data pump (DSP Engine) a single chip data pump that integrates a framer, deframer, FFT/IFFT engines, interleaver/ de-interleaver memory and network interfaces. An embedded 200 MIPS processor performs control-plane and management functions. The Data pump is available in different versions to support different levels of QoS

- Integrated Front End (IFE) with on-chip ADC/DAC, amplifiers and filters

- High-drive Line Driver (HLD) with integrated Low Noise Amplifier (LNA) supports programmable drive levels from 8.5 – 14.5 dBm

- iPOS consists of firmware and OSindependent APIs that enable easy integration into existing management software

- Standards-compliant DMT line coding ensures spectral compatibility with POTS, ISDN, and DSL services per T1.417 standard

- Region-specific RFI notching

- IEEE 1149.1 compliant JTAG interface

- Industrial temperature range (-40 °C to +85 °C)

© 2009 Ikanos Communications, Inc. All Rights Reserved. Ikanos Communications, Ikanos, the Ikanos logo, the "Bandwidth without boundaries" tagline, Fusiv, Fx, FxS, iQV and Ikanos Accelity, Ikanos Capri, Ikanos ISOS, Ikanos Maxtane, Ikanos Orion, Ikanos Solos, Ikanos Velocity, Ikanos Vulcan are among the trademarks or registered trademarks of Ikanos Communications. All other trademarks mentioned herein are properties of their respective holders. This information is protected by copyright and distributed under licenses restricting, without limitation, its use, reproduction, copying, distribution, and de-compilation. No part of this information may be reproduced in any form by any means electronic, mechanical, magnetic, optical, manual, or otherwise, without prior written authorization of an authorized officer of Ikanos Communications, Inc (Ikanos).

#### Disclaimer

This information is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Ikanos. Ikanos assumes no responsibility or liability for any errors or inaccuracies that may appear in this material. Ikanos makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. References in this document to an industry or technology standard should not be interpreted as a warranty that the product or feature described complies with all aspects of that standard. In addition, standards compliance and the availability of certain features will vary according to software release version. For further information regarding the standards compliance of a particular software release, and the features included in that release, refer to the release notes for that product.

Ikanos reserves the right to revise the design and associated documentation and to make changes from time to time in the content of this document without obligation of Ikanos to notify any person of such revisions or changes. Use of this document does not convey or imply any license under patent or other rights. Ikanos does not authorize the use of its products in life-support systems where a malfunction or failure may result in injury to the user. A manufacturer that uses Ikanos products in life-support applications assumes all the risks of doing so and indemnifies Ikanos against all charges.

For more information, contact Ikanos.

Ikanos Communications, Inc. 47669 Fremont Boulevard Fremont, California 94538

www.ikanos.com

P +1 510.979.0400

F +1 510.979.0500

E sales@ikanos.com