## SCHOOL OF DESIGN, ENGINEERING & COMPUTING

BSc (Hons) Computing

BSc (Hons) Software Engineering Management

ARM: ASSEMBLY LANGUAGE PROGRAMMING

PETER KNAGGS

AND

STEPHEN WELSH

August 31, 2004

# Contents

| Co  | $\mathbf{nten}$ | ats                                         | i               |

|-----|-----------------|---------------------------------------------|-----------------|

| Lis | st of           | Programs                                    | vii             |

| Pr  | eface           |                                             | ix              |

| 1   | Intr            | oduction                                    | 1               |

|     | 1.1             | The Meaning of Instructions                 | 1               |

|     |                 | 1.1.1 Binary Instructions                   | 1               |

|     | 1.2             | A Computer Program                          | 1               |

|     | 1.3             | The Binary Programming Problem              | 2               |

|     | 1.4             | Using Octal or Hexadecimal                  | 2               |

|     | 1.5             | Instruction Code Mnemonics                  | 3               |

|     | 1.6             | The Assembler Program                       | 4               |

|     |                 | 1.6.1 Additional Features of Assemblers     | 4               |

|     |                 | 1.6.2 Choosing an Assembler                 | 5               |

|     | 1.7             | Disadvantages of Assembly Language          | 5               |

|     | 1.8             | High-Level Languages                        | 6               |

|     |                 | 1.8.1 Advantages of High-Level Languages    | 6               |

|     |                 | 1.8.2 Disadvantages of High-Level Languages | 7               |

|     | 1.9             | Which Level Should You Use?                 | 8               |

|     |                 | 1.9.1 Applications for Machine Language     | 8               |

|     |                 | 1.9.2 Applications for Assembly Language    | 8               |

|     |                 | 1.9.3 Applications for High-Level Language  | 8               |

|     |                 | 1.9.4 Other Considerations                  | 8               |

|     | 1.10            | Why Learn Assembler?                        | 8               |

| 2   | Asse            | emblers                                     | 11              |

| _   | 2.1             | Fields                                      | 11              |

|     |                 | 2.1.1 Delimiters                            | 11              |

|     |                 | 2.1.2 Labels                                | 12              |

|     | 2.2             | Operation Codes (Mnemonics)                 | 14              |

|     | 2.3             | Directives                                  | 14              |

|     | 2.0             | 2.3.1 The DEFINE CONSTANT (Data) Directive  | 14              |

|     |                 | 2.3.2 The EQUATE Directive                  | 15              |

|     |                 | 2.3.3 The AREA Directive                    | 16              |

|     |                 | 2.3.4 Housekeeping Directives               | 17              |

|     |                 | 2.3.5 When to Use Labels                    | $\frac{17}{17}$ |

|     | 2.4             | Operands and Addresses                      | $\frac{17}{17}$ |

|     | 2.4             | 2.4.1 Decimal Numbers                       | 18              |

|     |                 | 2.4.1 Decimal Numbers                       | 18              |

|     |                 | 2.4.2 Other Number Systems                  | 18              |

|     |                 | 2.4.5 Names                                 | 10              |

ii CONTENTS

|   |                | $2.4.5 \\ 2.4.6$ | Arithmetic and Logical Expression General Recommendations                                                     |   |   |       | <br>  |   |       |   |       |   |       |   |   | 18<br>19        |

|---|----------------|------------------|---------------------------------------------------------------------------------------------------------------|---|---|-------|-------|---|-------|---|-------|---|-------|---|---|-----------------|

|   | 2.5            |                  | ${ m ents}$                                                                                                   |   |   |       |       |   |       |   |       |   |       |   |   | 19              |

|   | 2.6            | Types            | of Assemblers                                                                                                 |   |   | <br>  |       |   |       |   |       |   |       |   |   | 20              |

|   | 2.7            | Errors           |                                                                                                               |   |   |       | <br>  |   |       |   |       |   |       |   |   | 20              |

|   | 2.8            | Loader           | s                                                                                                             |   |   |       | <br>  |   |       |   |       |   |       |   |   | 21              |

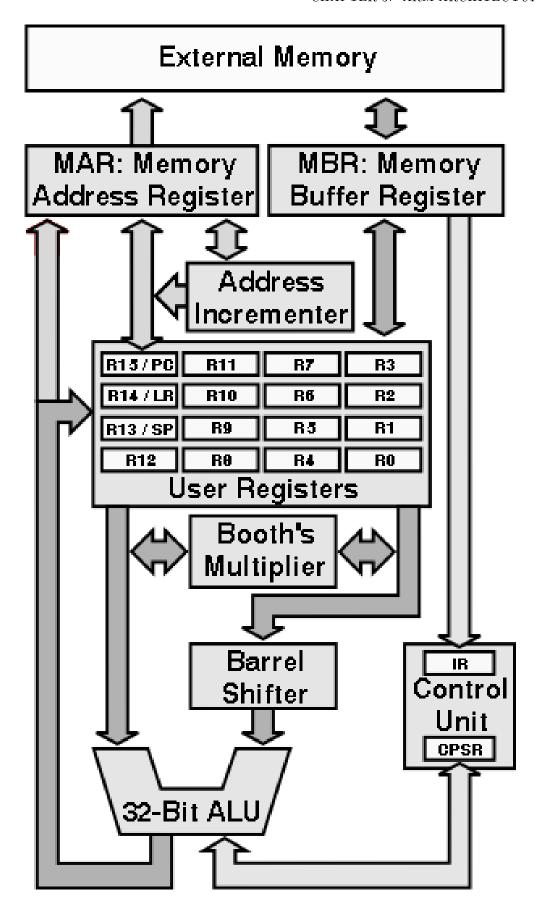

| 3 | $\mathbf{AR}$  | M Arc            | hitecture                                                                                                     |   |   |       |       |   |       |   |       |   |       |   |   | 23              |

|   | 3.1            | Proces           | $\operatorname{sor} \operatorname{modes} \dots \dots \dots \dots \dots$                                       |   |   |       |       |   |       |   |       |   |       |   |   | 23              |

|   | 3.2            | Regist           | ${ m ers}$                                                                                                    |   |   |       | <br>  |   |       |   |       |   |       |   |   | 25              |

|   |                | 3.2.1            | The stack pointer, SP or R13                                                                                  |   |   |       | <br>  |   |       |   |       |   |       |   |   | 26              |

|   |                | 3.2.2            | The Link Register, LR or R14                                                                                  |   |   |       | <br>  |   |       |   |       |   |       |   |   | 27              |

|   |                | 3.2.3            | The program counter, PC or R15.                                                                               |   |   |       | <br>  |   |       |   |       |   |       |   |   | 27              |

|   |                | 3.2.4            | Current Processor Status Registers                                                                            |   |   |       |       |   |       |   |       |   |       |   |   | 28              |

|   | 3.3            |                  |                                                                                                               |   |   |       |       |   |       |   |       |   |       |   |   | 28              |

|   | 3.4            | _                | ions                                                                                                          |   |   |       |       |   |       |   |       |   |       |   |   | 29              |

|   | 3.5            | -                | etion Set                                                                                                     |   |   |       |       |   |       |   |       |   |       |   |   | 30              |

|   | 0.0            | 3.5.1            | Conditional Execution: $\langle cc \rangle$                                                                   |   |   |       |       |   |       |   |       |   |       |   |   | 31              |

|   |                | 3.5.1            | Data Processing Operands: $\langle op1 \rangle$                                                               |   |   |       |       |   |       |   |       |   |       |   |   | 32              |

|   |                | 3.5.2            | = ' '                                                                                                         |   |   |       |       |   |       |   |       |   |       |   |   | $\frac{32}{34}$ |

|   |                | 5.5.5            | Memory Access Operands: $\langle op2 \rangle$ .                                                               | • | • | <br>· | <br>• | • | <br>į | • | <br>• | · | <br>• | ٠ | • | 34              |

| 4 | Inst           | ruction          |                                                                                                               |   |   |       |       |   |       |   |       |   |       |   |   | 37              |

|   |                | 4.0.4            | Branch instructions                                                                                           |   |   |       |       |   |       |   |       |   |       |   |   | 38              |

|   |                | 4.0.5            | Data-processing instructions                                                                                  |   |   |       |       |   |       |   |       |   |       |   |   | 38              |

|   |                | 4.0.6            | Status register transfer instructions                                                                         |   |   |       |       |   |       |   |       |   |       |   |   | 39              |

|   |                | 4.0.7            | Load and store instructions                                                                                   |   |   |       |       |   |       |   |       |   |       |   |   | 40              |

|   |                | 4.0.8            | Coprocessor instructions                                                                                      |   |   |       |       |   |       |   |       |   |       |   |   | 41              |

|   |                | 4.0.9            | Exception-generating instructions $\boldsymbol{.}$                                                            |   |   |       |       |   |       |   |       |   |       |   |   | 41              |

|   |                | 4.0.10           | Conditional Execution: $\langle cc \rangle$                                                                   | • |   | <br>٠ |       |   | <br>٠ | ٠ | <br>٠ | • | <br>٠ | ٠ | ٠ | 42              |

| 5 | $\mathbf{Add}$ |                  | g Modes                                                                                                       |   |   |       |       |   |       |   |       |   |       |   |   | <b>45</b>       |

|   | 5.1            | Data I           | Processing Operands: $\langle op1 \rangle$                                                                    |   |   |       | <br>  |   |       |   |       |   |       |   |   | 45              |

|   |                | 5.1.1            | Unmodified Value                                                                                              |   |   |       | <br>  |   |       |   |       |   |       |   |   | 45              |

|   |                | 5.1.2            | Logical Shift Left                                                                                            |   |   | <br>  | <br>  |   |       |   |       |   |       |   |   | 45              |

|   |                | 5.1.3            | Logical Shift Right                                                                                           |   |   |       |       |   |       |   |       |   |       |   |   | 46              |

|   |                | 5.1.4            | Arithmetic Shift Right                                                                                        |   |   |       |       |   |       |   |       |   |       |   |   | 46              |

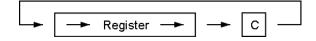

|   |                | 5.1.5            | Rotate Right                                                                                                  |   |   |       |       |   |       |   |       |   |       |   |   | 46              |

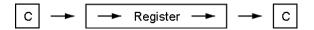

|   |                | 5.1.6            | Rotate Right Extended                                                                                         |   |   | <br>  |       |   |       |   |       |   |       |   |   | 47              |

|   | 5.2            | Memo             | $\operatorname{Cy} \operatorname{Access} \operatorname{Operands}: \langle \mathit{op2} \rangle \ldots \ldots$ |   |   |       |       |   |       |   |       |   |       |   |   | 47              |

|   |                | 5.2.1            | Offset Addressing                                                                                             |   |   |       |       |   |       |   |       |   |       |   |   | 48              |

|   |                | 5.2.2            | Pre-Index Addressing                                                                                          |   |   |       |       |   |       |   |       |   |       |   |   | 49              |

|   |                | 5.2.3            | Post-Index Addressing                                                                                         |   |   |       |       |   |       |   |       |   |       |   |   | 49              |

| c | D              |                  | -                                                                                                             |   |   |       |       |   |       |   |       |   |       |   |   | <b>P</b> 4      |

| 6 | 6.1            | grams<br>Evanu   | ole Programs                                                                                                  |   |   |       |       |   |       |   |       |   |       |   |   | <b>51</b> 51    |

|   | 0.1            |                  |                                                                                                               |   |   |       |       |   |       |   |       |   |       |   |   |                 |

|   |                | 6.1.1            | Program Listing Format                                                                                        |   |   |       |       |   |       |   |       |   |       |   |   | 51              |

|   | 6.0            | 6.1.2            | Guidelines for Examples                                                                                       |   |   |       |       |   |       |   |       |   |       |   |   | 51              |

|   | 6.2            |                  | the examples                                                                                                  |   |   |       |       |   |       |   |       |   |       |   |   | 52              |

|   | 6.3            |                  | the examples from the command li                                                                              |   |   |       |       |   |       |   |       |   |       |   |   | 53              |

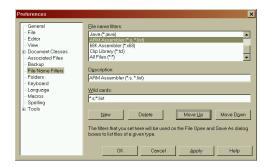

|   | _              | 6.3.1            | Setting up TextPad                                                                                            |   |   |       |       |   |       |   |       |   |       |   |   | 54              |

|   | 6.4            | _                | m Initialization                                                                                              |   |   |       |       |   |       |   |       |   |       |   |   | 55              |

|   | 6.5            |                  | Conditions                                                                                                    |   |   |       |       |   |       |   |       |   |       |   |   | 55              |

|   | 6.6            | Proble           | ${ m ms}$                                                                                                     |   |   |       | <br>  |   |       |   |       |   |       |   |   | 55              |

*CONTENTS* iii

| 7  | Data        | a Mov              | ement                                          | 57         |

|----|-------------|--------------------|------------------------------------------------|------------|

|    | 7.1         | Progra             | m Examples                                     | 57         |

|    |             | 7.1.1              | 16-Bit Data Transfer                           | 57         |

|    |             | 7.1.2              | One's Complement                               | 58         |

|    |             | 7.1.3              | 32-Bit Addition                                | 59         |

|    |             | 7.1.4              | Shift Left One Bit                             | 60         |

|    |             | 7.1.5              | Byte Disassembly                               | 61         |

|    |             | 7.1.6              | Find Larger of Two Numbers                     | 62         |

|    |             | 7.1.7              | 64-Bit Adition                                 | 63         |

|    |             | 7.1.8              | Table of Factorials                            | 64         |

|    | 7.2         | Proble             |                                                | 65         |

|    | 1.2         | 7.2.1              | 64-Bit Data Transfer                           | 65         |

|    |             | 7.2.1 $7.2.2$      | 32-Bit Subtraction                             | 65         |

|    |             | 7.2.2              |                                                | 65         |

|    |             |                    | Shift Right Three Bits                         |            |

|    |             | 7.2.4              | Halfword Assembly                              | 66         |

|    |             | 7.2.5              | Find Smallest of Three Numbers                 | 66         |

|    |             | 7.2.6              | Sum of Squares                                 | 66         |

|    |             | 7.2.7              | Shift Left $n$ bits                            | 66         |

| 0  | <b>.</b>    | •                  |                                                | 00         |

| 8  | Logi        | ıc                 |                                                | 69         |

| 9  | Prog        | gram I             | Loops                                          | 71         |

|    | 9.1         | Progra             | m Examples                                     | 72         |

|    |             | $9.1.\overline{1}$ | Sum of numbers                                 | 72         |

|    |             | 9.1.2              | Number of negative elements                    | 73         |

|    |             | 9.1.3              | Find Maximum Value                             | 75         |

|    |             | 9.1.4              | Normalize A Binary Number                      | 75         |

|    | 9.2         | Proble             | ·                                              | 76         |

|    | 0. <u>-</u> | 9.2.1              | Checksum of data                               | 76         |

|    |             | 9.2.2              | Number of Zero, Positive, and Negative numbers | 77         |

|    |             | 9.2.3              | Find Minimum                                   | 77         |

|    |             | 9.2.4              | Count 1 Bits                                   | 77         |

|    |             | 9.2.4              | Find element with most 1 bits                  | 77         |

|    |             | 9.4.0              | Tind element with most 1 bits                  | ' '        |

| 10 | Stri        | _                  |                                                | <b>7</b> 9 |

|    |             |                    | ng data in ASCII                               |            |

|    | 10.2        | A strin            | ng of characters                               | 80         |

|    |             | 10.2.1             | Fixed Length Strings                           | 81         |

|    |             | 10.2.2             | Terminated Strings                             | 81         |

|    |             | 10.2.3             | Counted Strings                                | 82         |

|    | 10.3        | Interna            | ational Characters                             | 82         |

|    | 10.4        | Progra             | m Examples                                     | 82         |

|    |             | 10.4.1             | Length of a String of Characters               | 82         |

|    |             | 10.4.2             | Find First Non-Blank Character                 | 84         |

|    |             |                    | Replace Leading Zeros with Blanks              | 84         |

|    |             |                    | Add Even Parity to ASCII Chatacters            | 85         |

|    |             |                    | Pattern Match                                  | 86         |

|    | 10.5        | Proble             |                                                | 88         |

|    | 20.0        |                    | Length of a Teletypewriter Message             | 88         |

|    |             |                    | Find Last Non-Blank Character                  | 88         |

|    |             |                    | Truncate Decimal String to Integer Form        | 88         |

|    |             |                    | Check Even Parity and ASCII Characters         | 89         |

|    |             |                    |                                                | 89         |

|    |             | 10.0.0             | String Comparison                              | 09         |

iv CONTENTS

| 11        | $\mathbf{Cod}$ | e Con            | version                                      | 91  |

|-----------|----------------|------------------|----------------------------------------------|-----|

|           | 11.1           | Progra           | m Examples                                   | 91  |

|           |                | 11.1.1           | Hexadecimal to ASCII                         | 91  |

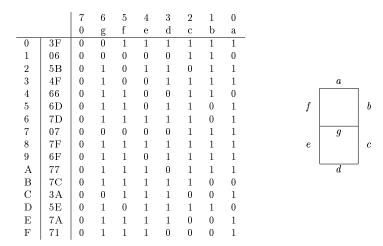

|           |                | 11.1.2           | Decimal to Seven-Segment                     | 92  |

|           |                | 11.1.3           | ASCII to Decimal                             | 93  |

|           |                |                  | Binary-Coded Decimal to Binary               | 94  |

|           |                |                  | Binary Number to ASCII String                | 95  |

|           | 11.2           |                  | ms                                           | 96  |

|           |                |                  | ASCII to Hexadecimal                         | 96  |

|           |                |                  | Seven-Segment to Decimal                     | 96  |

|           |                |                  | Decimal to ASCII                             | 96  |

|           |                |                  | Binary to Binary-Coded-Decimal               | 97  |

|           |                |                  | Packed Binary-Coded-Decimal to Binary String | 97  |

|           |                |                  | ASCII string to Binary number                | 97  |

|           |                |                  |                                              |     |

| <b>12</b> | Arit           | $\mathbf{hmeti}$ |                                              | 99  |

|           | 12.1           | Progra           | m Examples                                   | 99  |

|           |                | 12.1.2           | 64-Bit Addition                              | 99  |

|           |                | 12.1.3           | Decimal Addition                             | 100 |

|           |                | 12.1.4           | Multiplication                               | 101 |

|           |                | 12.1.5           | 32-Bit Binary Divide                         | 102 |

|           | 12.2           | Proble           | ms                                           | 103 |

|           |                | 12.2.1           | Multiple precision Binary subtraction        | 103 |

|           |                | 12.2.2           | Decimal Subtraction                          | 103 |

|           |                | 12.2.3           | 32-Bit by 32-Bit Multiply                    | 104 |

|           |                |                  |                                              |     |

| 13        |                | les and          |                                              | 105 |

|           | 13.1           |                  | 1                                            | 105 |

|           |                |                  | ·                                            | 105 |

|           |                |                  |                                              | 106 |

|           |                |                  | <b>~</b> ♥                                   | 107 |

|           |                |                  |                                              | 108 |

|           |                |                  | 0                                            | 109 |

|           | 13.2           |                  |                                              | 109 |

|           |                |                  | v                                            | 109 |

|           |                |                  | Add Entry to Ordered List                    |     |

|           |                |                  | Add Element to Queue                         |     |

|           |                |                  | 4-Byte Sort                                  |     |

|           |                | 13.2.5           | Using a Jump Table with a Key                | 110 |

| 11        | The            | Stack            |                                              | 111 |

| 14        | rne            | Stack            |                                              | 111 |

| 15        | Sub            | routin           | es                                           | 113 |

|           |                |                  |                                              | 113 |

|           |                |                  |                                              | 114 |

|           |                |                  |                                              | 114 |

|           |                |                  | <u> </u>                                     | 114 |

|           |                |                  |                                              | 115 |

|           |                |                  |                                              | 115 |

|           | 15.4           |                  | Of Parameters                                | 116 |

|           |                |                  | m Examples                                   | 116 |

|           |                | Proble           |                                              | 123 |

|           |                |                  |                                              | 123 |

|           |                |                  | ASCII Hex String to Binary Word              |     |

CONTENTS

|              | 15.6.3 Test for Alphabetic Character  | 123 |

|--------------|---------------------------------------|-----|

|              | 15.6.4 Scan to Next Non-alphabetic    | 123 |

|              | 15.6.5 Check Even Parity              | 124 |

|              | 15.6.6 Check the Checksum of a String | 124 |

|              | 15.6.7 Compare Two Counted Strings    |     |

| 16           | Interrupts and Exceptions             | 125 |

| $\mathbf{A}$ | ARM Instruction Definitions           | 127 |

|              | A.1 ADC: Add with Carry               | 127 |

|              | A.2 ADD: Add                          | 128 |

|              | A.3 AND: Bitwise AND                  | 128 |

|              | A.4 B, BL: Branch, Branch and Link    | 129 |

|              | A.5 CMP: Compare                      | 129 |

|              | A.6 EOR: Exclusive OR                 | 130 |

|              | A.7 LDM: Load Multiple                | 130 |

|              | A.8 LDR: Load Register                | 131 |

|              | A.9 LDRB: Load Register Byte          | 131 |

|              | A.10 MOV: Move                        | 131 |

|              | A.11 MVN: Move Negative               | 132 |

|              | A.12 ORR: Bitwise OR                  | 132 |

|              | A.13 SBC: Subtract with Carry         | 133 |

|              | A.14 STM: Store Multiple              | 133 |

|              | A.15 STR: Store Register              | 134 |

|              | A.16 STRB: Store Register Byte        | 134 |

|              | A.17 SUB: Subtract                    |     |

|              | A.18 SWI: Software Interrupt          |     |

|              | A.19 SWP: Swap                        | 136 |

|              | A.20 SWPB: Swap Byte                  |     |

| В            | ARM Instruction Summary               | 139 |

vi CONTENTS

# List of Programs

| $7.1 \\ 7.2$ | move16.s invert.s      | 16bit data transfer                                                      | 57<br>58 |

|--------------|------------------------|--------------------------------------------------------------------------|----------|

| 7.3a<br>7.3b | add.s<br>add2.s        | Add two numbers                                                          | 59<br>59 |

| 7.35         | shiftleft.s            | Shift Left one bit                                                       | 60       |

| 7.5          | nibble.s               | Disassemble a byte into its high and low order nibbles                   | 61       |

| 7.6          | bigger.s               | Find the larger of two numbers                                           | 62       |

| 7.7          | add64.s                | 64 bit addition                                                          | 63       |

| 7.8          | factorial.s            | Lookup the factorial from a table by using the address of the memory     | 06       |

|              | 14000114112            | location                                                                 | 64       |

| 8.7a         | bigger.s               | Find the larger of two numbers                                           | 69       |

|              | add64.s<br>factorial.s | 64 bit addition                                                          | 69       |

|              |                        | location                                                                 | 70       |

|              | sum16.s                | Add a series of 16 bit numbers by using a table address                  | 72       |

| 9.1b         | sum16b.s               | Add a series of 16 bit numbers by using a table address look-up          | 72       |

| 9.2a         | countneg.s             | Scan a series of 32 bit numbers to find how many are negative            | 73       |

| 9.2b         | countneg16.s           | Scan a series of 16 bit numbers to find how many are negative            | 74       |

| $9.3 \\ 9.4$ | largest16.s            | Scan a series of 16 bit numbers to find the largest                      | 75<br>75 |

| 9.4          | normalize.s            | Normalize a binary number                                                |          |

|              | strlencr.s             | Find the length of a Carage Return terminated string                     | 82       |

|              | strlen.s               | Find the length of a null terminated string                              | 83       |

|              | skipblanks.s           | Find first non-blank                                                     | 84       |

|              | padzeros.s             | Supress leading zeros in a string                                        | 84       |

| 10.4         | setparity.s            | Set the parity bit on a series of characters store the amended string in | O.E      |

| 10 50        |                        | Result                                                                   | 85<br>86 |

|              | cstrcmp.s<br>strcmp.s  | Compare null terminated strings for equality assume that we have no      | OU       |

| 10.00        | scremp.s               | knowledge of the data structure so we must assess the individual strings | 87       |

| 11.1a        | nibtohex.s             | Convert a single hex digit to its ASCII equivalent                       | 91       |

| 11.1b        | wordtohex.s            | Convert a 32 bit hexadecimal number to an ASCII string and output        |          |

|              |                        | to the terminal                                                          | 92       |

| 11.2         | nibtoseg.s             | Convert a decimal number to seven segment binary                         | 92       |

|              | dectonib.s             | Convert an ASCII numeric character to decimal                            | 93       |

|              | ubcdtohalf.s           | Convert an unpacked BCD number to binary                                 | 94       |

|              |                        | Convert an unpacked BCD number to binary using MUL                       | 94       |

| 6.11         | halftobin.s            | Store a 16bit binary number as an ASCII string of '0's and '1's          | 95       |

| 12.2         | add64.s                | 64 Bit Addition                                                          | 99       |

viii LIST OF PROGRAMS

| 12.3 addbcd.s                         | Add two packed BCD numbers to give a packed BCD result                                                                 | 100 |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|

| $12.4 \mathrm{a} \; \mathtt{mul16.s}$ | 16 bit binary multiplication                                                                                           | 101 |

| $12.4\mathrm{b}\mathrm{mul32.s}$      | Multiply two 32 bit number to give a 64 bit result (corrupts R0 and R1)                                                | 101 |

| 12.5 divide.s                         | Divide a 32 bit binary no by a 16 bit binary no store the quotient and remainder there is no 'DIV' instruction in ARM! | 102 |

| 13.1a insert.s                        | Examine a table for a match - store a new entry at the end if no match                                                 |     |

|                                       | found                                                                                                                  | 105 |

| $13.1\mathrm{b}$ insert2.s            | Examine a table for a match - store a new entry if no match found                                                      |     |

|                                       | extends insert.s                                                                                                       | 106 |

| 13.2 search.s                         | Examine an ordered table for a match                                                                                   | 106 |

| 13.3 head.s                           | Remove the first element of a queue                                                                                    | 107 |

| 13.4 sort.s                           | Sort a list of values – simple bubble sort                                                                             | 108 |

| 15.1a init1.s                         | Initiate a simple stack                                                                                                | 116 |

| $15.1\mathrm{b}\mathtt{init2.s}$      | Initiate a simple stack                                                                                                | 117 |

| 15.1c init3.s                         | Initiate a simple stack                                                                                                | 117 |

| $15.1\mathrm{d}$ init3a.s             | Initiate a simple stack                                                                                                | 118 |

| 15.1e byreg.s                         | A simple subroutine example program passes a variable to the routine                                                   |     |

|                                       | in a register                                                                                                          | 118 |

| 15.1f bystack.s                       | A more complex subroutine example program passes variables to the                                                      |     |

|                                       | routine using the stack                                                                                                | 119 |

| $15.1\mathrm{g}$ add $64.\mathrm{s}$  | A 64 bit addition subroutine                                                                                           | 121 |

| 15.1h factorial.s                     | A subroutine to find the factorial of a number                                                                         | 122 |

## **Preface**

Broadly speaking, you can divide the history of computers into four periods: the mainframe, the mini, the microprocessor, and the modern post-microprocessor. The *mainframe* era was characterized by computers that required large buildings and teams of technicians and operators to keep them going. More often than not, both academics and students had little direct contact with the mainframe—you handed a deck of punched cards to an operator and waited for the output to appear hours later. During the mainfame era, academics concentrated on languages and compilers, algorithms, and operating systems.

The minicomputer era put computers in the hands of students and academics, because university departments could now buy their own minis. As minicomputers were not as complex as mainframes and because students could get direct hands-on experience, many departments of computer science and electronic engineering taught students how to program in the native language of the computer—assembly language. In those days, the mid 1970s, assembly language programming was used to teach both the control of I/O devices, and the writing of programs (i.e., assembly language was taught rather like high level languages). The explosion of computer software had not taken place, and if you wanted software you had to write it yourself.

The late 1970s saw the introduction of the *microprocessor*. For the first time, each student was able to access a real computer. Unfortunately, microprocessors appeared before the introduction of low-cost memory (both primary and secondary). Students had to program microprocessors in assembly language because the only storage mechanism was often a ROM with just enough capacity to hold a simple single-pass assembler.

The advent of the low-cost microprocessor system (usually on a single board) ensured that virtually every student took a course on assembly language. Even today, most courses in computer science include a module on computer architecture and organization, and teaching students to write programs in assembly language forces them to understand the computer's architecture. However, some computer scientists who had been educated during the mainframe era were unhappy with the microprocessor, because they felt that the 8-bit microprocessor was a retrograde step—its architecture was far more primitive than the mainframes they had studied in the 1960s.

The 1990s is the *post-microprocessor* era. Today's personal computers have more power and storage capacity than many of yesterday's mainframes, and they have a range of powerful software tools that were undreamed of in the 1970s. Moreover, the computer science curriculum of the 1990s has exploded. In 1970 a student could be expected to be familiar with all field of computer science. Today, a student can be expected only to browse through the highlights.

The availability of high-performance hardware and the drive to include more and more new material in the curriculum, has put pressure on academics to justify what they teach. In particular, many are questioning the need for courses on assembly language.

If you regard computer science as being primarily concerned with the *use* of the computer, you can argue that assembly language is an irrelevance. Does the surgeon study metallurgy in order to understand how a scalpel operates? Does the pilot study thermodynamics to understand how a jet engine operates? Does the news reader study electronics to understand how the camera

x PREFACE

operates? The answer to all these questions is "no". So why should we inflict assembly language and computer architecture on the student?

First, education is not the same as training. The student of computer science is not simply being trained to use a number of computer packages. A university course leading to a degree should also cover the history and the theoretical basis for the subject. Without a knowledge of computer architecture, the computer scientist cannot understand how computers have developed and what they are capable of.

#### Is assembly language today the same as assembly language yesterday?

Two factors have influenced the way in which we teach assembly language—one is the way in which microprocessors have changed, and the other is the use to which assembly language teaching is put. Over the years microprocessors have become more and more complex, with the result that the architecture and assembly language of a modern state-of-the-art microprocessor is radically different to that of an 8-bit machine of the late 1970s. When we first taught assembly language in the 1970s and early 1980s, we did it to demonstrate how computers operated and to give students hands-on experience of a computer. Since all students either have their own computer or have access to a computer lab, this role of the single-board computer is now obsolete. Moreover, assembly language programming once attempted to ape high-level language programming— students were taught algorithms such as sorting and searching in assembly language, as if assembly language were no more than the (desperately) poor person's C.

The argument for teaching assembly language programming today can be divided into two components: the underpinning of computer architecture and the underpinning of computer software.

Assembly language teaches how a computer works at the machine (i.e., register) level. It is therefore necessary to teach assembly language to all those who might later be involved in computer architecture—either by specifying computers for a particular application, or by designing new architectures. Moreover, the von Neumann machine's sequential nature teaches students the limitation of conventional architectures and, indirectly, leads them on to unconventional architectures (parallel processors, Harvard architectures, data flow computers, and even neural networks).

It is probably in the realm of software that you can most easily build a case for the teaching of assembly language. During a student's career, he or she will encounter a lot of abstract concepts in subjects ranging from programming languages, to operating systems, to real-time programming, to AI. The foundation of many of these concepts lies in assembly language programming and computer architecture. You might even say that assembly language provides bottom-up support for the top-down methodology we teach in high-level languages. Consider some of the following examples (taken from the teaching of Advanced RISC Machines Ltd (ARM) assembly language).

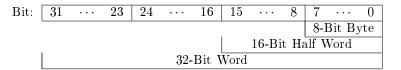

#### Data types

Students come across data types in high-level languages and the effects of strong and weak data typing. Teaching an assembly language that can operate on bit, byte, word and long word operands helps students understand data types. Moreover, the ability to perform any type of assembly language operation on any type of data structure demonstrates the need for strong typing.

#### Addressing modes

A vital component of assembly language teaching is addressing modes (literal, direct, and indirect). The student learns how pointers function and how pointers are manipulated. This aspect is particularly important if the student is to become a C programmer. Because an assembly language is unencumbered by data types, the students' view of pointers is much simplified by an assembly language. The ARM has complex addressing modes that support direct and indirect addressing, generated jump tables and handling of unknown memory offsets.

*PREFACE* xi

#### The stack and subroutines

How procedures are called, and parameters passed and returned from procedures. By using an assembly language you can readily teach the passing of parameters by *value* and by *reference*. The use of *local variables* and *re-entrant* programming can also be taught. This supports the teaching of task switching kernels in both operating systems and real-time programming.

#### Recursion

The recursive calling of subroutines often causes a student problems. You can use an assembly language, together with a suitable system with a tracing facility, to demonstrate how recursion operates. The student can actually observe how the stack grows as procedures are called.

#### Run-time support for high-level languages

A high-performance processor like the ARM provides facilities that support run-time checking in high-level languages. For example, the programming techniques document lists a series of programs that interface with 'C' and provide run-time checking for errors such as an attempt to divide a number by zero.

#### Protected-mode operation

Members of the ARM family operate in either a *priviledge mode* or a *user mode*. The operating system operates in the priviledge mode and all user (applications) programs run in the user mode. This mechanism can be used to construct *secure* or *protected* environments in which the effects of an error in one application can be prevented from harming the operating system (or other applications).

#### Input-output

Many high-level languages make it difficult to access I/O ports and devices directly. By using an assembly language we can teach students how to write device drivers and how to control interfaces. Most real interfaces are still programmed at the machine level by accessing registers within them.

All these topics can, of course, be taught in the appropriate courses (e.g., high-level languages, operating systems). However, by teaching them in an assembly language course, they pave the way for future studies, and also show the student exactly what is happening within the machine.

#### Conclusion

A strong case can be made for the continued teaching of assembly language within the computer science curriculum. However, an assembly language cannot be taught just as if it were another general-purpose programming language as it was once taught ten years ago. Perhaps more than any other component of the computer science curriculum, teaching an assembly language supports a wide range of topics at the heart of computer science. An assembly language should not be used just to illustrate algorithms, but to demonstrate what is actually happening inside the computer.

xii PREFACE

# 1 Introduction

A computer program is ultimately a series of numbers and therefore has very little meaning to a human being. In this chapter we will discuss the levels of human-like language in which a computer program may be expressed. We will also discuss the reasons for and uses of assembly language.

### 1.1 The Meaning of Instructions

The instruction set of a microprocessor is the set of binary inputs that produce defined actions during an instruction cycle. An instruction set is to a microprocessor what a function table is to a logic device such as a gate, adder, or shift register. Of course, the actions that the microprocessor performs in response to its instruction inputs are far more complex than the actions that logic devices perform in response to their inputs.

#### 1.1.1 Binary Instructions

An instruction is a binary digit pattern — it must be available at the data inputs to the microprocessor at the proper time in order to be interpreted as an instruction. For example, when the ARM receives the binary pattern 11100000100 as the input during an instruction fetch operation, the pattern means subtract. Similarly the microinstruction 111000001000 means add. Thus the 32 bit pattern 11100000010011101100000000001111 means:

"Subtract R15 from R14 and put the answer in R12."

The microprocessor (like any other computer) only recognises binary patterns as instructions or data; it does not recognise characters or octal, decimal, or hexadecimal numbers.

## 1.2 A Computer Program

A program is a series of instructions that causes a computer to perform a particular task.

Actually, a computer program includes more than instructions, it also contains the data and the memory addresses that the microprocessor needs to accomplish the tasks defined by the instructions. Clearly, if the microprocessor is to perform an addition, it must have two numbers to add and a place to put the result. The computer program must determine the sources of the data and the destination of the result as well as the operation to be performed.

All microprocessors execute instructions sequentially unless an instruction changes the order of execution or halts the processor. That is, the processor gets its next instruction from the next higher memory address unless the current instruction specifically directs it to do otherwise.

Ultimately, every program is a set of binary numbers. For example, this is a snippet of an ARM program that adds the contents of memory locations  $8094_{32}$  and  $8098_{32}$  and places the result in memory location  $809C_{32}$ :

This is a machine language, or object, program. If this program were entered into the memory of an ARM-based microcomputer, the microcomputer would be able to execute it directly.

## 1.3 The Binary Programming Problem

There are many difficulties associated with creating programs as object, or binary machine language, programs. These are some of the problems:

- The programs are difficult to understand or debug. (Binary numbers all look the same, particularly after you have looked at them for a few hours.)

- The programs do not describe the task which you want the computer to perform in anything resembling a human-readable format.

- The programs are long and tiresome to write.

- The programmer often makes careless errors that are very difficult to locate and correct.

For example, the following version of the addition object program contains a single bit error. Try to find it:

Although the computer handles binary numbers with ease, people do not. People find binary programs long, tiresome, confusing, and meaningless. Eventually, a programmer may start remembering some of the binary codes, but such effort should be spent more productively.

## 1.4 Using Octal or Hexadecimal

We can improve the situation somewhat by writing instructions using octal or hexadecimal numbers, rather than binary. We will use hexadecimal numbers because they are shorter, and because they are the standard for the microprocessor industry. Table 1.1 defines the hexadecimal digits and their binary equivalents. The ARM program to add two numbers now becomes:

E59F1010 E59f0008 E0815000 E58F5008

At the very least, the hexadecimal version is shorter to write and not quite so tiring to examine.

Errors are somewhat easier to find in a sequence of hexadecimal digits. The erroneous version of the addition program, in hexadecimal form, becomes:

| Hexadecimal | Binary     | Decimal    |

|-------------|------------|------------|

| Digit       | Equivalent | Equivalent |

| 0           | 0000       | 0          |

| 1           | 0001       | 1          |

| 2           | 0010       | 2          |

| 3           | 0011       | 3          |

| 4           | 0100       | 4          |

| 5           | 0101       | 5          |

| 6           | 0110       | 6          |

| 7           | 0111       | 7          |

| 8           | 1000       | 8          |

| 9           | 1001       | 9          |

| A           | 1010       | 10         |

| В           | 1011       | 11         |

| C           | 1100       | 12         |

| D           | 1101       | 13         |

| E           | 1110       | 14         |

| F           | 1111       | 15         |

Table 1.1: Hexadecimal Conversion Table

E59F1010 E59f0008 E0815000 E68F5008

The mistake is far more obvious.

The hexadecimal version of the program is still difficult to read or understand; for example, it does not distinguish operations from data or addresses, nor does the program listing provide any suggestion as to what the program does. What does 3038 or 31C0 mean? Memorising a card full of codes is hardly an appetising proposition. Furthermore, the codes will be entirely different for a different microprocessor and the program will require a large amount of documentation.

#### 1.5 Instruction Code Mnemonics

An obvious programming improvement is to assign a name to each instruction code. The instruction code name is called a "mnemonic" or memory jogger.

In fact, all microprocessor manufacturers provide a set of mnemonics for the microprocessor instruction set (they cannot remember hexadecimal codes either). You do not have to abide by the manufacturer's mnemonics; there is nothing sacred about them. However, they are standard for a given microprocessor, and therefore understood by all users. These are the instruction codes that you will find in manuals, cards, books, articles, and programs. The problem with selecting instruction mnemonics is that not all instructions have "obvious" names. Some instructions do (for example, ADD, AND, ORR), others have obvious contractions (such as SUB for subtraction, EOR for exclusive-OR), while still others have neither. The result is such mnemonics as BIC, STMIA, and even MRS. Most manufacturers come up with some reasonable names and some hopeless ones. However, users who devise their own mnemonics rarely do much better.

Along with the instruction mnemonics, the manufacturer will usually assign names to the CPU registers. As with the instruction names, some register names are obvious (such as A for Accumulator) while others may have only historical significance. Again, we will use the manufacturer's suggestions simply to promote standardisation.

If we use standard ARM instruction and register mnemonics, as defined by Advanced RISC Machines, our ARM addition program becomes:

```

LDR R1, num1

LDR R0, num2

ADD R5, R1, R0

STR R5, num3

```

The program is still far from obvious, but at least some parts are comprehensible. ADD is a considerable improvement over E59F. The LDR mnemonic does suggest loading data into a register or memory location. We now see that some parts of the program are operations and others are addresses. Such a program is an assembly language program.

## 1.6 The Assembler Program

How do we get the assembly language program into the computer? We have to translate it, either into hexadecimal or into binary numbers. You can translate an assembly language program by hand, instruction by instruction. This is called hand assembly.

The following table illustrates the hand assembly of the addition program:

| Instruction Mnemonic | Register/Memory Location | Hexadecimal Equivalent |

|----------------------|--------------------------|------------------------|

| LDR                  | R1, num1                 | E59F1010               |

| LDR                  | RO, num2                 | E59F0008               |

| ADD                  | R5, R1, R0               | E0815000               |

| STR                  | R5, num3                 | E58F5008               |

Hand assembly is a rote task which is uninteresting, repetitive, and subject to numerous minor errors. Picking the wrong line, transposing digits, omitting instructions, and misreading the codes are only a few of the mistakes that you may make. Most microprocessors complicate the task even further by having instructions with different lengths. Some instructions are one word long while others may be two or three. Some instructions require data in the second and third words; others require memory addresses, register numbers, or who knows what?

Assembly is a rote task that we can assign to the microcomputer. The microcomputer never makes any mistakes when translating codes; it always knows how many words and what format each instruction requires. The program that does this job is an "assembler." The assembler program translates a user program, or "source" program written with mnemonics, into a machine language program, or "object" program, which the microcomputer can execute. The assembler's input is a source program and its output is an object program.

Assemblers have their own rules that you must learn. These include the use of certain markers (such as spaces, commas, semicolons, or colons) in appropriate places, correct spelling, the proper control of information, and perhaps even the correct placement of names and numbers. These rules are usually simple and can be learned quickly.

#### 1.6.1 Additional Features of Assemblers

Early assemblers did little more than translate the mnemonic names of instructions and registers into their binary equivalents. However, most assemblers now provide such additional features as:

- Allowing the user to assign names to memory locations, input and output devices, and even sequences of instructions

- Converting data or addresses from various number systems (for example, decimal or hexadecimal) to binary and converting characters into their ASCII or EBCDIC binary codes

- Performing some arithmetic as part of the assembly process

- Telling the loader program where in memory parts of the program or data should be placed

- Allowing the user to assign areas of memory as temporary data storage and to place fixed data in areas of program memory

- Providing the information required to include standard programs from program libraries, or programs written at some other time, in the current program

- Allowing the user to control the format of the program listing and the input and output devices employed

#### 1.6.2 Choosing an Assembler

All of these features, of course, involve additional cost and memory. Microcomputers generally have much simpler assemblers than do larger computers, but the tendency is always for the size of assemblers to increase. You will often have a choice of assemblers. The important criterion is not how many off-beat features the assembler has, but rather how convenient it is to use in normal practice.

## 1.7 Disadvantages of Assembly Language

The assembler does not solve all the problems of programming. One problem is the tremendous gap between the microcomputer instruction set and the tasks which the microcomputer is to perform. Computer instructions tend to do things like add the contents of two registers, shift the contents of the Accumulator one bit, or place a new value in the Program Counter. On the other hand, a user generally wants a microcomputer to do something like print a number, look for and react to a particular command from a teletypewriter, or activate a relay at the proper time. An assembly language programmer must translate such tasks into a sequence of simple computer instructions. The translation can be a difficult, time-consuming job.

Furthermore, if you are programming in assembly language, you must have detailed knowledge of the particular microcomputer that you are using. You must know what registers and instructions the microcomputers has, precisely how the instructions affect the various registers, what addressing methods the computer uses, and a mass of other information. None of this information is relevant to the task which the microcomputer must ultimately perform.

In addition, assembly language programs are not portable. Each microcomputer has its own assembly language which reflects its own architecture. An assembly language program written for the ARM will not run on a 486, Pentium, or Z8000 microprocessor. For example, the addition program written for the Z8000 would be:

LD R0,%6000 ADD R0,%6002 LD %6004,R0

The lack of portability not only means that you will not be able to use your assembly language program on a different microcomputer, but also that you will not be able to use any programs that were not specifically written for the microcomputer you are using. This is a particular drawback for new microcomputers, since few assembly language programs exist for them. The result, too frequently, is that you are on your own. If you need a program to perform a particular task, you are not likely to find it in the small program libraries that most manufacturers provide. Nor are you likely to find it in an archive, journal article, or someone's old program File. You will probably have to write it yourself.

## 1.8 High-Level Languages

The solution to many of the difficulties associated with assembly language programs is to use, insted, high-level or procedure-oriented languages. Such languages allow you to describe tasks in forms that are problem-oriented rather than computer-oriented. Each statement in a high-level language performs a recognisable function; it will generally correspond to many assembly language instruction. A program called a compiler translates the high-level language source program into object code or machine language instructions.

Many different hgih-level languages exist for different types of tasks. If, for exampe, you can express what you want the computer to do in algebraic notation, you can write your FORTRAN (Formula Translation Language), the oldest of the high-level languages. Now, if you want to add two numbers, you just tell the computer:

```

sum = num1 + num2;

```

That is a lot simpler (and shorter) than either the equivalent machine language program or the equivalent assembly language program. Other high-level languages include COBOL (for business applications), BASIC (a cut down version of FORTRAN designed to prototype ideas before codeing them in full), C (a systems-programming language), C++ and JAVA (object-orientated general development languages).

#### 1.8.1 Advantages of High-Level Languages

Clearly, high-level languages make program easier and faster to write. A common estimate is that a programmer can write a program about ten times as fast in a high-level language as in assembly language. That is just writing the program; it does not include problem definition, program design, debugging testing or documentation, all of which become simpler and faster. The high-level language program is, for instance, partly self-documenting. Even if you do not know FORTRAN, you could probably tell what the statement illustrated above does.

#### Machine Independence

High-level languages solve many other problems associated with assembly language programming. The high-level language has its own syntax (usually defined by an international standard). The language does not mention the instruction set, registers, or other features of a particular computer. The compiler takes care of all such details. Programmers can concentrate on their own tasks; they do not need a detailed understanding of the underlying CPU architecture — for that matter, they do not need to know anything about the computer the are programming.

#### Portability

Programs written in a high-level language are portable — at least, in theory. They will run on any computer that has a standard compiler for that language.

At the same time, all previous programs written in a high-level language for prior computers and available to you when programming a new computer. This can mean thousands of programs in the case of a common language like  ${\sf C}$ .

#### 1.8.2 Disadvantages of High-Level Languages

If all the good things we have said about high-level languages are true — if you can write programs faster and make them portable besides — why bother with assebly languages? Who wants to worry about registers, instruction codes, mnemonics, and all that garbage! As usual, there are disadvantages that balance the advantages.

#### **Syntax**

One obvious problem is that, as with assembly language, you have to learn the "rules" or *syntax* of any high-level language you want to use. A high-level language has a fairly complicated set of rules. You will find that it takes a lot of time just to get a program that is syntactically correct (and even then it probably will not do what you want). A high-level computer language is like a foreign language. If you have talent, you will get used to the rules and be able to turn out programs that the compiler will accept. Still, learning the rules and trying to get the program accepted by the compiler does not contribute directly to doing your job.

#### Cost of Compilers

Another obvious problem is that you need a compiler to translate program written in a high-level language into machine language. Compilers are expensive and use a large amount of memory. While most assemblers occupy only a few KBytes of memory, compilers would occupy far larger amounts of memory. A compiler could easily require over four times as much memory as an assembler. So the amount of overhead involved in using the compiler is rather large.

#### Adapting Tasks to a Language

Furthermore, only some compilers will make the implementation of your task simpler. Each language has its own target proglem area, for example, FORTRAN is well-suited to problems that can be expressed as algebraic formulas. If however, your problem is controlling a display terminal, editing a string of characters, or monitoring an alarm system, your problem cannot be easily expressed. In fact, formulating the solution in FORTRAN may be more awkward and more difficult than formulating it in assembly language. The answer is, of course, to use a more suitable high-level language. Languages specifically designed for tasks such as those mentioned above do exist — they are called system implementation languages. However, these languages are less widely used.

#### Inefficiency

High-level languages do not produce very efficient machine language program. The basic reason for this is that compilation is an automatic process which is riddled with compromises to allow for many ranges of possibilities. The compiler works much like a computerised language translator — sometimes the words are right but the sentence structures are awkward. A simpler compiler connot know when a variable is no longer being used and can be discarded, when a register should be used rather than a memory location, or when variables have simple relationships. The experienced programmer can take advantage of shortcuts to shorten execution time or reduce memory usage. A few compiler (known as optimizing cmpilers) can also do this, but such compilers are much larger than regular compilers.

#### 1.9 Which Level Should You Use?

Which language level you use depends on your particular application. Let us briefly note some of the factors which may favor particular levels:

#### 1.9.1 Applications for Machine Language

Virtually no one programs in machine language because it wastes human time and is difficult to document. An assembler costs very little and greatly reduces programming time.

#### 1.9.2 Applications for Assembly Language

- Limited data processing

- High-volume applications

- Real-Time control applications

- Short to moderate-sized programs

- Application where memory cost is a factor

- Applications involving more input/output or control than computation

### 1.9.3 Applications for High-Level Language

- Long programs

- Low-volume applications

- Programs which are expected to undergo many changes

- Compatibility with similar applications using larger computers

- Applications involing more computation than input/output or control

- Applications where the amout of memory required is already very large

- Availability of a specific program in a high-level language which can be used in the application.

#### 1.9.4 Other Considerations

Many other factors are also important, such as the availability of a large computer for use in development, experience with particular languages, and compatibility with other applications.

If hardware will ultimately be the largest cost in your application, or if speed is critical, you should favor assembly language. But be prepared to spend much extra time in software development in exchange for lower memory costs and higher execution speeds. If software will be the largest cost in your application, you should favor a high-level language. But be prepared to spend the extra money required for the supporting hardware and software.

Of course, no one except some theorists will object if you use both assembly and high-level languages. You can write the program originally in a high-level language and then patch some sections in assembly language. However, most users prefer not to do this because it can create havoc in debugging, testing, and documentation.

## 1.10 Why Learn Assembler?

Given the advance of high-level languages, why do you need to learn assembly language programming? The reasons are:

- 1. Most industrial microcomputer users program in assembly language.

- 2. Many microcomputer users will continue to program in assembly language since they need the detailed control that it provides.

- 3. No suitable high-level language has yet become widely available or standardised.

- 4. Many application require the efficiency of assembly language.

- 5. An understanding of assembly language can help in evaluating high-level languages.

- 6. Almost all microcomputer programmers ultimately find that they need some knowledge of assembly language, most often to debug programs, write I/O routines, speed up or shorten critical sections of programs written in high-level languages, utilize or modify operating system functions, and undertand other people's programs.

The rest of these notes will deal exclusively with assembler and assembly language programming.

# 2 Assemblers

This chapter discusses the functions performed by assemblers, beginning with features common to most assemblers and proceeding through more elaborate capabilities such as macros and conditional assembly. You may wish to skim this chapter for the present and return to it when you feel more comfortable with the material.

As we mentioned, today's assemblers do much more than translate assembly language mnemonics into binary codes. But we will describe how an assembler handles the translation of mnemonics before describing additional assembler features. Finally we will explain how assemblers are used.

#### 2.1 Fields

Assembly language instructions (or "statements") are divided into a number of "fields".

The operation code field is the only field which can never he empty; it always contains either an instruction mnemonic or a directive to the assembler, sometimes called a "pseudo-instruction," "pseudo-operation," or "pseudo-ope."

The operand or address field may contain an address or data, or it may be blank.

The comment and label fields are optional. A programmer will assign a label to a statement or add a comment as a personal convenience: namely, to make the program easier to read and use.

Of course, the assembler must have some way of telling where one field ends and another begins. Assemblers often require that each field start in a specific column. This is a "fixed format." However, fixed formats are inconvenient when the input medium is paper tape; fixed formats are also a nuisance to programmers. The alternative is a "free format" where the fields may appear anywhere on the line.

#### 2.1.1 Delimiters

If the assembler cannot use the position on the line to tell the fields apart, it must use something else. Most assemblers use a special symbol or "delimiter" at the beginning or end of each field.

| Label<br>Field | Operation Code<br>or Mnemonic<br>Field | Operand or<br>Address<br>Field | Comment Field                       |

|----------------|----------------------------------------|--------------------------------|-------------------------------------|

| VALUE1         | DCW                                    | 0x201E                         | ;FIRST VALUE                        |

| VALUE2         | DCW                                    | 0x0774                         | ;SECOND VALUE                       |

| RESULT         | DCW                                    | 1                              | ;16-BIT STORAGE FOR ADDITION RESULT |

| START          | MOV                                    | RO, VALUE1                     | GET FIRST VALUE                     |

|                | ADD                                    | RO, RO, VALUE2                 | ; ADD SECOND VALUE TO FIRST VALUE   |

|                | STR                                    | RESULT, RO                     | STORE RESULT OF ADDITION            |

| NEXT:          | ?                                      | ?                              | ; NEXT INSTRUCTION                  |

label  $\langle whitespace \rangle$  instruction  $\langle whitespace \rangle$ ; comment

whitespace Between label and operation code, between operation code and ad-

dress, and before an entry in the comment field

comma Between operands in the address field asterisk Before an entire line of comment

semicolon Marks the start of a comment on a line that contains preceding code

Table 2.1: Standard ARM Assembler Delimiters

The most common delimiter is the space character. Commas, periods, semicolons, colons, slashes, question marks, and other characters that would not otherwise be used in assembly language programs also may serve as delimiters. The general form of layout for the ARM assembler is:

You will have to exercise a little care with delimiters. Some assemblers are fussy about extra spaces or the appearance of delimiters in comments or labels. A well-written assembler will handle these minor problems, but many assemblers are not well-written. Our recommendation is simple: avoid potential problems if you can. The following rules will help:

- Do not use extra spaces, in particular, do not put spaces after commas that separate operands, even though the ARM assembler allows you to do this.

- Do not use delimiter characters in names or labels.

- Include standard delimiters even if your assembler does not require them. Then it will be more likely that your programs are in correct form for another assembler.

#### 2.1.2 Labels

The label field is the first field in an assembly language instruction; it may be blank. If a label is present, the assembler defines the label as equivalent to the address into which the first byte of the object code generated for that instruction will be loaded. You may subsequently use the label as an address or as data in another instruction's address field. The assembler will replace the label with the assigned value when creating an object program.

The ARM assembler requires labels to start at the first character of a line. However, some other assemblers also allow you to have the label start anywhere along a line, in which case you must use a colon (:) as the delimiter to terminate the label field. Colon delimiters are not used by the ARM assembler.

Labels are most frequently used in Branch or SWI instructions. These instructions place a new value in the program counter and so alter the normal sequential execution of instructions. B  $150_{16}$  means "place the value  $150_{16}$  in the program counter." The next instruction to be executed will be the one in memory location  $150_{16}$ . The instruction B START means "place the value assigned to the label START in the program counter." The next instruction to be executed will be the on at the address corresponding to the label START. Figure 2.1 contains an example.

Why use a label? Here are some reasons:

- A label makes a program location easier to find and remember.

- The label can easily be moved, if required, to change or correct a program. The assembler will automatically change all instructions that use the label when the program is reassembled.

2.1. FIELDS 13

Assembly language Program

When the machine language version of this program is executed, the instruction B START causes the address of the instruction labeled START to be placed in the program counter That instruction will then be executed.

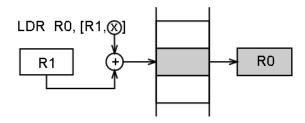

Figure 2.1: Assigning and Using a Label